### Order Number 9114332

## Performance observability

Malony, Allen Davis, Ph.D.

University of Illinois at Urbana-Champaign, 1990

This is an authorized facsimile, made from the microfilm master copy of the original dissertation or master thesis published by UMI.

The bibliographic information for this thesis is contained in UMI's Dissertation Abstracts database, the only central source for accessing almost every doctoral dissertation accepted in North America since 1861.

300 North Zeeb Road P.O. Box 1346 Ann Arbor, Michigan 48106-1346 USA

800.521.0600 734.761.4700 web www.il.proquest.com

Printed in 2003 by digital xerographic process on acid-free paper

|   | • |  |  |

|---|---|--|--|

| • |   |  |  |

| · |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

#### **INFORMATION TO USERS**

The most advanced technology has been used to photograph and reproduce this manuscript from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

**UM**I

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

## PERFORMANCE OBSERVABILITY

## $\mathbf{BY}$

### ALLEN DAVIS MALONY

B.S., University of California, 1980 M.S., University of California, 1982

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1990

Urbana, Illinois

### UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

### THE GRADUATE COLLEGE

|                      |                                                    | SEPTEMBER 1990              |

|----------------------|----------------------------------------------------|-----------------------------|

|                      |                                                    |                             |

| WE HEREBY            | RECOMMEND THAT THE                                 | THESIS BY                   |

|                      | ALLEN DAVIS MALONY                                 |                             |

| ENTITLED             | PERFORMANCE OBSERVAL                               | BILITY                      |

| BE ACCEPTED IN       | PARTIAL FULFILLMENT                                | OF THE REQUIREMENTS FOR     |

| THE DEGREE OF_       | DOCTOR OF PHILOSOPHY                               | Sail V. Rel                 |

| _                    |                                                    | Director of Thesis Research |

|                      |                                                    | Head of Department          |

| Committee on Final E | Chairperson  Chairperson  Chairperson  Chairperson |                             |

† Required for doctor's degree but not for master's.

#### PERFORMANCE OBSERVABILITY

Allen Davis Malony, Ph.D.

Department of Computer Science

University of Illinois at Urbana-Champaign, 1990

D. Reed, Advisor

Performance observability is the ability to accurately capture, analyze, and present (collectively observe) information about the performance of a computer system. Advances in computer systems design, particularly with respect to parallel processing and supercomputers, have brought a crisis in performance observation — computer systems technology is outpacing the tools to understand the performance behavior of and to operate the machines near the high-end of their performance range. In this thesis, we study the performance observability problem with emphasis on the practical design, development, and use of tools for performance measurement, analysis, and visualization.

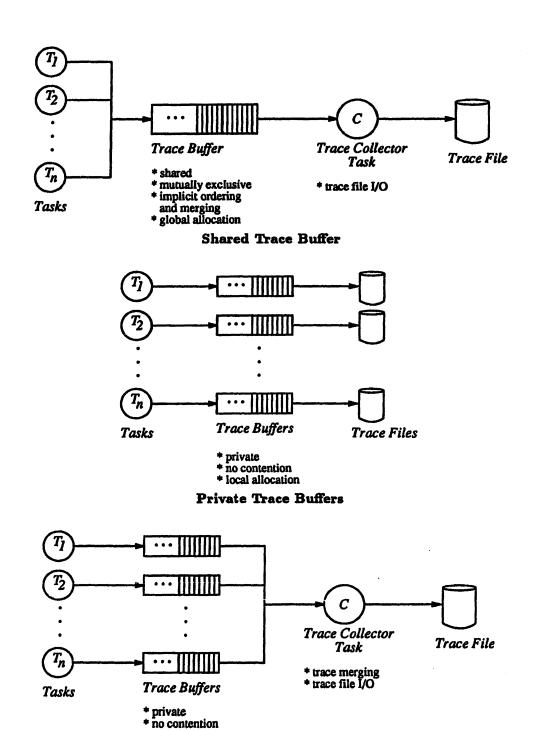

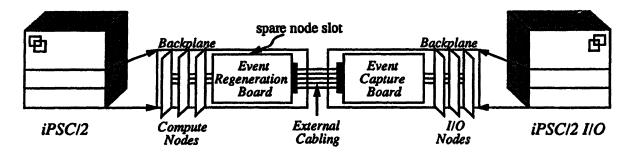

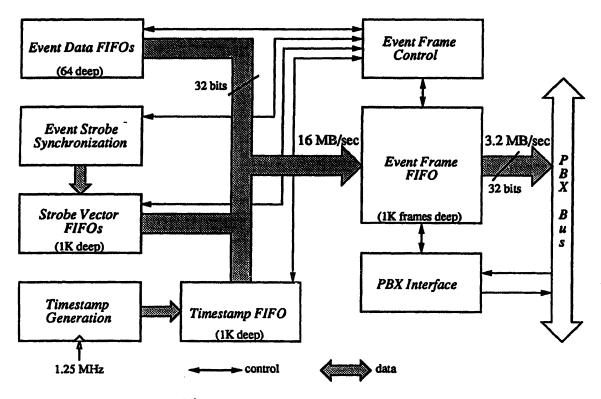

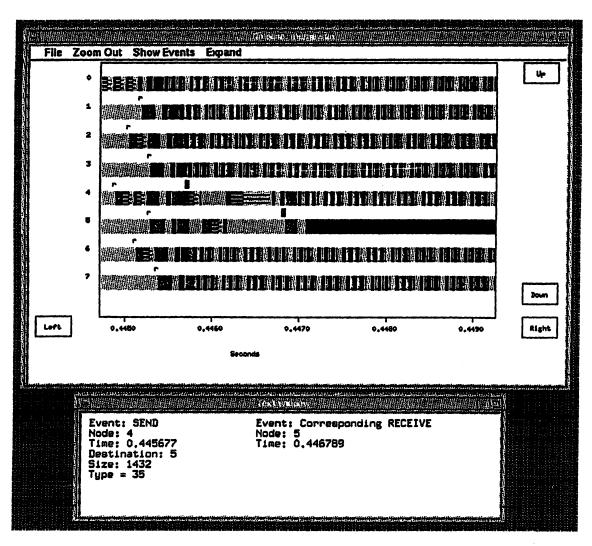

Tools for performance observability must balance the need for performance data against the cost of obtaining it (environment complexity and performance intrusion) – too little performance data makes performance analysis difficult; too much data perturbs the measured system. We discuss several methods for performance measurement concentrating specifically on mechanisms for timing and tracing. We show how minor hardware and software modifications can enable better measurement tools to be built and describe results from a prototype hardware-based software monitor developed for the Intel iPSC/2 multiprocessor.

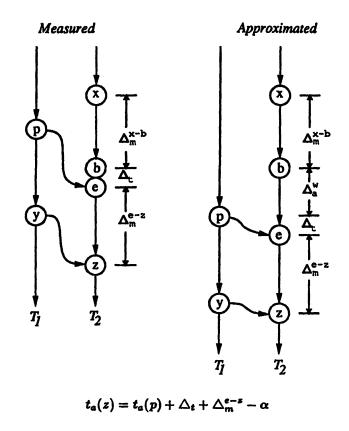

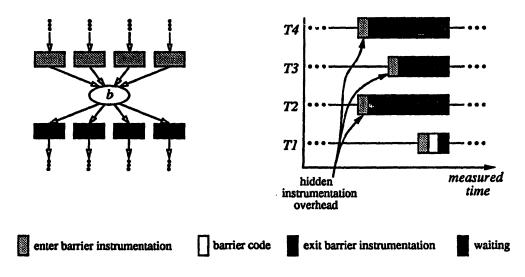

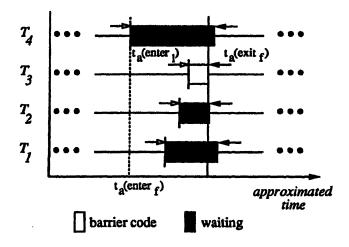

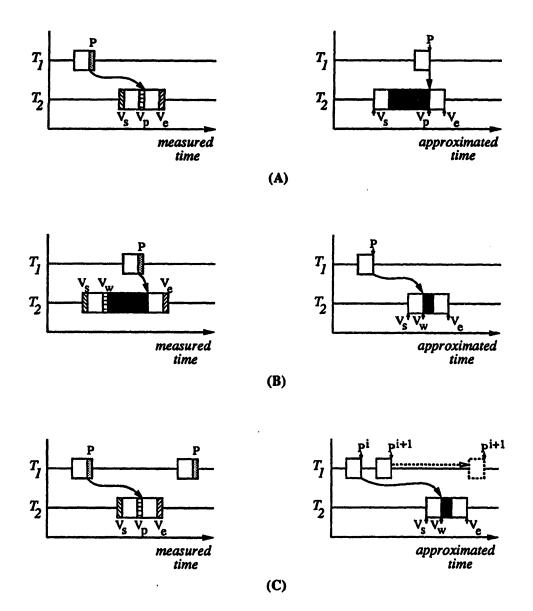

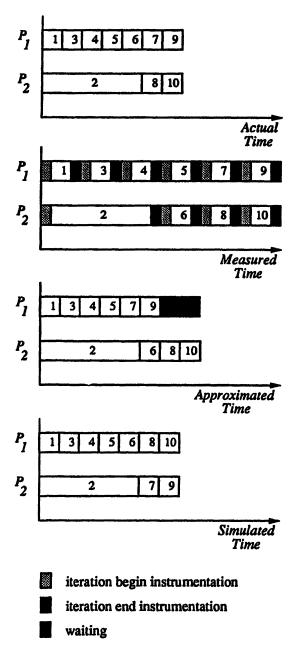

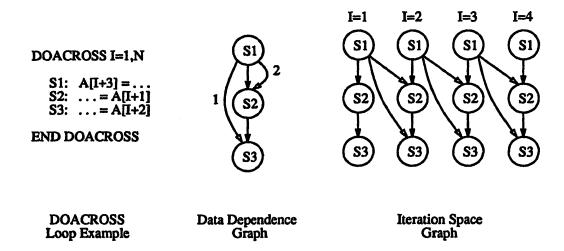

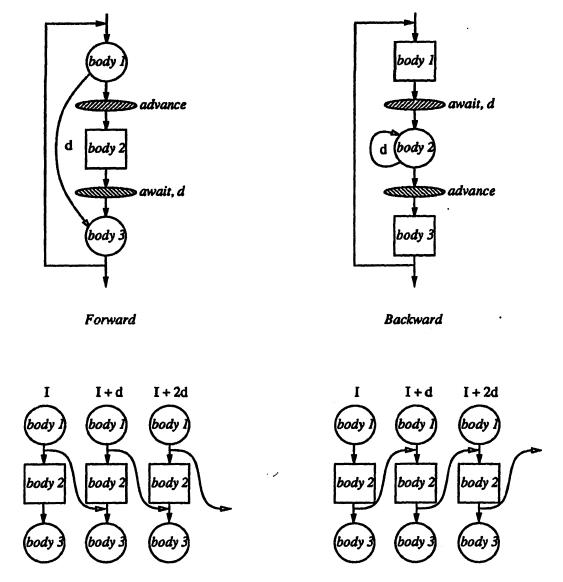

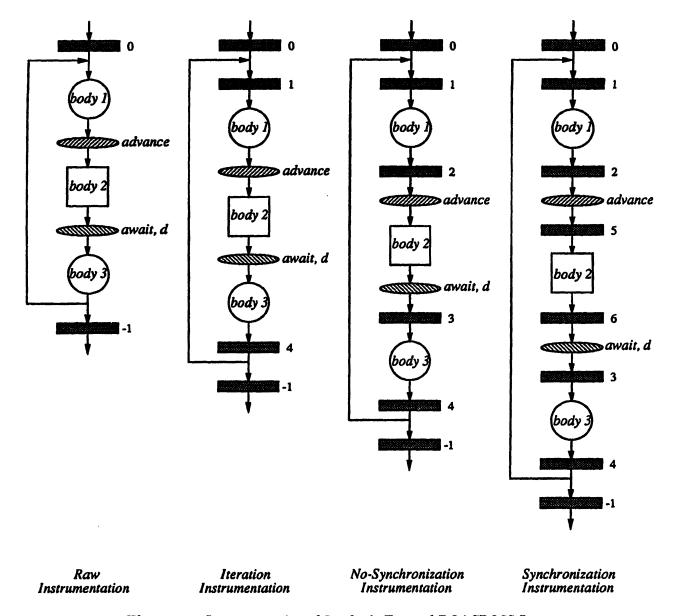

Any software performance measurement perturbs the measured system. We develop two models of performance perturbation to understand the effects of instrumentation intrusion: time-based and event-based. The time-based models use only measured time overheads of instrumentation to approximate actual execution time performance. We show that this model can give accurate approximations for sequential execution and for parallel execution with independent execution ordering. We use the event-based model to quantify the perturbation effects of instrumentations of parallel executions with ordering dependencies. Our results show that this model can be applied in practice to achieve accurate approximations. We also discuss the limitations of the time-based and event-based models.

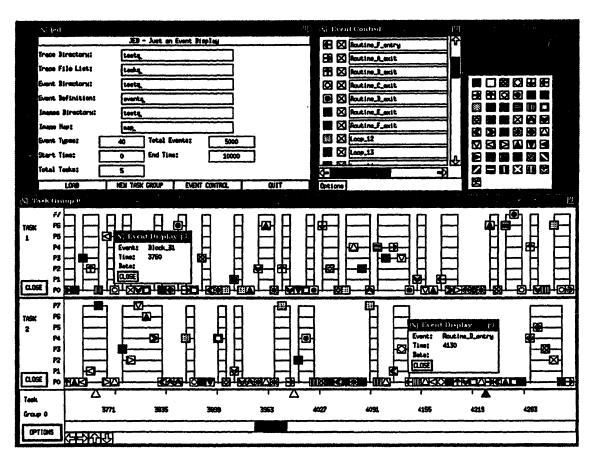

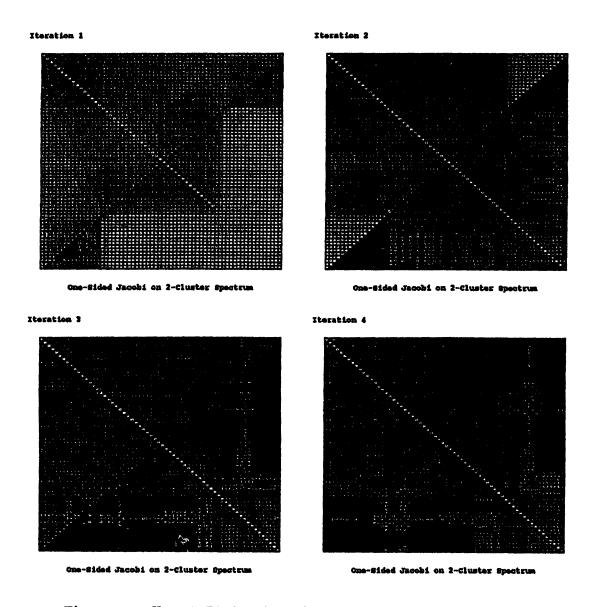

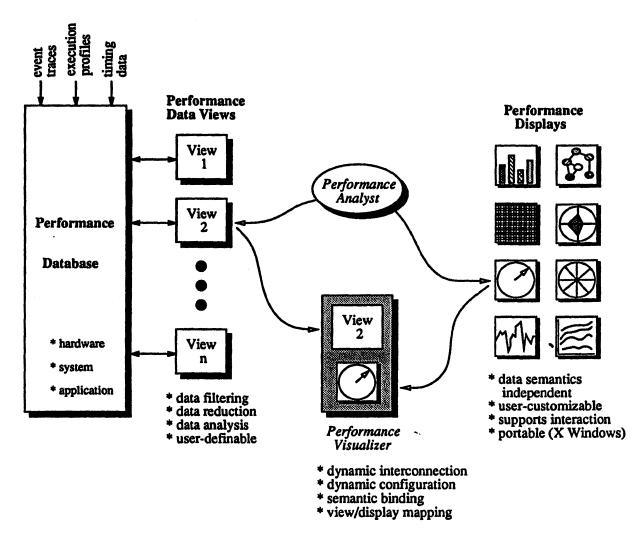

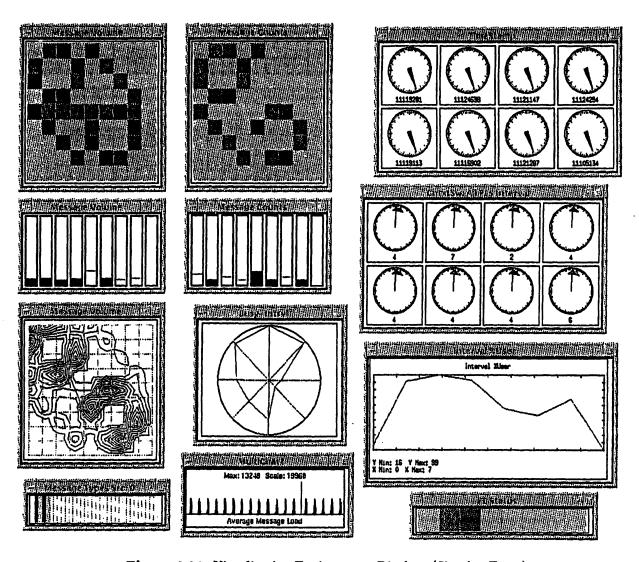

The potentially large volume of detailed performance data requires new approaches to presentation that can show both gross performance characteristics while allowing users to focus on local performance behavior. We give several examples where performance visualization techniques have been effectively applied, plus discuss the architecture and a prototype of a general performance visualization environment.

Finally, we apply several of the performance measurement, analysis, and visualization techniques to a practical study of performance observability on the Cray X-MP and Cray 2 supercomputers. Our results show that even modest improvements in the existing set of performance tools for a particular machine can have significant benefits in performance evaluation capabilities.

To my Father, my Mother, Kimberly, and Lindsay

### Acknowledgments

The journey to complete my doctorate work during these last five years was long and difficult. Fortunately, there were many people who helped me along the way. I would like to thank Duncan Lawrie for first offering me a research assistantship through the Department of Computer Science with the Center for Supercomputing Research and Development. David Kuck gave me the opportunity to be a full-time professional at CSRD and has always treated me with respect. George Cybenko has supported my completion of the Ph.D. dissertation and I appreciate his understanding.

I would like to thank the members of the Picasso group. Ruth Aydt's technical assistance in many capacities has helped smooth out the rough spots. Dirk Grunwald was always available for enlightening discussions. The rest of the boys have provided many a laugh to relieve the tensions of the moment.

I give credit to Justin Rattner of Intel for the idea of the HyperMon hardware monitor. Paul Close, also of Intel, was instrumental in securing support for HyperMon's development and has provided much encouragement during the project. Tracy Tilton, John Andrews, and Dan Lavery provided invaluable technical expertise during HyperMon's construction.

What can I say about my advisor, Daniel Reed. He has been my mentor, my colleague, and my friend. His guidance has been helped me mature as a researcher and his respect for my ideas has made working with him very rewarding. I look forward to many fruitful interactions with Dan in the future.

My Father and Mother have always inspired me to do my best. Their lives and achievements have set examples for me to follow. I proudly share this accomplishment with them.

Finally, I would like to thank most of all my wife Kimberly. Her love and encouragement have both supported and sustained me. I could not have achieved this without her.

<sup>&</sup>lt;sup>1</sup>The thesis research was supported by the Department of Computer Science under grants from the National Science Foundation, NSF CDA-87-22836 and NSF CCR-87-06653; and by the Center for Supercomputing Research and Development under grants from the National Science Foundation, NSF ASC-84-04556 and NSF MIP-88-07775, and the NASA Ames Research Center, NCC-2-559.

# TABLE OF CONTENTS

| 1 | Int | roduction                                     | 1  |

|---|-----|-----------------------------------------------|----|

|   | 1.1 | A Performance Evaluation Crisis               | 2  |

|   | 1.2 | Performance Observability                     | 3  |

| 2 | Per | formance Measurement                          | 5  |

|   | 2.1 | Performance Measurement and Observability     | 8  |

|   | 2.2 | Event-Based Performance Measurement Model     | 10 |

|   | 2.3 | Timing                                        | 12 |

|   |     | 2.3.1 Clocks and Timers                       | 12 |

|   |     | 2.3.2 Timer Implementation                    | 13 |

|   |     | 2.3.3 User-Level Timing and Profiling         | 15 |

|   |     | 2.3.4 Context Switch Tracing and Timing       | 17 |

|   |     | 2.3.5 Timing and Parallel Execution           |    |

|   |     | 2.3.6 Global Clock Synchronization            | 20 |

|   |     | 2.3.7 Remarks                                 | 21 |

|   | 2.4 | Tracing                                       | 21 |

|   |     | 2.4.1 The General Tracing Approach            | 22 |

|   |     | 2.4.2 Software-Based Solutions                |    |

|   |     | 2.4.3 Hardware-Based Software Event Tracing   | 27 |

|   |     | 2.4.4 Remarks                                 | 28 |

|   | 2.5 | A Hardware-Based Monitor for the Intel iPSC/2 | 29 |

|   |     | 2.5.1 Intel iPSC/2 Description                | 31 |

|   |     | 2.5.2 HyperMon Design                         | 32 |

|   |     | 2.5.3 Current Configuration                   | 39 |

|   |     | 2.5.4 HyperMon Evaluation                     |    |

|   |     | 2.5.5 Lessons Learned                         |    |

|   | 2.6 | Comments                                      | 51 |

| 3 | Tim | ne-Based Performance Perturbation             | 52 |

|   | 3.1 | Experimental Environment                      | 54 |

|   | 3.2 | Performance Perturbation                      | 56 |

|   |     | 3.2.1 Sequential Perturbations                | 57 |

|   |     |                                               | 59 |

|   | 3.3 | Timing Perturbation Models                    | 60 |

|   |     | 3.3.1 Definitions                             |    |

|   |     | 3.3.2 Execution Time Analysis                 |    |

|   |     |                                               |    |

|   |            | 3.3.3 Event Trace Timing Analysis                        |

|---|------------|----------------------------------------------------------|

|   | 3.4        | Performance Instrumentation                              |

|   | 3.5        | Execution Time Experiments                               |

|   |            | 3.5.1 Sequential C Experiments                           |

|   |            | 3.5.2 Sequential Fortran Experiments                     |

|   |            | 3.5.3 Vectorized Fortran Experiments                     |

|   |            | 3.5.4 Concurrent Fortran Experiments                     |

|   |            | 3.5.5 Vector Concurrent Fortran Experiments              |

|   | 3.6        | Event Trace Analysis                                     |

|   |            | 3.6.1 Loop Two - Incomplete Cholesky Conjugate Gradient  |

|   |            | 3.6.2 Loop Eight - ADI Integration                       |

|   | 3.7        | Comments                                                 |

|   |            |                                                          |

| 4 |            | ent-Based Performance Perturbation: Synchronization      |

|   | 4.1        | Dependence Preliminaries                                 |

|   | 4.2        | Event Perturbation Modeling                              |

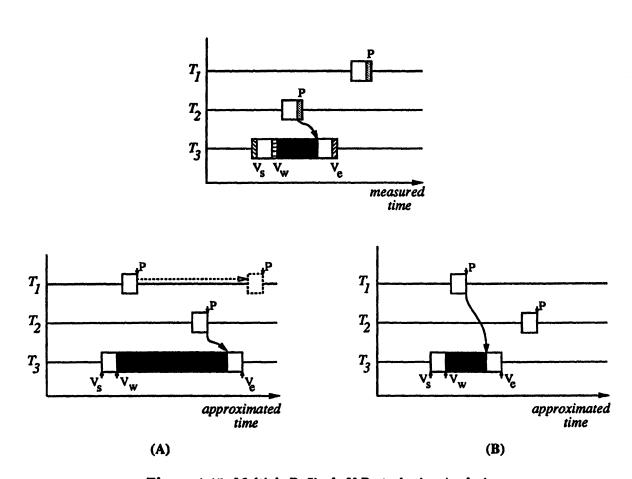

|   |            | 4.2.1 Case One                                           |

|   |            | 4.2.2 Case Two                                           |

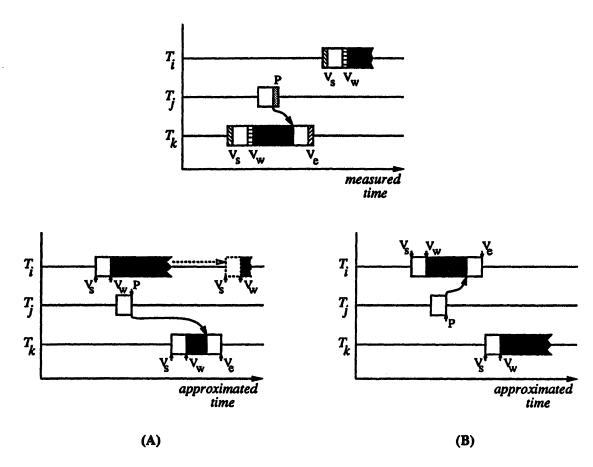

|   |            | 4.2.3 Case Three                                         |

|   |            | 4.2.4 Case Four                                          |

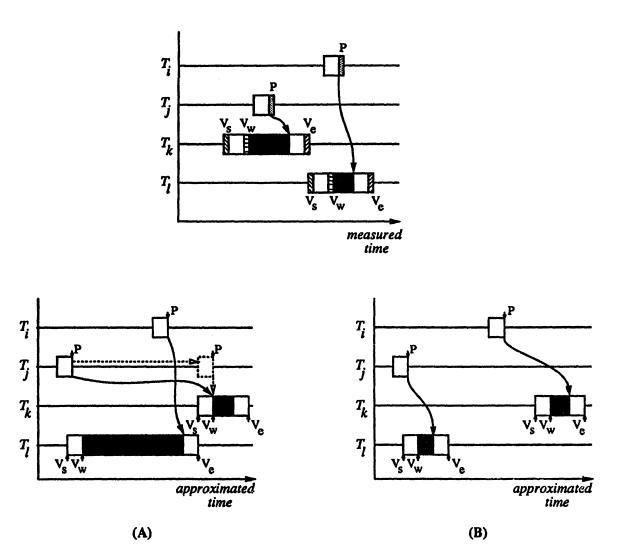

|   |            | 4.2.5 General Synchronization Events                     |

|   | 4.3        | Barrier Perturbation Analysis                            |

|   |            | 4.3.1 Barrier Operation                                  |

|   |            | 4.3.2 Barrier Instrumentation                            |

|   |            | 4.3.3 Barrier Approximation                              |

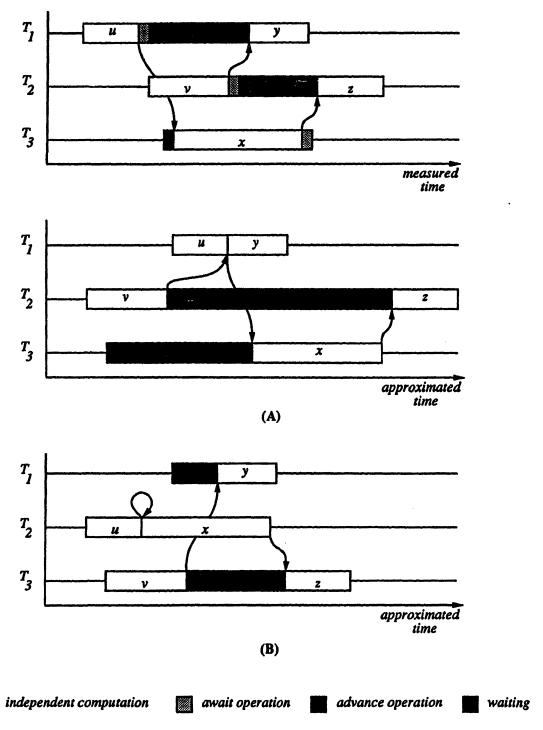

|   | 4.4        | Semaphore Perturbation Analysis                          |

|   |            | 4.4.1 Semaphore Operation                                |

|   |            | 4.4.2 Semaphore Instrumentation                          |

|   |            | 4.4.3 Semaphore Approximation                            |

|   | 4.5        | Advance/Await Perturbation Analysis                      |

|   |            | 4.5.1 Advance/Await Operation                            |

|   |            | 4.5.2 Advance/Await Instrumentation                      |

|   |            | 4.5.3 Advance/Await Approximation                        |

|   | 4.6        | Comments                                                 |

| _ | 70         | nd David David nov                                       |

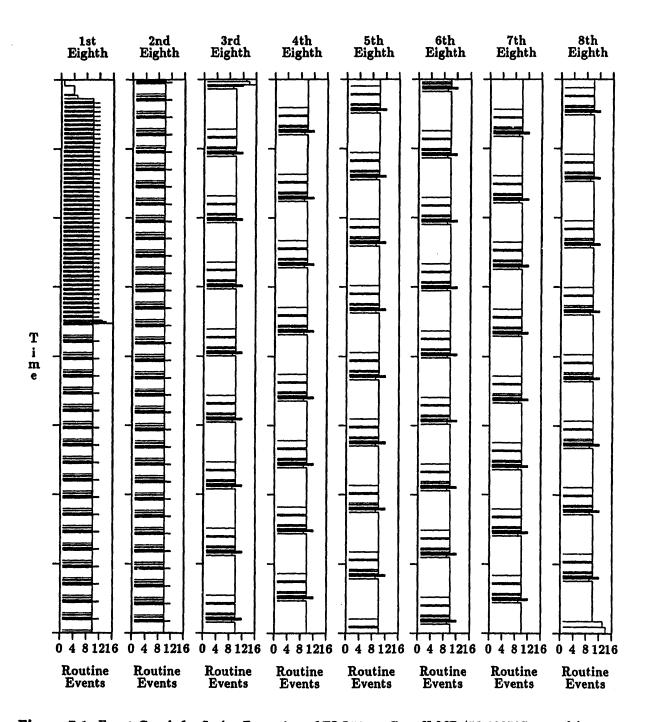

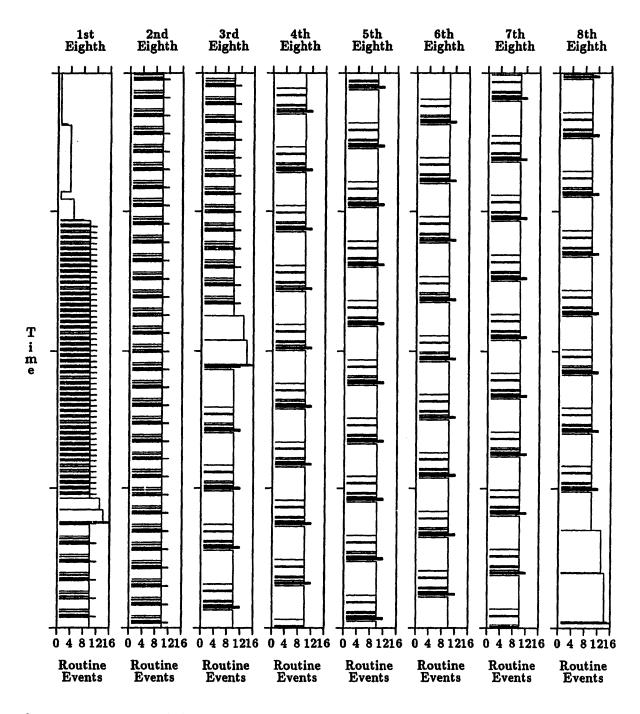

| D |            | nt-Based Performance Perturbation: Loop Analysis         |

|   | 5.1        | DOALL Loop Perturbation Analysis                         |

|   |            | 5.1.1 Static Scheduling                                  |

|   |            | 5.1.2 Dynamic Self-Scheduling                            |

|   | <b>5.2</b> | A DOACROSS Perturbation Analysis Study                   |

|   |            | 5.2.1 The DOACROSS Loop Model                            |

|   |            | 5.2.2 DOACROSS Instrumentation                           |

|   |            | 5.2.3 Synthetic DOACROSS Experiments                     |

|   |            | 5.2.4 Target Environment                                 |

|   |            | 5.2.5 Synthetic DOACROSS Experiment Results              |

|   | 5.3        | Event-Resed Perturbation Analysis of the Livermore Loops |

|      | 5.4   | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | Per   | rformance Visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 6.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |       | 6.1.1 Performance Data Views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |       | 6.1.2 Performance Data Displays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.2   | Case Studies in Performance Visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

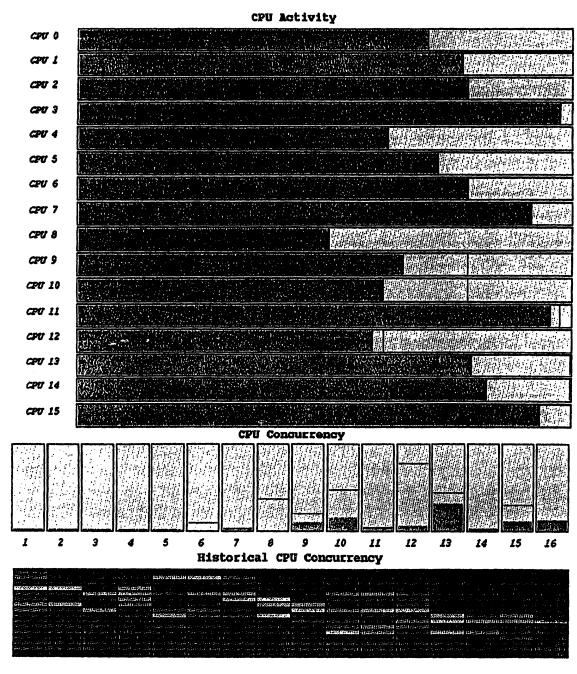

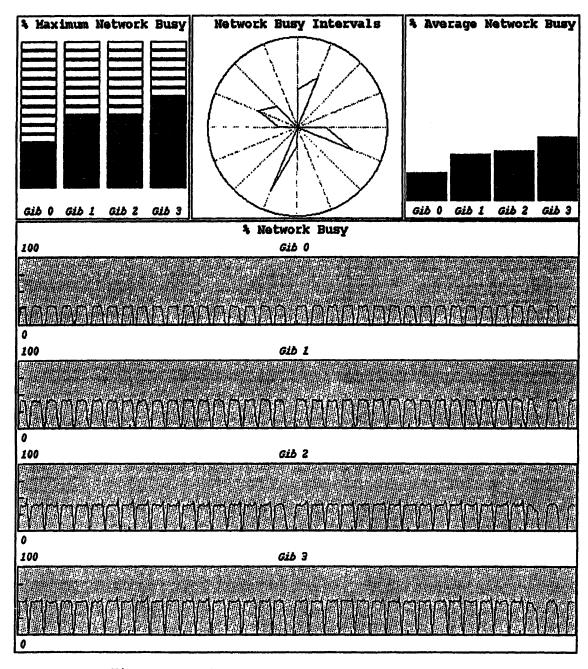

|      |       | 6.2.1 Hardware Performance Visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |       | 6.2.2 System Performance Visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

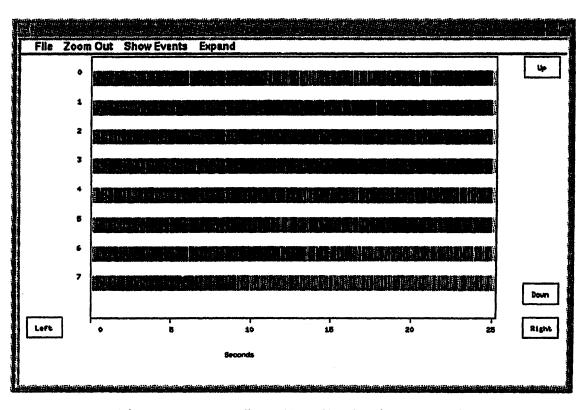

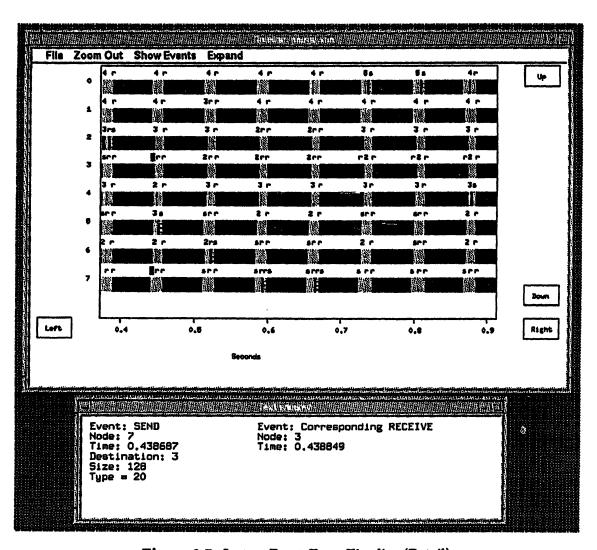

|      |       | 6.2.3 Program Event Visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 6.3   | Performance Visualization Environment Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 6.4   | - distinguisted to be desired the control of the co |

|      |       | 6.4.1 First Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |       | 6.4.2 Second Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 6.5   | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

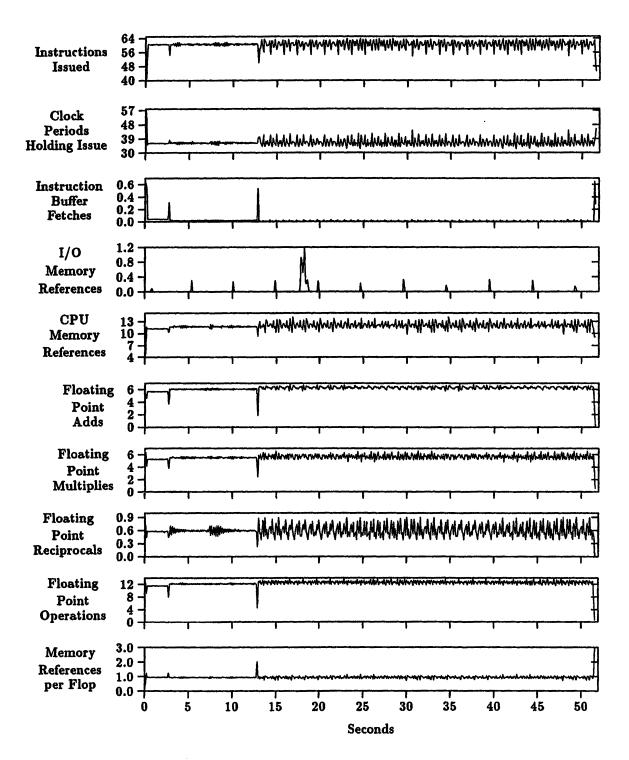

| 7    | Per   | formance Observability Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 7.1   | Supercomputer Performance Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 7.2   | Standard Cray Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 7.3   | A Cray Tracing Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |       | 7.3.1 Software Event Tracing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |       | 7.3.2 TraceFlow and TracePerf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 7.4   | Perfect Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 7.5   | Trace Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |       | 7.5.1 Flowtrace Profiling versus TraceFlow Profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |       | 7.5.2 Perftrace Profiling versus TracePerf Profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |       | 7.5.3 Caveats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 7.6   | Dynamic Execution Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

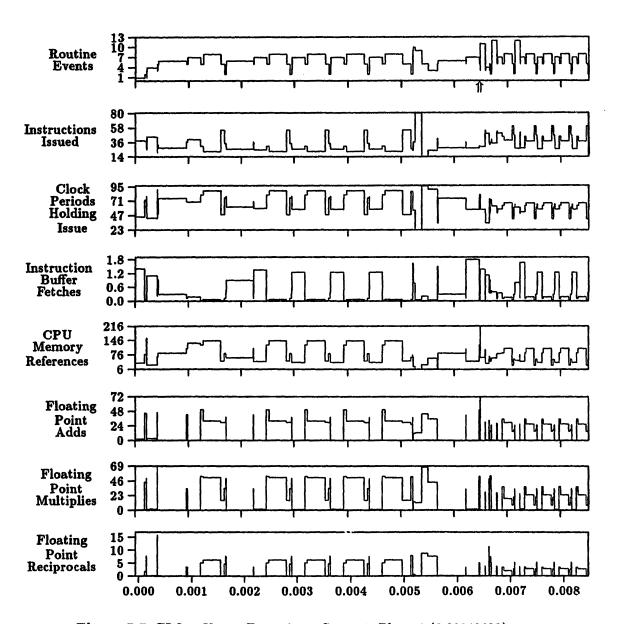

|      |       | 7.6.1 Subroutine Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

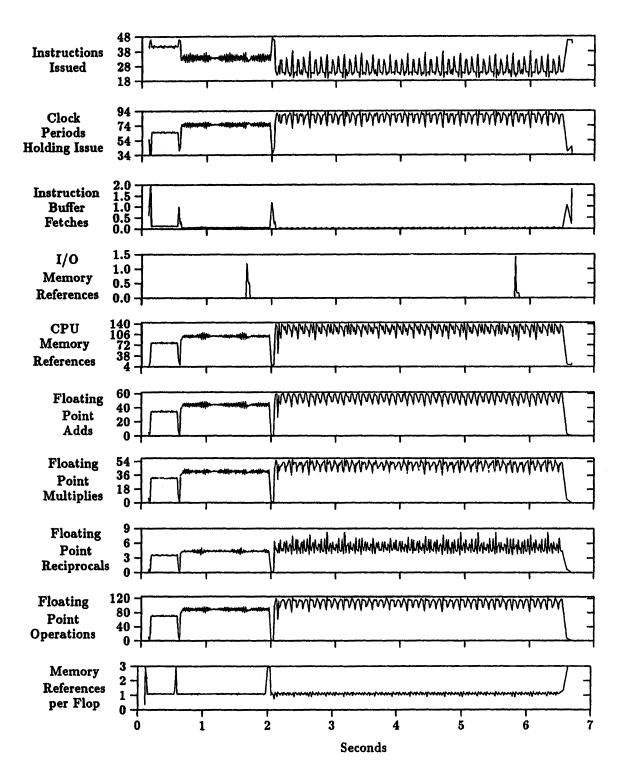

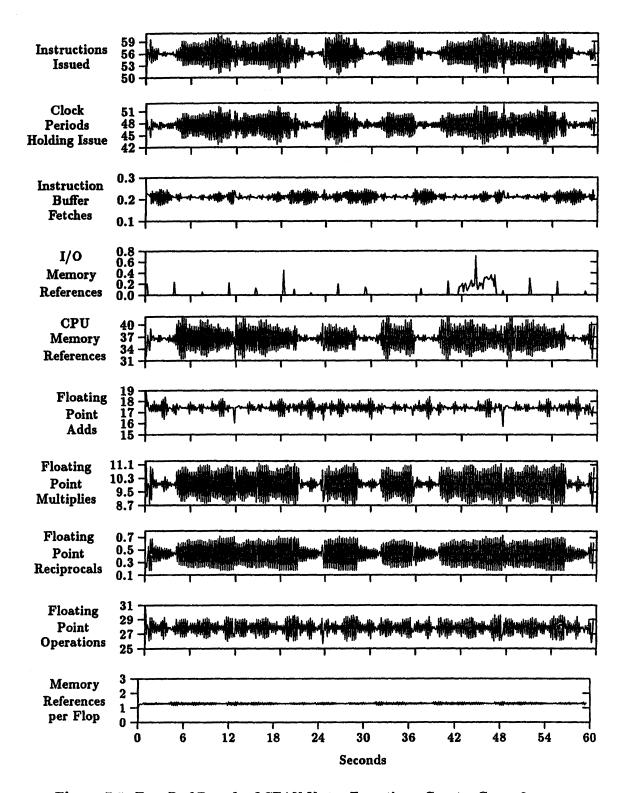

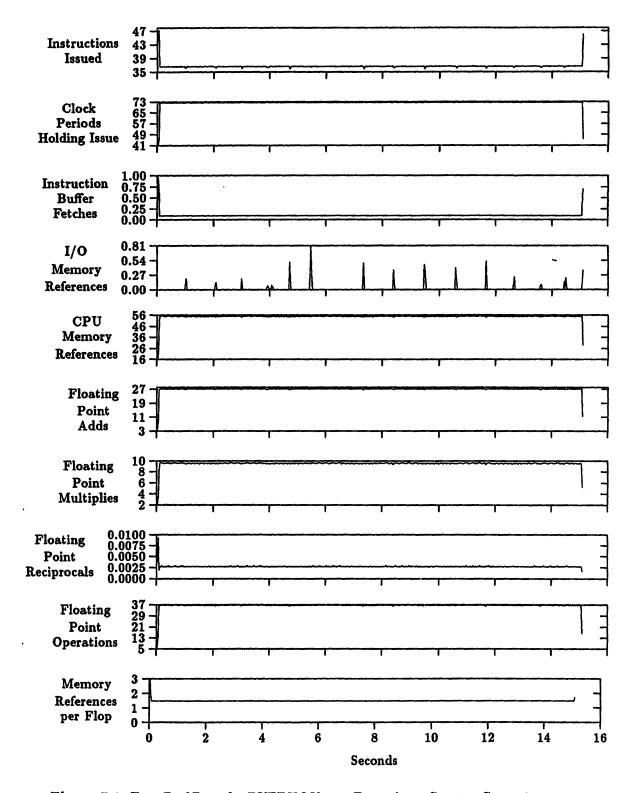

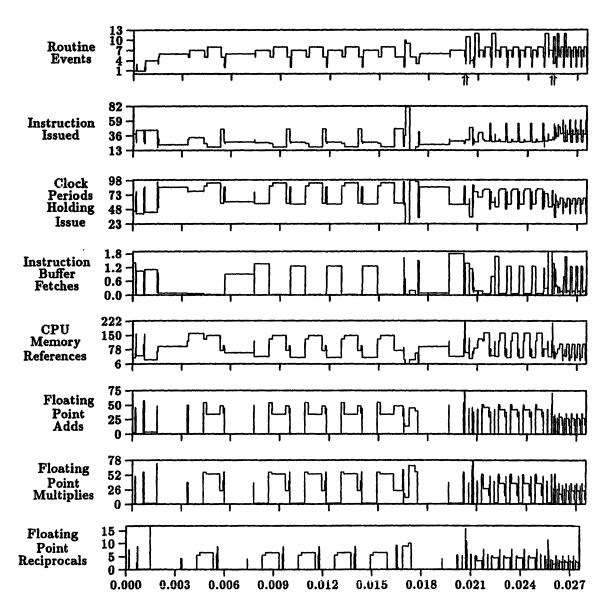

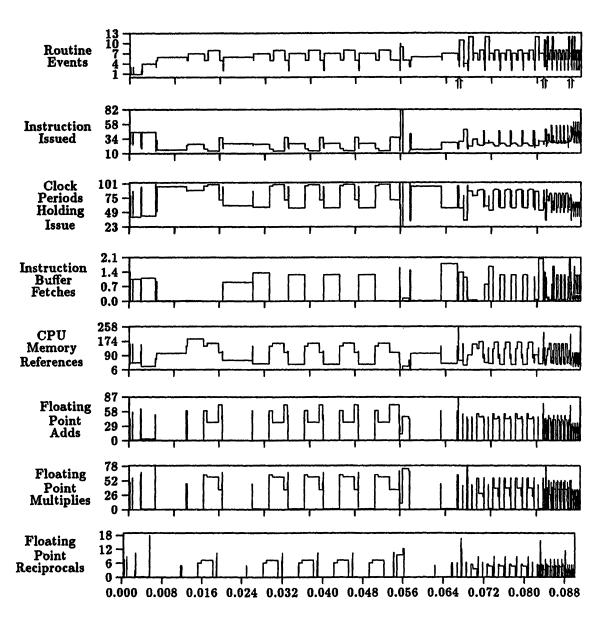

|      |       | 7.6.2 Hardware Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |       | 7.6.3 Procedure Execution and Hardware Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

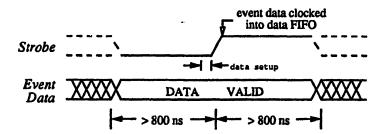

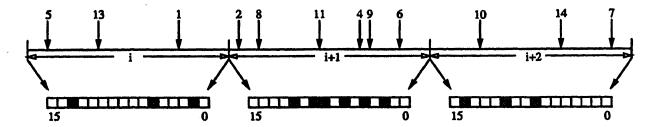

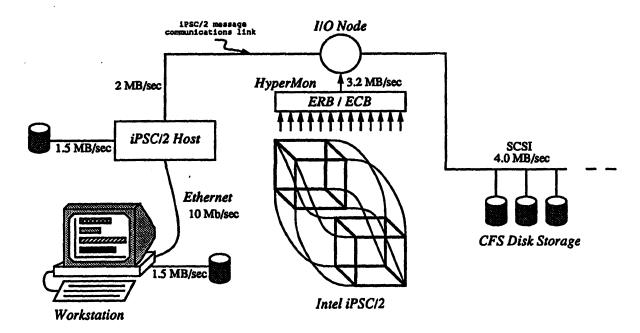

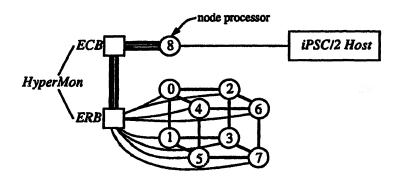

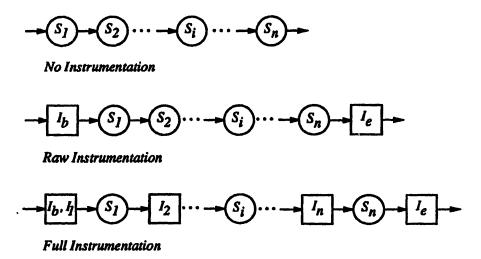

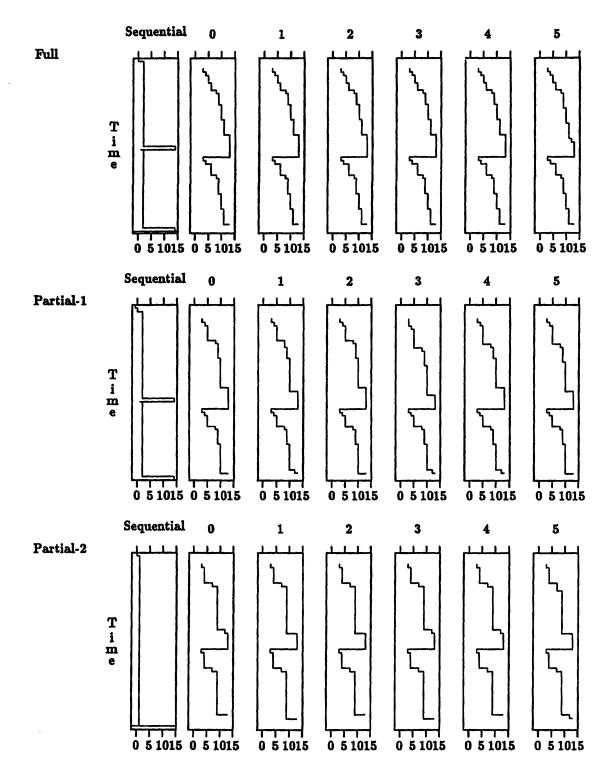

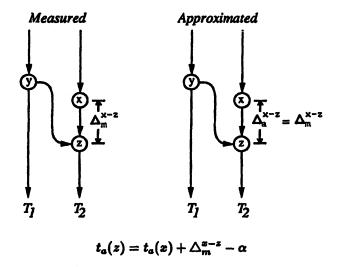

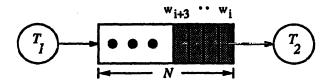

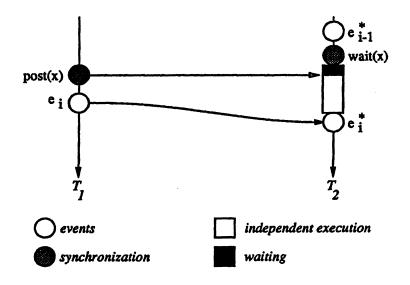

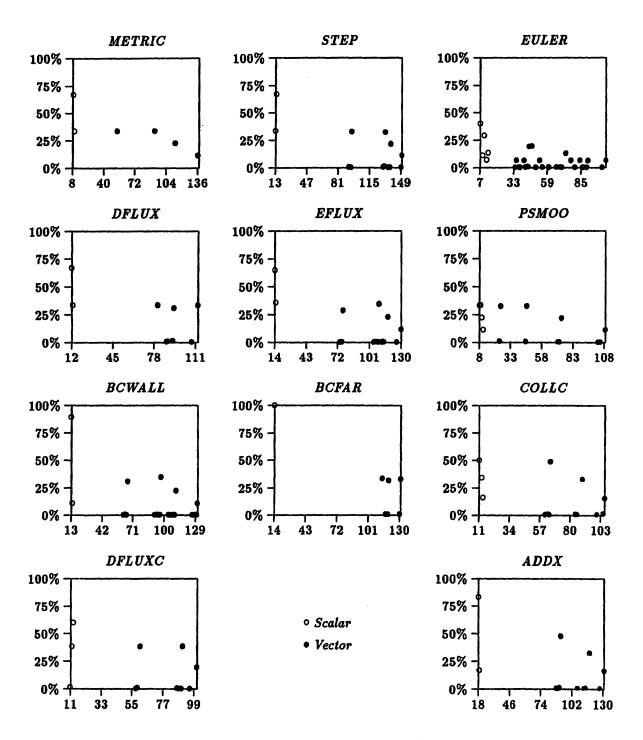

|      |       | 7.6.4 Megaflop Distributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |