## PROCESS ALLOCATION AND LOAD BALANCING IN PARALLEL LOGIC PROGRAMMING

by

MOATAZ ALI MOHAMED

#### A THESIS

Presented to the Department of Computer and Information Science and the Graduate School of the University of Oregon in partial fulfillment of the requirements for the degree of Masters of Science

August 1990

APPROVED:

Dr. John S. Conery

#### An Abstract of the Thesis of

Moataz Ali Mohamed

for the degree of

Masters of Science

in the Department of Computer and Information Science

to be taken

August 1990

Title: PROCESS ALLOCATION AND LOAD BALANCING IN PARALLEL LOGIC

**PROGRAMMING**

Approved:

Dr. John S. Conery

We study the problem of process allocation in the course of executing parallel logic programs. Very little work has been done in addressing the process allocation problem in the logic programming paradigm. We observe that the processes that arise in the course of executing AND/OR model programs have very regular and repetitive communication patterns, which justifies the design of tailored dynamic allocation algorithms that utilize such characteristics to achieve better preformance. The contributions of this research are: first, addressing the dynamic process allocation problem as a graph embedding problem, where two recently developed graph embedding algorithms are adapted to be used in OM (a virtual machine based on the AND/OR execution model). The performance of the algorithms is evaluated using simulations. Second, developing distributed heuristics for process allocation in OM, one of which is the first algorithm to appear in the literature that combines both sender initiated and receiver initiated strategies. Third, describing a queuing model for OM and analyzing the key parameters of the model and their effect on performance.

#### VITA

NAME OF THE AUTHOR: Moataz Ali Mohamed

PLACE OF BIRTH: Alexandria, Egypt

DATE OF BIRTH: July 26, 1966

## GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon Alexandria University, Alexandria, Egypt

## **DEGREES AWARDED:**

Master of Science, 1990, University of Oregon Bachelor of Science, 1988, Alexandria University

## AREAS OF SPECIAL INTEREST:

Parallel Logic Programming

Parallel Processing and Parallel Architectures

Load Balancing and Scheduling

Programming Languages and Compilers

## PROFESSIONAL EXPERIENCE:

Associate System Administrator, Department of Computer and Information Science, University of Oregon, Eugene, June 1990-August 1990

Graduate Research Assistant, Department of Computer and Information Science, University of Oregon, Eugene, December 1988-June 1990 Graduate Teaching Fellow, Department of Computer and Information Science, University of Oregon, Eugene, Fall 1988; Fall 1989; Spring 1990

Visiting Research Programmer, AI Lab, Department of Computer Science, University of Utah, Salt Lake City, Summer 1987

#### AWARDS AND HONORS:

Alexandria University, School of Engineering, Dean's honors list, 1986-1988.

#### PUBLICATIONS:

Lo, V. M., Rajopadhye, Mohamed, M. A., Nitzberg, N., Gupta, S., Keldsen, D., Telle, J. LaRCS: A language for describing parallel computations. In *Proceedings of the 1990 Hawaii International Conference on Systems Sciences*, accepted for publication.

Lo, V. M., Rajopadhye, Gupta, S., Keldsen, D., Mohamed, M. A., Telle, J. OREGAMI: Software tools for mapping parallel algorithms to parallel architectures. In *Proceedings of the 1990 International Conference on Parallel Processing*, (August 1990), pp. to appear.

Lo, V. M., Rajopadhye, Gupta, S., Keldsen, D., Mohamed, M. A., Telle, J. Mapping Divide and Conquer Algorithms to Parallel Architectures

In Proceedings of the 1990 International Conference on Parallel Processing,

(August 1990), pp. to appear.

#### ACKNOWLEDGEMENTS

I wish to express my gratitude to my adviser, John Conery for his guidance and support throughout this research and for his valuable comments on earlier drafts of this thesis. I also wish to thank Virginia Lo for supplying many references to the classical load balancing literature, and for choosing me to work with her in a related project, OREGAMI. I learned a lot about parallel processing, especially process allocation and the mapping problem through my work in this project. Thanks are also in accord to Evan Tick for the discussions on the Japanese research projects, Michael Stafford for the many discussions about the details of OM's implementation, Michael Quinn for comments in the early stages on developing load balancing heuristics, and Amanda Ronai for helping in drawing some of the figures.

## **DEDICATION**

To my parents and two sisters.

## TABLE OF CONTENTS

| Chapt | Ger                                                                                                                                                               | Page           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| I.    | INTRODUCTION                                                                                                                                                      | . 1            |

|       | A Tour in the Parallelism Galaxy                                                                                                                                  | 2              |

|       | Why Parallel Logic Programming?                                                                                                                                   | 5<br>5         |

| II.   | Thesis Overview                                                                                                                                                   | 6              |

| 11.   | CLASSICAL LOAD BALANCING                                                                                                                                          |                |

|       | Introduction                                                                                                                                                      | 8              |

|       | Taxonomy for Load Balancing Algorithms  Load Balancing Algorithms  Conclusions                                                                                    | 12<br>14       |

| III.  | PROCESS ALLOCATION AS A GRAPH EMBEDDING PROBLEM                                                                                                                   |                |

|       | Dynamic Graph Embeddings                                                                                                                                          | 17<br>17<br>20 |

| IV.   | LOAD BALANCING IN PARALLEL LOGIC PROGRAMMING                                                                                                                      |                |

|       | Introduction The Processing Power Plane Multi-level Load Balancing Load Dispatching Strategies for the Parallel Inference Machine Contracting Within Neighborhood | 23             |

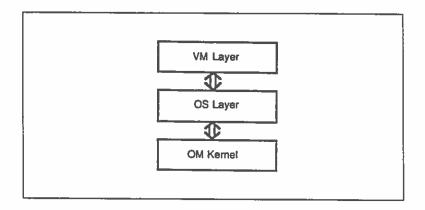

| V.    | OVERVIEW OF THE OPAL MACHINE                                                                                                                                      | 40             |

|       | Introduction                                                                                                                                                      | 40<br>40<br>41 |

|       |                                                                                                                                                                        | ix                   |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|       | Communication Characteristics of the AND/OR Model The OPAL Programming Environment The OPAL Machine The Process Allocator                                              | 43<br>44             |

| VI.   | PROCESS ALLOCATION ALGORITHMS FOR OM                                                                                                                                   | 47                   |

|       | Generalized Random Walks The Crawl Algorithm ANDs Crawl, ORs Run Walk With Your Neighbors The Rendezvous Algorithm The AND-Shipping, OR-Stealing Algorithm Conclusions | 50<br>51<br>51<br>51 |

| VII.  | SIMULATIONS AND PERFORMANCE EVALUATION                                                                                                                                 |                      |

|       | The Simulation Environment                                                                                                                                             | 55                   |

| VIII. | A QUEUING MODEL FOR OM                                                                                                                                                 |                      |

|       | Bounding the Number of Processes                                                                                                                                       |                      |

| IX.   | CONCLUSIONS AND FUTURE RESEARCH                                                                                                                                        | 74                   |

| BIBLI | OGRAPHY                                                                                                                                                                |                      |

## LIST OF TABLES

| Table |                                              |  |  |  |  |    | ] | Pag |

|-------|----------------------------------------------|--|--|--|--|----|---|-----|

| 1.    | Calculation of Min-hops and Max-hops in ACWN |  |  |  |  | ٠. |   | 37  |

## LIST OF FIGURES

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

| 1.     | An Example of Contention in a Mapping                             | 20   |

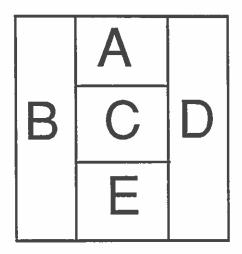

| 2.     | Subtask Distribution in the Multi-level Algorithm                 | 30   |

| 3.     | An Example of a Non-optimal Allocation in CWN                     |      |

| 4.     | The Software Layers of OM                                         |      |

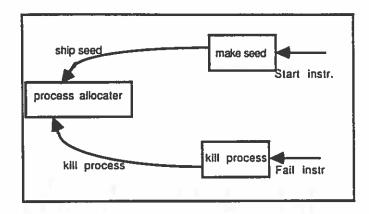

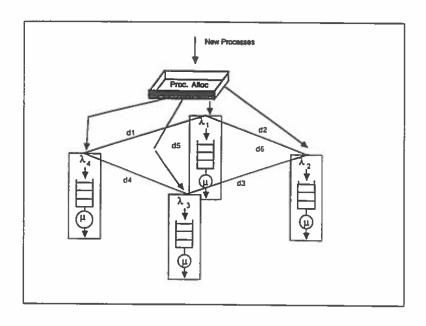

| 5.     | The Interface Between the Process Allocator and the OS Components |      |

| 6.     | The Map                                                           |      |

| 7.     | The Map Coloring Program in OPAL                                  |      |

| 8.     | The Even Path Program in OPAL                                     |      |

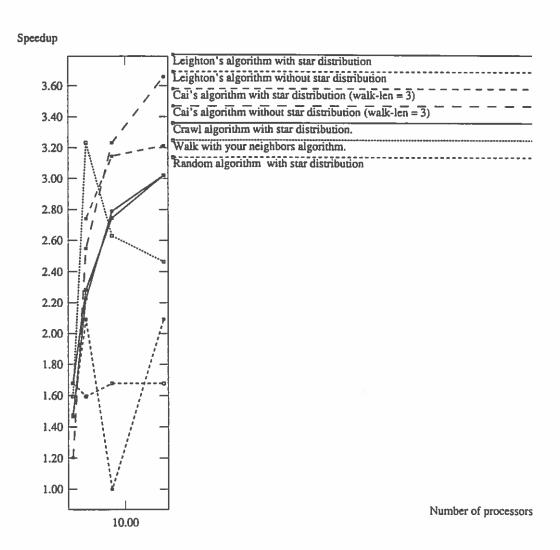

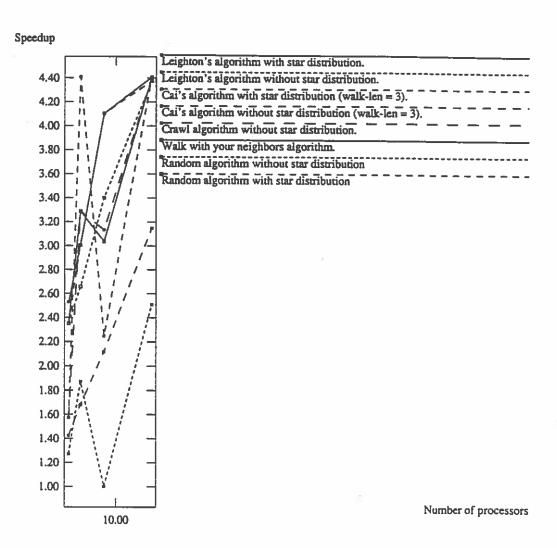

| 9.     | The Speedup in the Map Coloring Program                           |      |

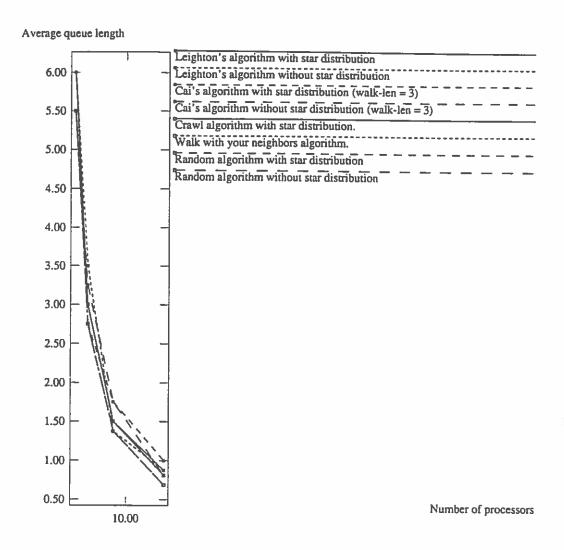

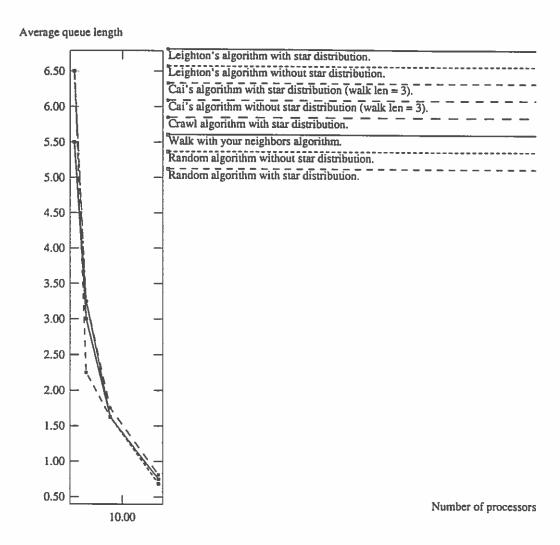

| 10.    | The Average Queue Length in the Map Coloring Program              |      |

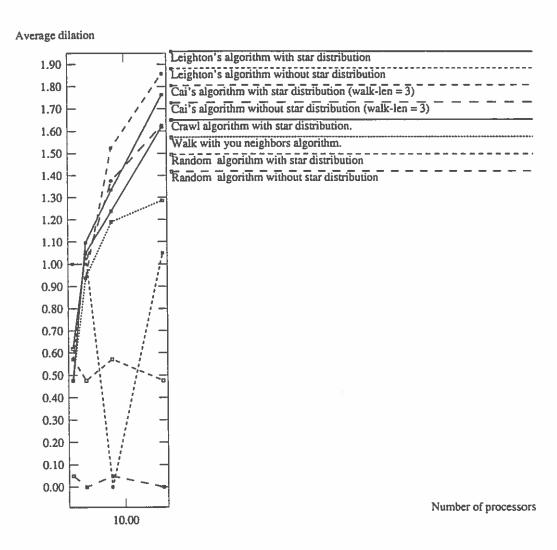

| 11.    | The Average Dilation in the Map Coloring Program                  |      |

| 12.    | The Speedup in the Path Program                                   |      |

| 13.    | The Average Load in the Path Program                              |      |

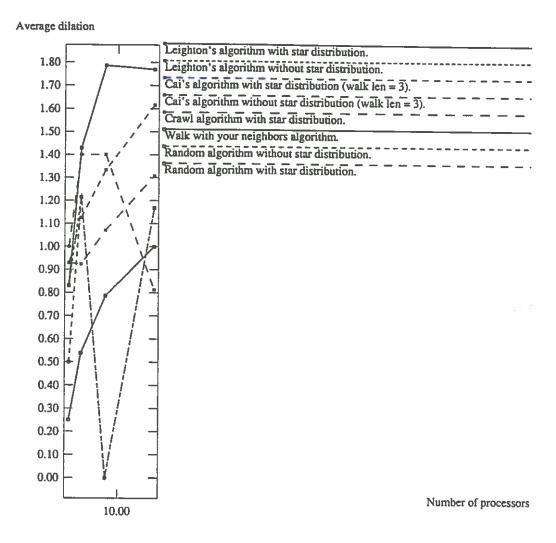

| 14.    | The Average Dilation in the Path Program                          |      |

| 15.    | A Queuing View of Process Allocation in OM                        |      |

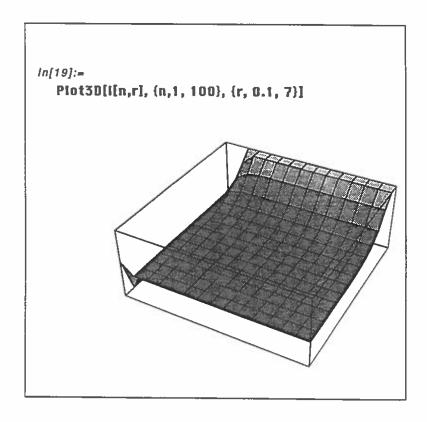

| 16.    | A Plot of the Average Queue Length Function                       |      |

#### CHAPTER I

#### INTRODUCTION

Parallel processing is a rapidly developing field that is attracting the interest of researchers from various disciplines. Speed, being the obsession of every programmer or researcher who has a large scale or computationally intensive problem, is one of the primary motivations. However, as the current developments in the field stand, running a program on a machine with more processors does not necessarily imply better performance.

The parallel processing field is currently partitioned into several competing programming paradigms. In the following section we will attempt to provide a brief overview of these paradigms and point out some of the primary concerns in programming the representative machines of each of those paradigms. We also name some of the applications that seem well suited to those machines, as well as those that programmers have found difficult to map to the architecture.

#### A Tour in the Parallelism Galaxy

Shared memory multiprocessors.

A shared memory multiprocessor is composed of several main stream microprocessors usually connected by a bus and sharing a global memory. Typical examples of this class are the Sequent Symmetry, Alliant Fx/80, and the Encore Multimax. The main problems in programming such machines are locking and synchronization over shared data structures and cache coherency. Lack of scalability is also a problem since the architecture is constrained by the physical limitation on the number of processors that can be connected on a shared bus. Several parallel logic programming systems, such as Aurora [27] Andorra [14] have been successfully implemented on shared memory machines.

• Message passing multicomputers.

Multicomputers are composed of autonomous loosely coupled processors connected by an interconnection network [1]. The processors are usually full fledged main stream microprocessors with each processor having its own memory. No global shared memory is supported. The main advantage of these systems is their scalability. The primary disadvantage is the high cost of communication over the network. One of the main problems in programming these architectures is mapping the application programs onto the architectures. Several research projects are currently addressing this problem in the context of developing integrated environments of compilers and mappers that would relieve the programmer from hard-coding the mapping into her/his code. Examples of this class are the hypercube architectures, such as Intel's iPSC/2 and NCUBE; mesh architectures such as ICOT's Multi-PSI; the BBN Butterfly, the twisted torus HP Mayfly; and the Pyramid machine.

#### • Vector processors.

Vector processors were the first commercially available machines to target the data parallelism application domain. The main idea was to partition the data into vectors so high speed vector operations could be performed on them. Typical examples of this class are the Cray machines, such as the CRAY-1, X-MP, and Y-MP. One of the primary reasons of the success of vector processors is compiler technology, particularly Fortran compilers. The compilers do intelligent optimizations in analyzing the number of iterations in a loop and the data dependences to fit the arrays in vector registers [15].

SIMD massively parallel array processors.

SIMD (single instruction multiple data) architectures were pioneered by the design of the ILLIAC-IV computer. Recent commercial SIMD machines are Thinking Machines' Connection Machine (CM) [16] and MasPar's MP-1. The main idea in the design of these architectures is to connect a huge number of very primitive processing elements (PE) in an array or hypercube fashion. The architecture targets the

class of applications which are very fine grain with a high degree of regularity, such as image processing, weather simulations, and matrix computations. It is our belief that any problem for which a systolic algorithm can be written could be efficiently programmed on such architectures.

#### The Parallel Programming Dilemma

From the programming viewpoint, researchers have taken several conflicting approaches towards programming parallel architectures. One current trend in parallel processing research is the development of new programming environments specifically for certain architectural platforms. There are three main directions that seem to be having a degree of success. One is to take popular established languages such as Fortran or C and augment them with extensions for parallelization. Examples of such languages are the iPSC C and CM-Lisp.

Another approach is to devise novel parallel languages that have originally parallel semantics and that do not assume any particular target architecture. An example of this approach is the Strand88 language.

The third approach is to design a portable threads library that can be used as an add-on to various sequential programming environments. Clearly this library is to be portable across various architectural platforms. Linda could be regarded as an example of this direction since Linda is independent of the host programming language and thus can be used as an add-on parallelization extension. The main difference between this approach and the first one is that it is more generic since it is independent of both the target architecture and the programming language. In some sense, this portability is a direct result of factoring out (decoupling) the threads library from the programming language and the architecture-specific details.

#### The Quest for Efficiency

Every parallel programmer must have experienced at some point the funny feeling of having her/his parallel program run slower than its sequential counterpart. Another

serious problem is having non-monotonic speedup curve, i.e., at certain regions in the curve the time increases while increasing the number of processors. This implies that the program has either sequential bottlenecks or communication-intensive regions that tend to dominate when the program is executed using a number of processors in that range. There is a consensus in the computer science community that making a parallel program more efficient is much harder than optimizing a sequential problem. One of the main factors contributing to this situation is the lack of robust symbolic debuggers, program profilers, trace generators, and similar tools which would help programmers analyze their programs and determine their execution bottlenecks. Many of these tools are currently under construction in academia and in industry.

## Architecture Independent Parallel Programming

Architecture independent programming facilitates two properties that are major goals in programming language design: portability, and an abstract level of programming. The programmer should program at a level of abstraction that lets her/him concentrate on the algorithmic issues themselves and not be burdened with machine specific details, such as the number of processors and the interconnection network characteristics.

One approach researchers have taken to provide for architecture-independent programming is to develop automatic mappers that would automate the process allocation problem. Depending on the computation model, the mappers can either operate statically (at compile time) or dynamically (at run time). Strand88, one of the commercial concurrent languages, totally ignores the problem and leaves it to the programmer to do the process allocation.

We believe that the motivations behind architecture independent parallel programming are very similar to those of the sequential declarative programming paradigm in the sense that we want the programmers to concentrate on their algorithm's characteristics, such as, what constitutes a process, how the processes communicate, and what the algorithm does, instead of spending time considering issues like how many processes should be mapped to one processor or deriving a function that maps a process label to a pro-

cessor number. These issues dictate how the algorithm is to be executed, which should not be the programmers' concern. The less the programmer is burdened by control issues the less productive the programming environment is, especially with the ever increasing complexity of control in programming parallel machines.

## Why Parallel Logic Programming?

The elegance of logic programming as a programming paradigm is attributed to its declarative nature. Programmers only specify what the algorithm computes without specifying how it should compute it. Thus the implementation is left open to the underlying environment. It is this freedom that opens the door for parallelism. It is now clear that overspecification is often the main obstacle in achieving efficient parallelism. This clean separation of semantics and control is what gives logic programming its power and suitability to parallelism.

Parallel logic programming offers a unique mix of the advantages of the above approaches. It has the same "look and feel" of an old successful language, namely Prolog. The semantics of pure logic programming do not have the sequential restrictions of the conventional Von Neumann languages, and thus lends itself very naturally to parallelism. The last advantage is portability which is a direct consequence of the emphasis on logic rather than control. Clearly, programs that do not explicitly specify control issues will be machine independent which facilitates source-level portability.

#### Goals

In this research, we study the problem of allocating dynamically spawned processes arising in the course of the execution of parallel logic programs. There has been very little work on this problem in the logic programming literature. However, the problem of process allocation and load balancing has been extensively studied in its own right, independent of a particular computation model. In this study, we survey the recent work that has been done in the context of existing parallel logic programming systems, and introduce new process allocation heuristics that achieve good performance according to

the metrics of speedup, load sharing, and bounded dilation.

The setting of the problem is as follows. The target architecture is assumed to be a message passing architecture with any type of interconnection network. We do not assume the existence of a global address space. We assume that each processor has a minimal kernel resident at that node. The programming language used for coding the programs (OPAL, a Prolog-like language with AND/OR parallelism) does not express any user-specified mapping information and thus the user does not interfere with the mapping of the processes to the processors. Hence, the allocation strategy is totally automatic and transparent to the user.

The main goal of this study is to design efficient process allocation heuristics for message passing parallel logic programming systems. One of the main motivations of this study was to incorporate ideas from three areas: graph embeddings, classical load balancing, and queuing theory. This study is also an exercise in evaluating heuristics for an open problem for which even the performance metrics are subject to debate. We have looked at the problem from two different views: graph embedding and process allocation. The original goal was to implement the heuristics on message passing parallel architectures such as the hypercube, but since the parallel implementation of OM was not yet ready at the time of this study, simulations were chosen to test the ideas presented here.

#### Thesis Overview

In chapter II we first present a taxonomy of load balancing algorithms, followed by a survey of some of the most relevant classical load balancing algorithms that were developed for either distributed computing or parallel processing systems. Each of the algorithms is evaluated and classified in view of the presented criteria. In chapter IV we survey the load balancing algorithms that were specifically designed to be used in parallel logic programming systems. Graph embedding is presented as a model for dynamic process allocation in chapter III, where two recent algorithms for embedding trees into hypercubes are discussed. Then, the proposal of using configuration languages as a tool to express the programmer's knowledge about the program's characteristics and pass it on to

the allocator to achieve efficient embeddings is examined. An overview of the AND/OR process model and the architecture of the OPAL machine is presented in chapter V together with a discussion of the most prominent communication and execution characteristics of the processes. The process allocation heuristics we developed are presented in chapter VI. In chapter VII, we discuss the simulation environment and the performance evaluation of the algorithms according to the various proposed metrics. Chapter VIII presents a queuing model for OM and discusses some of the important parameters of the model and their impact on performance. Finally, our conclusions and future extensions to this research are presented in chapter IX.

#### CHAPTER II

#### CLASSICAL LOAD BALANCING

This chapter gives a survey of classical process allocation and load balancing algorithms, with an emphasis on dynamic algorithms. We present a taxonomy for such algorithms according to some of their common characteristics. The impact of these characteristics on some performance metrics is also discussed. Finally, we address the analogy between the results obtained from the work on load balancing algorithms for distributed systems and dynamic allocation algorithms for multicomputers.

#### Introduction

The complexity of designing a multiprocessor is rapidly decreasing as the field of parallel architecture is advancing. However, the efficient programming of such sophisticated machines is not getting any easier. The problems that arise in the course of programming a multicomputer are primarily due to the difficulties and the overhead incurred in mapping the computation to the processors of the architecture. This problem can be tackled either statically (i.e., at compile time), or dynamically (i.e., at run time).

Throughout this thesis, we will mainly focus the discussion on homogeneous message passing multicomputers, where all the processors are identical and no global shared memory exists. We will review some of the dynamic load balancing algorithms that addressed the problem in both distributed and parallel processing systems.

#### Definitions and Preliminaries

In this section, we will give the definitions of the terms used throughout the paper. Some of these definitions are not widely used yet, but we believe they are gaining enough popularity that their standardization is to be expected.

#### • Mapping Algorithm

A mapping algorithm assigns each process in the computation a processor in the architecture. The typical goals of mapping algorithms are to achieve constant load among the processors (load balancing) and to minimize the dilation (defined below).

## • Load Balancing Algorithm

A load balancing algorithm distributes the computation tasks among the processors, maintaining constant load among all the processors of the system. One might think that a load balancing algorithm is simply a mapping algorithm and there should not be any need for the distinction. It is certainly true that load balancing algorithms are a subclass of mapping algorithms, however the distinction is important since some systems do the process allocation in two stages: first some kind of a random mapping is used, then a load balancing algorithm is invoked to improve the mapping decisions.

#### • Load Sharing Algorithm

A load sharing algorithm is one that distributes the computation tasks among the processors, but is not guaranteed to maintain constant load across all the processors of the system. It is important to note that almost all claimed load balancing algorithms are really load sharing algorithms since guaranteeing uniform load on all the processors in the system is almost always impossible. Therefore, we will use the terms interchangeably throughout this document.

#### Thrashing

Thrashing is the situation where all the processors are busy transferring tasks and no actual computations are executed. This phenomenon is often encountered when the mapping algorithm does not incorporate a control policy for terminating the transfer of a task.

The Degree of an Interconnection Network

The degree of an interconnection network is the maximum number of links incident

on one node (processor) in the network. A network is said to have a uniform (constant) degree if all the nodes have the same degree, such as in the hypercube. An example of a non-uniform degree network is a mesh, where nodes in the interior have degree four and nodes on the perimeter have degree two or three.

# The Diameter of an Interconnection Network The diameter of an interconnection network is the longest path between any two processors in the network. The radius is half the diameter.

#### • Dilation

The dilation is defined to be the stretching that the edge in the computation suffers from due to the mapping of nodes connected by the edge to distant processors in the architecture. The dilation of the mapping is the maximum distance in the architecture between nodes which are adjacent in the computation graph. The average dilation of the mapping is calculated by taking the average over all the dilations of the communication edges in the computation graph through the execution of the program. There is some subtlety involved in dilation measurement, since in most networks there will exist more than one path of varying lengths between any two processors in the system. We will assume that the minimum length path is the dilation of that communication edge. This assumption implies that the routing algorithm will consistently choose the optimal route (in terms of hop-count), which might not always be possible.

#### Load

The load of a processor is the number of processes (computation nodes) that are mapped to it, and thus have to be time multiplexed on that processor. However, it is very important to note that this measure is not accurate, as it assumes that processes have comparable computational requirements. If indeed, a large variation in the processing time exists between the processes in the system, more sophisticated means for estimating the execution time of each process should be provided and the later should be used in calculating the load. Korry did a study of load assessment

in a distributed system consisting of a network of Sun 2 workstations [20]. His experiments showed that a combination of the processor utilization, the number of context switches, and the number of page swaps yielded the best result in terms of predicting response time. The load of a mapping is defined to be the maximum of all the loads of the processors involved in the mapping. Load is an indication of the computation cost, since, as the number of processes mapped to the same processor is increased, the overhead of context switching is greater. Throughout this thesis, the default definition will be the number of processes residing on a given processor, unless otherwise stated.

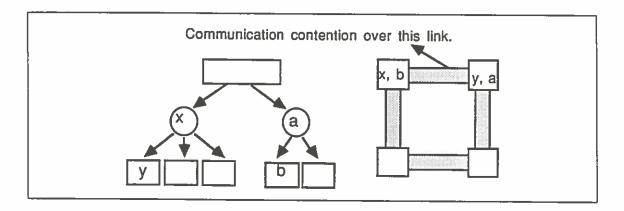

#### Communication Contention

Contention over a link in the interconnection network occurs when two messages (or packets) attempt to use the link at the same time. Communication contention is costly for several reasons. First, since one of the messages will have to wait, the destination processor of that message will be idle while awaiting this message. Second, if a different route is chosen for one of the contending messages, most probably it will be longer and thus will take more time, in addition to increasing the probability of contention along the links of this longer route.

#### • Completion Time

Completion time is the gross figure that indicates the wall clock time the machine took to execute the program. This figure is often used in speedup measurements and not given directly since it is highly dependent on the architecture, compiler, load conditions, etc.

#### Speedup

Speedup is by far the most common performance metric used in parallel processing. It is defined to be the ratio of the completion time of the program when run using more than one processor to the time it takes to run on one processor (i.e., sequentially) [12].

#### • Processor Utilization

A processor's utilization is the ratio of the time the processor was busy to the total execution time of the program. The average of the utilization of all the processors in the machine is taken to be the overall utilization figure. The drawback of this metric is that it does not indicate the percentage of time useful work is done as opposed to overhead such as packing and unpacking of messages. An ironic example is that when the system is thrashing, almost all the processors will exhibit very high utilization factors.

#### Taxonomy for Load Balancing Algorithms

There has not been a standard unifying classification model for load balancing algorithms in the literature. Below are several classifications (some of which are orthogonal) which will be used throughout the paper. It is important to note that some of these classifications might seem very similar. This taxonomy is based on and contains extensions to those presented in [9], [20].

#### Adaptive vs. Preset

An adaptive algorithm is one that uses the system's state information in making its decisions. A preset algorithm has a canned fixed strategy which it always executes independently of the state of the system.

#### Static vs. Dynamic

A static mapping algorithm is one that operates on a static computation graph, i.e., a graph in which the number of processes and their communication edges are fixed. In other words, no more processes will be spawned and no more communication edges will be established. Hence, a static mapper can get all the information it needs at compile time. On the other hand, a dynamic mapper is one that maps dynamically evolving computations (i.e., graphs that shrink and grow). Hence, dynamic mappers have to be invoked during the execution of the computation whenever a new process is spawned or when some other event occurs.

#### • Deterministic vs. Probabilistic

A probabilistic mapping algorithm is one that associates a probability with each of the possible destinations of the transferred node. A deterministic algorithm is one that is certain about the destination node for the transfer.

## • Sender Initiated vs. Receiver Initiated

A sender initiated algorithm is one in which lightly loaded processors ask for more load. In a receiver initiated algorithm a congested processor tries to transfer a task to some other lightly loaded processor.

## • Topology Dependent vs. Topology Independent

Whether or not an algorithm depends on the interconnection topology of a system is an important metric in evaluating a mapping algorithm, particularly if the algorithm is to be used on a system with a reconfigurable interconnection network (IN). An algorithm that was designed to work on a particular IN is highly likely not to perform well on another IN, if it works at all. On the other hand, for machines with fixed IN, an algorithm that was tailored for such an IN will probably be optimal compared to a generic topology independent algorithm.

## Permitted Migration vs. Prohibited Migration

A mapping algorithm that permits process migration is one that allows processes to be transferred after they were started. Clearly, this constitutes high run-time overhead since it involves the transfer of large status tables over the interconnection network. In an algorithm that prohibits process migration, once a process is started on a given processor, it will stay there until it terminates.

#### • Fairness

Fairness is the guarantee that no process in the system suffers from indefinite postponement. This criterion is most commonly used in conjunction with schedulers, but since some of the load balancing algorithms do process allocation as well (as opposed to doing the balancing stage after the allocation is done) it is important to incorporate fairness as a classification criterion.

#### **Load Balancing Algorithms**

Most previous work in load balancing addressed the problem of balancing load across the nodes of a distributed system and local area networks. In both cases, a node is an independent computer. A survey of some of those algorithms that are relevant to our approach will be given in the following sections. We only consider algorithms for homogeneous systems. An interesting common feature of all these algorithms is that they are all independent of the interconnection network topology, i.e., architecture independent. The algorithms vary in their complexity according to the amount of system state information they collect.

#### Pressure Gradient

The gradient model load balancing algorithm introduced by Lin and Keller is a topology-independent adaptive algorithm [23]. The algorithm is based on the idea that a lightly loaded processor triggers the balancing mechanism by informing its immediate neighbors that it demands more work load. The algorithm is composed of two basic steps. First, each processor determines its own loading condition and sends this information to its neighbors. The second step establishes a gradient surface. Each processor should calculate its proximity value, where the proximity of a processor is defined to be its distance from a lightly loaded processor. The gradient surface is the aggregate of all the proximities. However, since proximity calculation requires the collection of all the proximities from all the processors in the system, they use a pressure gradient to approximate the gradient surface. The propagated pressure of a processor is defined to be zero if the processor is lightly loaded. Otherwise, the pressure is one plus the minimum of the propagated pressures of its immediate neighbors. Notice that this propagated pressure reflects the closeness of a processor to a lightly loaded processor. The pressure surface of the network is the collection of the propagated pressures of all processors.

This algorithm can be regarded as receiver initiated, since task transfers are indi-

rectly initiated by lightly loaded processors. The algorithm is clearly deterministic and does not employ randomness at any level. Most importantly it is adaptive since the allocation decisions are influenced by the proximity information which is gathered at run-time.

#### Random

In a random load balancing algorithm, a processor decides where to map the new process by selecting a node at random and transferring the process to that node. It has been shown that if the system is restricted to such a simple strategy, it will certainly exhibit the thrashing phenomenon in the steady state under high loads. A simple cure for this incorporates a static transfer limit that restricts the number of times that a task can be transferred.

This algorithm is an example of a preset mapping algorithm since it does not collect any state information and thus does not react to changes in the system state. Purely random allocation algorithms are rapidly gaining popularity and almost any distributed or parallel environment that has been implemented has employed some variant of a simple random allocation algorithm. The most obvious benefits are simplicity and scalability which are direct consequences of randomness.

#### Threshold

In a system based on thresholds, a static threshold of the maximum number of processes on a given processor is predetermined. To transfer a process, the sender probes a candidate receiver to see if transferring that process would place the receiver above the threshold. If so, another candidate receiver is picked, otherwise, the task is transferred to that processor. A control policy has to be incorporated to govern this probing scheme. One proposed policy is to continue with the probing until either a viable processor accepts the task or the number of probes exceeds a static predefined probe limit.

We notice that the threshold is not an upper bound on the load maintained by the algorithm, since when the static limit on the number of probes is reached, the receiver's load is actually placed over the threshold. Thus, a tight bound on the load achieved by

this algorithm cannot be determined.

#### Shortest Queue

A variation on the threshold algorithm tries to make the best assignment based on the amount of information it collects. A sender probes a group of receivers seeking one that can host the task. The processor with the shortest queue length is chosen to host the task unless the transfer would make it exceed the load threshold. In the latter case, the sender processor is obliged to process the task locally. This algorithm also does not have a tight bound on the maximum load of the mapping it provides.

#### Conclusions

The results of the work on the load balancing in homogeneous systems indicate that simple strategies which do not react to system state fluctuations, and thus have very little run time overhead, work nearly as well as complex strategies which collect a lot of information. In other words, according to the classification provided earlier, this means that algorithms that use a preset strategy are to be preferred to adaptive algorithms. It has also been shown that sender initiated policies outperform receiver initiated methods at light to moderate loads [10].

Dynamically evolving computations arise very often in a number of programming techniques. The difficulties that arise in executing these computations are due to the fact that very little information about the computation can be inferred statically and thus mapping algorithms have to be incorporated at run time. Thus, the overhead due to the complexity of the mapping algorithm has a great impact on the total execution time of the computation. Extensive research on load balancing algorithms for distributed computing and parallel processing systems has shown that simple randomized algorithms are preferred to complex deterministic ones.

#### CHAPTER III

## PROCESS ALLOCATION AS A GRAPH EMBEDDING PROBLEM

#### Dynamic Graph Embeddings

A parallel algorithm can be viewed as a partial order on the set of processes that comprise the algorithm. The relation of the partial order is the "precedes" relationship [21]. Thus, two processes are said to be concurrent if they are incomparable with respect to that relation. Dynamic computations can be divided into bounded computations, where a bound on the total number of processes can be determined, and unbounded computations, where there is no limit to the number of processes that might be spawned. Because of non-determinism, computations generated by the OM execution model are of the unbounded type. The AND/OR tree is the canonical graph-representation of the computation. This motivated us to study graph-theoretic algorithms that embed dynamically evolving graphs into graphs of interconnection networks, and use their ideas in devising tailored process allocation algorithms for OM.

## Algorithms for Mapping Dynamic Trees onto Hypercubes

There has been considerable interest in mapping tree computations to a variety of target architectures. The motivation being that tree computations are generated by many programming techniques such as divide and conquer and backtracking.

Recently, two randomized algorithms were presented for embedding dynamically evolving trees in hypercubes [2], [22]. The algorithm introduced by Batt and Cai embeds a dynamically growing binary tree of unbounded size in the hypercube [2]. Their algorithm maintains an M vertex binary tree dynamically on an N node hypercube with dilation  $O(\log\log N)$  and with probability  $1-\frac{1}{poly(N)}$  no processor has more than  $O(1+\frac{M}{N})$  processes. This means that the constant load property and the bound on the dilation are

independent of the size of the tree. Thus, the algorithm is general enough to handle trees whose size cannot be predetermined. The probabilistic component of the algorithm is the step that handles spawning new processes. This is done by taking a short random walk and allocating the subtree whose root is the new spawned process to the subcube starting at the destination of the walk.

The random walk is constructed by choosing the next dimension to walk along at random, i.e., with probability  $\frac{1}{n}$ , where n is the dimension of the hypercube.

This algorithm can be classified as a preset algorithm and is very much topology dependent, since it was designed specifically to map binary trees to hypercubes and the properties of both are utilized in the analysis of the algorithm. We will later discuss how to generalize the algorithm to work on other architectures with reasonable performance. It is also clear that the algorithm is sender-initiated since a walk is initiated only when a new process is spawned. It is important to note that the algorithm maintains constant load only if the number of nodes in the tree is of the same order of magnitude as the number of nodes in the hypercube N, i.e., if  $M = C \times N$ , where C is a constant.

The algorithm also prohibits process migration since it is observed that no control over dilation can be guaranteed if process migration is allowed.

The second interesting algorithm is the one proposed by Leighton, Newman, and Schwabe, where their goals are to achieve constant dilation, and maintain constant load with high probability [22]. The assumptions they made were that the upper bound on the number of nodes in the tree must be N, i.e., the number of nodes in the hypercube.

The algorithm is also randomized and in some sense constructs a random walk similar to that of [2] but the use of randomness is different and the walk length is dependent on the depth of the node in the tree and the maximum allowed dilation b. In their algorithm, the candidate dimensions traversed by the walk depend on b and the depth of the node in the tree, where each candidate dimension has a probability of 0.5 of being actually traversed in the walk. The basic result of the algorithm is that any star centered at a node x in the hypercube will get at most O(n) tree nodes mapped to it, where a star centered at node x is defined to be the set of nodes consisting of the n neighbors of x and

x itself (where n is the dimension of the cube).

A very important result obtained by [22] is that no deterministic algorithm can achieve constant load without having a dilation of  $\Omega(\sqrt{\log N})$ .

#### Observations

It is important to note that both algorithms have preset strategies that are always applied independent of the system state. This also complies with the results from distributed systems load balancing algorithms, where it was shown that preset algorithms are better than complex adaptive ones with high overhead. Another similarity is the observation that both algorithms use sender initiated strategies for handling newly spawned processes.

The similarity between the results obtained here and those obtained in the distributed systems work indicates that the issues involved in both fields are very similar and thus we believe that research in mapping algorithms to multicomputers should benefit from previous work on load balancing algorithms for distributed systems. This study is one such attempt.

#### Performance Metrics

Both algorithms considered load and dilation as their performance metrics. In both algorithms, one metric is good in the deterministic sense while the other is good in the probability sense. Clearly, it is impossible to achieve optimal or even good performance according to both metrics deterministically since the two goals are often conflicting and thus improving one will tend to worsen the other. A trivial example is the case when all the processes are mapped to the same processor which obviously makes the dilation zero. However the load of the mapping is maximum, i.e., no load balancing is achieved. The opposite extreme case is when every processor has an equal number of processes mapped to it. In most cases such a mapping will have high dilation.

The degree of parallelism is another metric which we believe is also vital in the overall performance of a parallel algorithm especially those whose computation graphs are

trees. This metric is especially valuable in precedence constrained computations such as the dynamically evolving AND/OR trees where the notion of time is natural and apparent. The following is an example that illustrates the value of this metric. Consider the case when two processes that are completely independent, i.e., can run in parallel, for example, processes that are in different subtrees, get allocated to the same processor. They will have to be time multiplexed and the time of the computation is at best doubled (see Figure 1).

Figure 1: An Example of Contention in a Mapping

Thus, we believe that an algorithm that tends to achieve a good compromise between these metrics is highly likely to be superior in the overall completion time metric. One possibility for achieving the compromise between the metrics is to use a weighting function that incorporates all the conflicting performance indices.

#### User Guided Process Allocation

The parallel programming field is now mature enough that there exists a large body of parallel algorithms that were initially designed to be executed on parallel machines, as opposed to the previous trend of parallelizing existing sequential algorithms.

A common property in most of these originally parallel algorithms is that they usually explicitly specify what constitutes a process and do not leave it up to the implementation environment to partition the code into tasks that can be run in parallel. It is

also noted that a cognitive model such as a process graph is almost always employed in the design stage of the algorithm and most probably in its analysis.

We believe that only specifying the processes is not sufficient to efficiently execute parallel programs. It is also necessary to provide additional information that will help the compiler (and any additional software components involved) make the right decisions concerning the execution of the parallel program on the target architecture. It is clear that among the most important and vital information that should be provided is the mapping-relevant issues such as communication patterns and phase behavior.

This approach has been adopted by several researchers in academia, and has resulted in the development of a few configuration languages such as Conic [28], GDL [4], and LaRCS [26], [25]. Most of these languages are based on a graph model as the canonical representation of the program. These languages are intended to aid the programmer in describing the configuration of the processes in the program and their communication and execution characteristics. Such information could be utilized by the mapper-compiler combination to make informed allocation decisions.

We believe that if the programmer is to be allowed to describe extra-logical features of her/his program such as the execution and communication patterns, such an approach might well be used in parallel logic programming also. In other words, the programmer would write her/his normal parallel logic program in OPAL, and separately describe its characteristics in a configuration language. Both programs would be fed to the corresponding compilers and then linked together to form a load module. The linking phase should provide information for the process allocator so that it could make intelligent decisions at run time based on the information supplied by the programmer in the configuration program.

#### Conclusions

This chapter addressed the process allocation problem from a graph embedding perspective. A couple of recent algorithms that embed dynamically evolving trees on hypercubes were presented. Some generalizations to these algorithms to work on generic

architectures and generic AND/OR trees will be discussed in a later chapter. We also presented some ideas as to how to incorporate dynamic mapping information in the LaRCS configuration language. This would be of interest if annotations are to be employed in logic programming systems.

#### CHAPTER IV

#### LOAD BALANCING IN PARALLEL LOGIC PROGRAMMING

#### Introduction

Researchers in the parallel logic programming (PLP) area have recently started addressing the problem of process allocation and load balancing in the context of available PLP systems. Until very recently most PLP systems have been built around an off the shelf generic process allocation algorithm. This was encouraged by the fact that a large body of load balancing algorithms were available, and it was usually an easy task to select one which would yield acceptable performance on the average. However, clearly there was no global consensus on what acceptable should denote as most of these algorithms were heuristics. Recently, researchers started addressing the problem of designing tailored process allocation algorithms for parallel logic programming execution models. In this chapter, we will survey those research efforts in the context of message passing parallel logic programming systems and evaluate each of the presented algorithms according to the criteria presented in chapter II.

## The Processing Power Plane

A processing power plane (referred to as PPP) is an abstract model that is intended as an intermediate level between the physical hardware and the application programs [33]. The motivation of the PPP is to provide means for modeling communication cost without exposing the details of the architecture to the application programs. Thus, somehow, the distance between the physical processors had to be incorporated in the PPP. This led the designers to modeling the physical structure of the architecture by considering the system to be an N-dimensional cube in which computing power is uniformly distributed. Since the algorithm was designed to be implemented on the Multi-PSI/v2 architecture, a loosely

coupled multiprocessor system with a 2-dimensional mesh interconnection network, N was chosen to be 2. The model is a 2-dimensional cube, i.e., a plane, hence the name processing power plane. We note, however, that this model assumes a homogeneous architecture where all the processors are identical and would not accurately model a heterogeneous system.

The algorithm breaks up the allocation process into two consecutive stages. The first stage is allocating the process to a certain location on the processing plane. The second stage is the actual allocation of the processing plane to the physical processor. The load balancing phase takes place at the level of each PPP. Finally, a dynamic reallocation phase makes localized enhancements based on collecting local load information.

#### · Load balancing on the PPP level

Since the algorithm uses the notion that the size of the rectangle allocated to the process determines how much computation power is given to that process, some estimate of the computation power needed by each process is required. The designers rightly state that such information might not always be feasible to specify. However, one proposal was to have the user provide this information as an annotation to the program For example, for Prolog-like languages, an example of such annotations is:

$$p : \neg \leftarrow (2 * q), \rightarrow r.$$

This specification states that the plane given to the predicate p is subdivided for q and r and that the subgoal q should be given twice as large a subplane as the subgoal r. Clearly, when such information can not accurately be provided, the user can give relative estimates as to how much power each process needs. One reasonable approach to estimating this is the size of the arguments to the goal.

Load balancing on the Physical level

The PPP must be covered by the physical processors in the system for the program to be executed. For optimal load balancing, every processor in the system should be responsible for an equal area of the PPP. This, however, might not be the case, as some areas of the PPP might get more load than others, in which case, appropriate adjustments to the size of the PPP region each processor is responsible for should be made. Processors responsible for dense areas should narrow their regions, whereas those responsible for sparse areas should widen theirs.

The authors point out the following example in which physical proximity on the PPP is not preserved in the mapping to the architecture which causes higher communication overhead. Consider the case where a process is allocated near the boundary of the region allocated to a certain processor and it communicates very frequently with another process allocated on the opposite side of the boundary. Although these processes are almost adjacent on the PPP, the cost of their communication will actually be much higher than the communication between that process with processes that are incident on the same processor. The problem here stems from the fact that physical proximity on the PPP was not preserved on the architecture. The distance between the processes on the PPP was stretched when mapped onto the architecture. This is exactly analogous to the dilation we defined in our graph model. The authors mention that some randomness in mapping the PPP to the physical processors might be useful in alleviating this problem.

The reallocation stage is best done by having a centralized controller that would attempt to achieve a better balance of the load on each processor. However, this clearly would require gathering a huge amount of global information which entails an enormous number of messages exchanged between all the processors and that controller. Moreover, such a centralized controller clearly makes the system non-fault-tolerant and is itself a bottleneck. Therefore, a simpler localized scheme was chosen to do the reallocation. Each corner point between every four processors acts as the reallocation pivot, where messages are exchanged between the four processors to determine the load of each processor and how load balancing could be achieved amongst them. This process repeats for every corner point in the PPP until computational load diffuses throughout the plane.

# The PPP Algorithm on the Multi-PSI

We will briefly describe the architecture of the Multi-PSI machine as it is the target architecture for the PPP algorithm and the following one. It is also one of the primary computing resources that was developed by the fifth generation computer systems (FGCS) project. The Multi-PSI is a loosely coupled MIMD machine that has a 2-dimensional mesh interconnection network. The machine can have up to 64 processors in an 8 × 8 network. The processors are those of the PSI-II. The machine was basically designed to run the concurrent logic programming language KL1. KL1 is based on Flat GHC augmented by metaprogramming and pragma facilities. In fact, the operating system of the machine, PIMOS, is wholly written in KL1. The performance of the Multi-PSI is measured in terms of reductions per second (RPS) where a reduction is a logical inference step.

Flat GHC is a concurrent logic programming paradigm that deviates from the pure logic programming model by assigning a set of guards for each clause. Note that only input unification is allowed for the guards. Once a guard succeeds, the procedure commits to the solution obtained by the clause, and no backtracking is allowed. Thus a typical clause looks like the following:

$$H(X_1, X_2, \ldots, X_k) : -G_1, G_2, \ldots G_m \mid B_1, B_2, \ldots B_n.$$

Input unification means that if any argument  $X_j$  is a constant, it must match a corresponding constant in the call. In Prolog  $X_j$  may unify with a variable, but this "outputs" the constant to the calling environment, which is not allowed in FGHC.

An algorithm based on the PPP model described above was implemented on the Multi-PSI/v2 architecture. The algorithm uses the notion that throwing a goal basically amounts to sending a packet to the PE responsible for that point on the PPP where the goal is allocated. Had the goal thrower PE known the entire mapping of the PPP to the physical PEs determining the destination PE would have been trivial. However, as such global information is costly to gather, the designers developed an incremental packet transmission algorithm that uses local information, together with the hardware mechanism

to implement the algorithm using table look-up. We will not go into the details of these schemes as they are irrelevant to our discussion. The interested reader is referred to [33].

The authors note a few problems with the implementation among which the following are the most relevant to our perspective:

#### • Network deadlock

Since a packet may follow any direction at any given node in the network, potential network deadlock is possible. The use of a deadlock-free routing algorithm, however, would restrict the freedom of the direction of movement of packets. The authors note that since the network has a finite longest path, a deadlock-free network architecture with a packet-pool buffer could have been used. For a larger scale machine, more efficient algorithms will be required.

### • Load Measurement

The authors, rightly, note that their notion of "load" is not accurate and propose that a better approach might be to assign priority values to processes and use the sum of such values of processes executed per unit time as a measure of load.

In addition to the self-criticism presented by the authors of the algorithm, we will evaluate it in light of the classification criteria we introduced in chapter II.

# Sender initiated or receiver initiated

This algorithm can not be classified as being sender initiated or receiver initiated per se as the mapping of each process (goal) to a location on a PPP is done at compile time. At run time, whenever a goal is thrown to be solved, all is required is to determine which processor that location on the PPP was allocated to. Thus in some sense the allocation is static or compile-time and only reallocation enhancements are dynamic or run-time. Hence, the algorithm is independent of the sender vs receiver initiated criterion.

### Not fully distributed

The algorithm is not fully distributed and the initial allocation of the processes to the

PPP was not said to be done in parallel. Hence, a centralized processor is assumed to be responsible for that stage. Also, the goal thrower seems to be a dedicated PE that would be responsible for determining which goal is to be solved next and sending it to the array where the packet transmission algorithm ships it to its final destination PE.

#### • Randomized

Randomness was said to be incorporated at the level of mapping the PPP to the physical processors.

# • Architecture independence

This algorithm is not architecture-independent as it assumes a homogeneous architecture. It also has the mesh interconnection built into the packet transmission algorithm and it relies on custom hardware that would make the realization of the localized packet transmission algorithms feasible. However, we believe that the main scheme of the PPP could be incorporated in any MIMD machine, assuming routing algorithms exist that are capable of implementing the packet transmission algorithms. The existence of some sort of a host that would act as the goal thrower and would perform the initial process allocation to the PPP is also assumed. This latter assumption, however, is reasonable and realistic enough as most commercially available MIMD machines have such a host node.

## Process migration

Since the reallocation stage is done dynamically (i.e., at run time) it is effectively doing process migration. Thus, it constitutes high run-time overhead due to the transfer of process tables and structures from one processor to the other over the interconnection network.

# Multi-level Load Balancing

The Multi-level load balancing algorithm was designed specifically for OR-parallel exhaustive search programs [13]. The target architecture for which it was designed was also

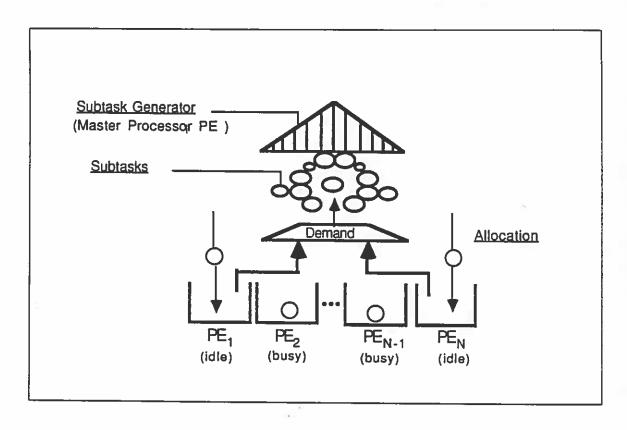

the Multi-PSI machine. However, the algorithm is claimed to be architecture-independent. The main idea of the algorithm is to partition the program into mutually independent tasks (subtask generation) and then distribute those subtasks to the physical processors (subtask allocation).

The multi-level load balancing algorithm was arrived at as an extension of a onelevel scheme that simply used one master processor as the subtask generator that generates subtask to be distributed to the other slave PEs in the system. However, it was clear that the subtask supply was the bottleneck of the system as the number of processors in the system increased. Hence, a natural solution to alleviate that problem was to incorporate more subtask generators.

The multi-level algorithm divides the processors into groups, each with its own subtask generator, and attempts to balance the load at both the group level and the processor level. The generated subtasks are allocated to the PEs according to the task allocation strategy.

A "super-subtask" generator is allocated to one master PE which divides the program into super-subtasks until the search reaches the first distribution level. The super-subtask generator distributes super-subtasks to M group masters which will act as subtask generators. Each group master is responsible for a fixed number of processors whose number is  $\frac{N}{M}$  where N is the number of processors available in the system. The first level of distribution is the distribution of super-subtasks to idle group masters to balance the load across processor groups (PG). The second level is the load balancing within a group where subtasks are distributed to idle PEs (see Figure 2). As mentioned earlier, the algorithm was motivated by the idea of avoiding the subtask bottleneck by keeping the number of processors competing for subtasks small. However, if N becomes increasingly large, a potential bottleneck can still occur within groups, in which case, more distribution levels should be introduced. Clearly, it is this hierarchical scheme that makes the algorithm scalable and hence portable to families of architectures.

The allocation strategy is basically a simple receiver initiated (or on-demand) strategy. Idle PE's send a demand message to the subtask generator which in turn distributes

Figure 2: Subtask Distribution in the Multi-level Algorithm (from [13])

tasks to the idle PE's which execute these tasks and then send a new demand message upon completion of their tasks.

A technique called group merging is employed to handle the situation when a group of processors become idle because they finished executing their subtasks whereas other groups are still busy. Clearly, such a situation arises as a result of load imbalance at the super-subtask level. The situation is remedied by a scheme that merges idle groups with busy groups to form larger units. However, as groups are merged the subtask generator of the newly formed group is now responsible for feeding a much larger number of processors which creates the evil subtask bottleneck.

The algorithm was tested on the all solution exhaustive search program of the Packing Piece Puzzle on the Multi-PSI machine and almost linear speedups were obtained when varying the number of processors.

Analyzing the multi-level load balancing scheme according to the dimensions introduced in chapter II yields the following observations:

#### Receiver initiated

The multi-level algorithm is receiver initiated. A study by Eager et al [10] showed that under heavy system load, receiver-initiated strategies perform better than sender-initiated strategies. This result complies with the measurements taken from the performance study that was conducted to test this algorithm. In fact, since this algorithm is targeted towards exhaustive search OR-parallel programs, we believe that it was a very clever design decision to use a receiver-initiated strategy.

#### Randomness

When several processors are idle and requesting work and there are enough subtasks for all of them, randomness could be used as the arbitration scheme.

#### Not fully distributed

This point is of great interest here, since the algorithm is distributed when you take the viewpoint of the processor masters alone and view the PEs in the processor groups as simply the computational power of the masters. However, if one takes the global view of the system, then clearly the group masters constitute centralization points which are vulnerable points in terms of faults, since a breakdown at one of the master PEs would freeze all the PEs in the processor group controlled by that master.

# • Architecture independence

The algorithm is fairly architecture independent since no knowledge of the architecture was employed at any point in the distribution scheme. While group merging is influenced by the mesh interconnection, we believe that it could very easily be modified in order to group the processors in a different fashion that is independent of the topology of the network, for instance, grouping the one-away neighbors of an idle group.

## • Process migration

It is not explicitly stated whether process migration is permitted when processor groups are merged or not.

# Load Dispatching Strategies for the Parallel Inference Machine

Another machine built as part of the Japanese fifth generation computer systems project is known as the Parallel Inference Machine (PIM). The PIM is a message passing MIMD machine that is currently under construction. Similar to the Multi-PSI, the PIM also executes programs written in the KL-1 language. Load balancing strategies for the PIM are described in this section.

The PIM has an interesting hierarchical architecture that in essence resembles that of the  $cm^*$ . The bottom level is made of the individual PEs. The next level up is called the cluster-layer, where a cluster is a group of tightly coupled PE's. The third level is the bunch layer, where a bunch is a group of loosely coupled clusters. The top level is the integration layer where an integration is a group of bunches.

The machine that was actually being built had only a 2-layer hierarchy, i.e., up to the bunch layer. There were 10 clusters interconnected using an equal length network such as a cross-bar switch. Each cluster had 10 PEs coupled tightly through shared memory and caches.

Several algorithms for load dispatching on the PIM have been presented [31]. The algorithms are basically influenced by two main ideas: first, anticipate idle targets to dispatch load to, and second, stop load dispatching when conditions are not appropriate, such as the sender becoming idle as a result of the dispatch or if the target is much more overloaded than the sender.

All the algorithms were tested using simulations on a virtual machine emulating the PIM. The main results in the paper are drawn from one test program, the 6-Queens program; however similar results were reported to be obtained from running the algorithms on two other parsing programs.

Four strategies were used:

- Strategy A: The clusters to which goals are dispatched is determined totally at random.

- Strategy B: The cluster with the minimum ready goals is chosen as the target of the dispatch. This strategy uses the number of processes in the ready queue as an estimate of the load.

- Strategy C: Same as strategy A but the dispatch is aborted if the target cluster

has more ready goals than the dispatching cluster. As the authors do not specify

whether the dispatch is retried in hope of obtaining a different target, we assume

that once aborted the task would simply be allocated locally.

- Strategy D: The cluster with maximum ready goals dispatches to that with minimum ready goals. This strategy requires global information about the load of all the clusters in the system.

A minor modification is also made to strategies B and C, resulting in strategies B' and C'. The modification is that before dispatching is started, the load of the dispatching cluster is first compared to a threshold minimum below which dispatching is aborted.

Dispatching while the load is below the threshold might result in the dispatching cluster becoming idle very soon. Analytical or statistical analysis to determine this threshold value was not provided

The goals of the authors were to minimize the parallel processing overhead and to maximize the processor utilization. The parallel processing overhead is defined to be the overhead due to the suspend/resume processes that are supported in KL-1. Recall that processor utilization is the ratio of the processor's busy time to the total time of execution of the program. It is interesting to note that both these factors depend on the load granularity in conflicting manners. For instance, the finer the granularity, the higher the processor utilization, and the higher the parallel processing overhead also. On the other hand, the bigger the grain size, the lower the parallel processing overhead, and the lower the processor utilization. Note that these factors are much more significant at the bunch layer (i.e., between clusters) than at the cluster layer (i.e., between PEs). Inside a cluster, load balancing can be achieved using frequent inexpensive communication. Also the shared memory can be be used for storing the queue of ready processes, which decreases the cost of suspension and resumption.

criterion that the authors used was the load dispatching rate, which is defined as the ratio of all goals dispatched to the total number of reduced goals. Their definition of granularity is that it is the reciprocal of the load dispatching rate. Clearly, at high load dispatching rates, the parallel processing overhead dominates the processing time, whereas at low dispatching rates, utilization is higher.

the following properties:

#### Sender initiated

The authors deliberately made the decision that the algorithms be sender initiated as they claim that for a large scale PIM (i.e., with more than 100 processors) the communication overhead due to broadcasting load requests would place severe requirements on the channels. This decision was influenced by the architecture rather than the nature of the application programs (i.e., OR vs. AND parallelism) as was the case in the other efforts.

## Randomness

The authors incorporated randomness in determining the target of the allocation in all algorithms. In fact, strategy A is a blindly random one. This, we believe, is well in accordance with the decision to use sender-initiated allocation.

## • Fully distributed

The algorithms are fully distributed as all clusters execute the same allocation routine whenever a new process is spawned. The algorithm is fault-tolerant and insensitive to failures at the cluster level.

## Process Migration

Once a process is allocated to cluster, it is not allowed to migrate to other clusters. This was also motivated by the cost of communication across clusters.

# Architecture independence

While several of the design decisions that influenced the algorithms were motivated by the architecture, the resultant algorithms are very architecture independent and could be very easily run on various architectural platforms.

ideas might be interesting extensions to the PIM load balancing schemes:

# Hierarchical load balancing

The idea here is to incorporate the multi-level load balancing scheme, as the clusters lend themselves very naturally to the concept of processor groups. Thus one processor in each cluster would serve as the subtask generator for the rest of the PEs in that cluster and try to balance the load within the cluster.

# Hybrid load balancing

While sender initiated strategies might be good for inter-cluster load balancing, a receiver-initiated strategy might very well be more appropriate within clusters since the cost of communication is much less and hence broadcasting load information would not be intolerable. Within the cluster, a receiver initiated strategy such as that reported in the multi-level load balancing algorithm might be more powerful

for intra-cluster load balancing. We will pursue this idea in one of the algorithms devised for OM to evaluate whether the performance of a hybrid strategies warrants their extra overhead or not.

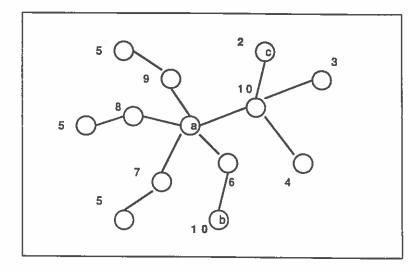

# Contracting Within Neighborhood

been tested in a real setting and on more than one despite the fact that they are still toy programs. An algorithm known as contracting within neighborhood is used in the Chare-Kernel which is the base implementation on top of which the Reduce OR model is implemented [18]. The algorithm was first proposed in [19] and has been extensively modified and extended to be responsive to system changes in [30]. The original algorithm is called the Naive Contracting Within Neighborhood (NCWN), while the new adaptive version is called ACWN.

The NCWN algorithm is sender initiated and attempts to localize communication as much as possible by avoiding communication between non neighboring processors. The motivation is that such communication is not scalable and would tend to make the cost of communication overhead dominate the performance. Henceforth, we will use our generalized notion of a "star" to refer to the immediate neighbors of a processor.