# MAPPING PARALLEL ALGORITHMS TO MESSAGE PASSING MACHINES

by

# XIAOXIONG ZHONG

# A DISSERTATION

Presented to the Department of Computer and Information Science and the Graduate School of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

June 1994

"Mapping Parallel Algorithms to Message Passing Machines," a dissertation prepared by Xiaoxiong Zhong in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science. This dissertation has been approved and accepted by:

Chair of the Examining Committee

5/28/94 Date

Committee in charge:

Dr. Virginia Lo, Chair

Dr. Sanjay Rajopadhye

Dr. Andrzej Proskurowski

Dr. Evan Tick

Dr. Brad Shelton

Vice Provost and Dean of the Graduate School

An Abstract of the Dissertation of

Xiaoxiong Zhong

for the degree of

Doctor of Philosophy

in the Department of Computer and Information Science

to be taken

June 1994

Title: MAPPING PARALLEL ALGORITHMS TO MESSAGE PASSING **MACHINES**

Approved: Virginia M. Lo

Message passing machines provide an opportunity to achieve high performance for applications such as those in scientific computing, in digital signal processing, in simulation and in electronic design automation. Programming such architectures to achieve high performance, however, poses a challenging task to users. One of the major problems is to design a mapping (assignment) scheme for processes to deal with the mismatch between the ideal communication structure for the parallel algorithm and the target architecture. The research in this thesis aims at this problem. In the thesis, two kinds of architectures, multicomputers and systolic arrays, are considered.

In the first part, we concentrate on communication issues in the design of mapping algorithms for a multicomputer. As communication switching technologies advance, major factors which incur communication overhead have changed and should be studied. We empirically study the effect of communication overhead caused by the topological mismatch in a multicomputer Empirical case studies are carried out to qualitatively characterize the impact of several important mapping metrics and architectural factors on the performance of benchmarks. To quantify communication overhead, we study and validate analytical estimation formulae for message latency. The applications of the message latency formulae to a general purpose multicomputer simulator are discussed and a new parallel program performance evaluation framework is proposed.

We then study the problem of reducing communication overhead by utilizing knowledge of the message passing requirement in an application. We propose efficient application-specific routing algorithms to reduce communication overhead. The proposed techniques can be applied to parallel programs with intensive communication on a multicomputer with user-controlled routing capability.

In the second part, we study the problem of mapping a class of algorithms called regular iterative algorithms to systolic arrays. First, the problem of finding an optimal time schedule for regular iterative algorithms is studied. Second, we propose a systematic method to enumerate linear allocation functions to yield spatially regular systolic arrays with some permissible connection constraints. Such a method can be used to design systolic arrays based on various optimization criteria. Finally, we show how to improve efficiency of a systolic array to an almost 100% efficient array by using a quasi-linear transformation function. The results have potential applications in a high level synthesis system or in a silicon compiler.

#### CURRICULUM VITA

NAME OF THE AUTHOR: Xiaoxiong Zhong

PLACE OF BIRTH: Guangdong, China

DATE OF BIRTH: November 27, 1963

#### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon Fudan University, China

#### DEGREES AWARDED:

Doctor of Philosophy in Computer and Information Science, 1994, University of Oregon

Master of Science in Computer Science, 1986, Fudan University, China

Bachelor of Science in Computer Science, 1983, Fudan University, China

#### PROFESSIONAL EXPERIENCE:

Lecturer, Department of Computer Science, Zhongshan University, Guangdong, China, 1986-1989

Graduate Teaching and Research Fellow, Department of Computer and Information Science, University of Oregon, Eugene, 1989-1993

Senior Software Engineer, Zycad Corporation, Fremont, California, 1993-1994

#### ACKNOWLEDGEMENTS

I wish to express my deep appreciation and thanks to my advisors Dr. Ginnie Lo and Dr. Sanjay Rajopadhye for their continuous support and encouragement. The guidance, care and understanding from Ginnie have always been a major source of strength for me. Working with Sanjay has been stimulating. I am grateful to Dr. Evan Tick for his help, motivation, and advice. His detailed corrections and comments greatly enhanced the quality of this thesis. Dr. Andrzej Proskurowski has been very supportive during my stay at the University of Oregon and I am very thankful for all his help. I thank Dr. Brad Shelton for taking time to be on my committee.

I am also grateful for the support from Zycad Corporation. The encouragement my manager Ramesh provided me in the last few months has been very helpful in finishing my dissertation.

I thank my graduate fellows A.V.S.Sastry, Jan Telle, and many others for their help. I thank our graduate secretary Betty Lockwood.

My friend Norman Lumian has made my stay in Eugene enjoyable and interesting.

The care and understanding from my parents and sisters in China have been important to me. My wife Wensheng has always been behind me during this long and sometimes difficult journey. This would not have been possible without her understanding and support.

# TABLE OF CONTENTS

| Chapt | ter                                                                                                                                                                                                                                             | Page                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| I.    | INTRODUCTION                                                                                                                                                                                                                                    | 1                                            |

|       | The Mapping Problem                                                                                                                                                                                                                             | 2<br>5<br>8                                  |

| PAR   | T I. COMMUNICATION ISSUES IN MAPPING TO MULTICOMPUTE                                                                                                                                                                                            | ERS                                          |

| II.   | MAPPING TO MULTICOMPUTERS                                                                                                                                                                                                                       | 11                                           |

|       | Introduction                                                                                                                                                                                                                                    | 12<br>13<br>19<br>24<br>26<br>35<br>36<br>39 |

| III.  | COMMUNICATION OVERHEAD ON A MULTICOMPUTER                                                                                                                                                                                                       | 41                                           |

|       | Related Work  Multicomputer Network Simulation  The Mapping Effect  Message Latency Estimation  Justifying the Formulae  Incorporating the Message Latency Formulae into A Simulator  Applications of the Message Latency Formulae  Conclusions | 41<br>44<br>49<br>69<br>72<br>74<br>76       |

| IV.   | APPLICATION-SPECIFIC WORMHOLE ROUTINGS ON A MULTICOMPUTER NETWORK                                                                                                                                                                               | 80                                           |

|       | Related Work                                                                                                                                                                                                                                    | 81<br>83                                     |

|       |                                                                                            | Page                     |

|-------|--------------------------------------------------------------------------------------------|--------------------------|

|       | Deadlock-Free Low-Maximum Contention Routing                                               | 97                       |

| V.    | AN EFFICIENT HEURISTIC FOR APPLICATION-SPECIFIC ROUTINGS ON A MESH CONNECTED MULTICOMPUTER | 106                      |

|       | Related Work                                                                               | 107<br>114<br>117        |

|       | PART II. MAPPING TO SYSTOLIC ARRAYS                                                        |                          |

| VI.   | SYSTOLIC ARRAY DESIGN                                                                      | 126                      |

|       | Systolic Arrays                                                                            | 128<br>132               |

| VII.  | OPTIMAL SCHEDULES FOR REGULAR ITERATIVE ALGORITHMS                                         | 137                      |

|       | Introduction                                                                               | 138<br>141<br>144<br>151 |

| VIII. | LINEAR ALLOCATION FUNCTIONS FOR SYSTOLIC ARRAY DESIGN                                      | 156                      |

|       | Introduction                                                                               |                          |

| Pa                                                               | age                                                  |

|------------------------------------------------------------------|------------------------------------------------------|

|                                                                  | 187<br>190                                           |

| IX. QUASI-LINEAR ALLOCATION FUNCTIONS FOR EFFICIENT ARRAY DESIGN | 192                                                  |

| Notations and Problem Definition                                 | 192<br>193<br>195<br>199<br>204<br>215<br>222<br>227 |

| APPENDIX                                                         |                                                      |

| A. BENCHMARK PROGRAMS AND SIMULATION RESULTS 2                   | 233                                                  |

|                                                                  | 233<br>245                                           |

| BIBLIOGRAPHY                                                     | 250                                                  |

# LIST OF TABLES

| Table |                                                                                                                                                                                                                                                              | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.    | Contention Metrics for the Reflecting and Growing Mappings of DAQ .                                                                                                                                                                                          | 60   |

| 2.    | Dilation Metrics the Reflecting and Growing Mappings of DAQ                                                                                                                                                                                                  | 60   |

| 3.    | Contention Metrics for the Gray Code and Identical Mappings of FFT                                                                                                                                                                                           | 61   |

| 4.    | Dilation Metrics for the Gray code and Identical Mappings of FFT                                                                                                                                                                                             | 61   |

| 5.    | Performance Comparison Between the Reflecting Mapping and the Growing Mapping of DAQ of Message Size Equal to 8192 Bytes on a Wormhole-Routed System. Column 4 Shows the Ratio of stime of the Growing Mapping over stime of the Reflecting Mapping          | 66   |

| 6.    | Performance Comparison Between the Gray Code Mapping and the Identical Mapping of FFT of Message Size Equal to 512 Bytes on a Wormhole-Routed System. Column 4 Shows the Ratio of the stime of the Identical Mapping over the stime of the Gray Code Mapping | 66   |

| 7.    | Performance Comparison Between the Reflecting Mapping and the Growing Mapping of DAQ of Message Size Equal to 128 Bytes on a Store-Forward Routed System                                                                                                     | 67   |

| 8.    | Prediction vs. Simulation Error for the Wormhole Routing                                                                                                                                                                                                     | 73   |

| 9.    | Prediction vs. Simulation Error for Store-Forward Routing                                                                                                                                                                                                    | 73   |

| 10.   | Prediction vs. Simulation Error for a 2-D FFT on a 64 Node Wormhole Routed System                                                                                                                                                                            | 76   |

| 11.   | Performance of $DFH$ for the Applications                                                                                                                                                                                                                    | 103  |

| 12.   | Performance of $BLOCK$ for the Applications                                                                                                                                                                                                                  | 121  |

| 13.   | DAQ Performance on a 1024-Node Wormhole-Routed System                                                                                                                                                                                                        | 245  |

| 14.   | DAQ Performance on a 256-Node Wormhole-Routed System                                                                                                                                                                                                         | 246  |

| 15.   | DAQ Performance on a 64-Node Wormhole-Routed System                                                                                                                                                                                                          | 246  |

| 16.   | DAQ Performance on a 1024-Node Store-Forward Routed System                                                                                                                                                                                                   | 247  |

| 17.   | DAQ Performance on a 256-Node Store-Forward Routed System                                                                                                                                                                                                    | 247  |

| 18.   | DAQ Performance on a 64-Node Store-Forward Routed System                                                                                                                                                                                                     | 248  |

|   |     |                                                              | Page |

|---|-----|--------------------------------------------------------------|------|

|   | 19. | FFT Performance on a 1024-Node Wormhole-Routed System        | 248  |

| - | 20. | FFT Performance on a 256-Node Wormhole-Routed System $\dots$ | 249  |

| • | 21. | FFT Performance on a 64-Node Wormhole-Routed System          | 240  |

# LIST OF FIGURES

| Figure |                                                                                                                                                    | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.     | An Example of Mismatch Between an Application and a Target Archi-                                                                                  |      |

|        | tecture                                                                                                                                            |      |

| 2.     | Illustration of a Mapping Procedure                                                                                                                | 17   |

| 3.     | Illustration of Flow Control Schemes in a Contention-Free Situation. $$ .                                                                          | 23   |

| 4.     | Deadlock in a Store-Forward Routing                                                                                                                | 27   |

| 5.     | Deadlock in a Wormhole Routing                                                                                                                     | 28   |

| 6.     | Deadlock Avoidance in a Store-Forward Routing                                                                                                      | 31   |

| 7.     | Deadlock Avoidance in a Wormhole Routing                                                                                                           | 33   |

| 8.     | Partitioning of a 2-D Mesh into Four Virtual Networks                                                                                              | 34   |

| 9.     | SEND_PACKET Event Handler                                                                                                                          | 47   |

| 10.    | ROUTE_PACKET Event Handler                                                                                                                         | 47   |

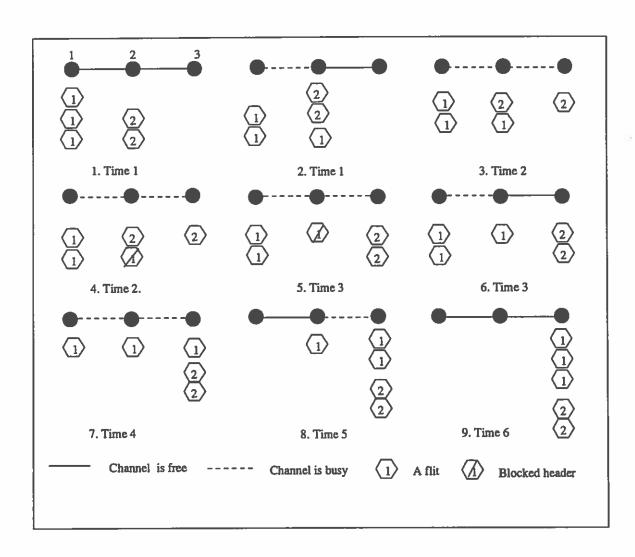

| 11.    | Simulation Steps to Pass a Message from Node 1 to Node 3 and to Pass Another Message from Node 2 to Node 3                                         | 49   |

| 12.    | The State of Each Channel and Physical Time of Each Step to Pass a Message from Node 1 to Node 3 and to Pass Another Message from Node 2 to Node 3 | 50   |

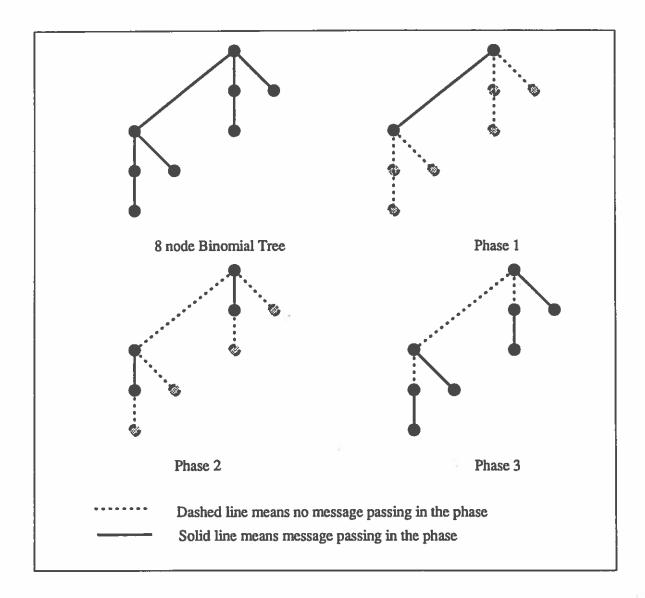

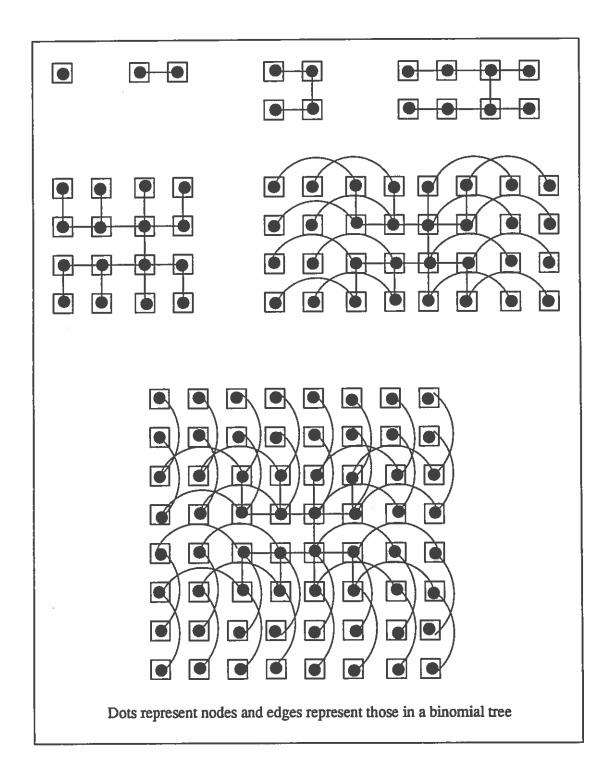

| 13.    | An 8-Node Binomial Tree and Its Three Phases                                                                                                       | 53   |

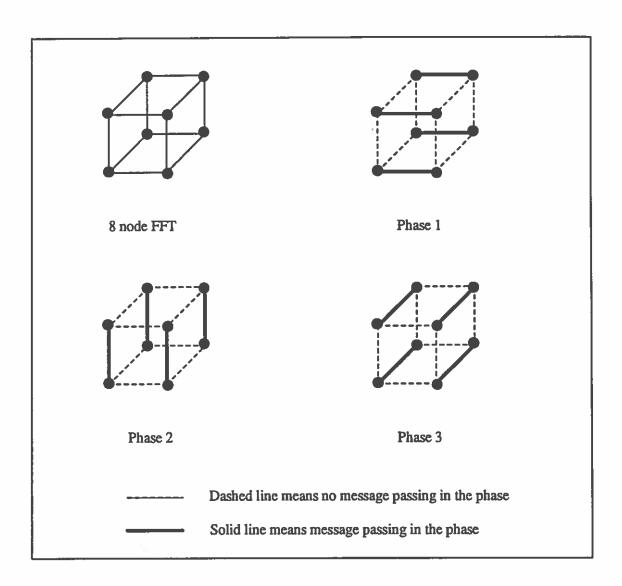

| 14.    | An 8-Node FFT Topology and Its Three Phases                                                                                                        | 54   |

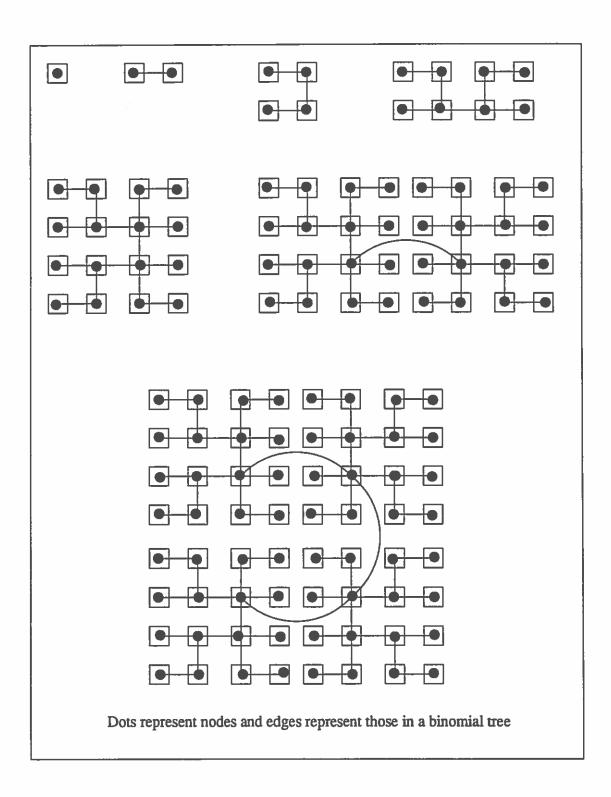

| 15.    | The Reflecting Mapping to Meshes with Size from 1 to 64                                                                                            | 57   |

| 16.    | The Growing Mapping to Meshes with Size from 1 to 64                                                                                               | 59   |

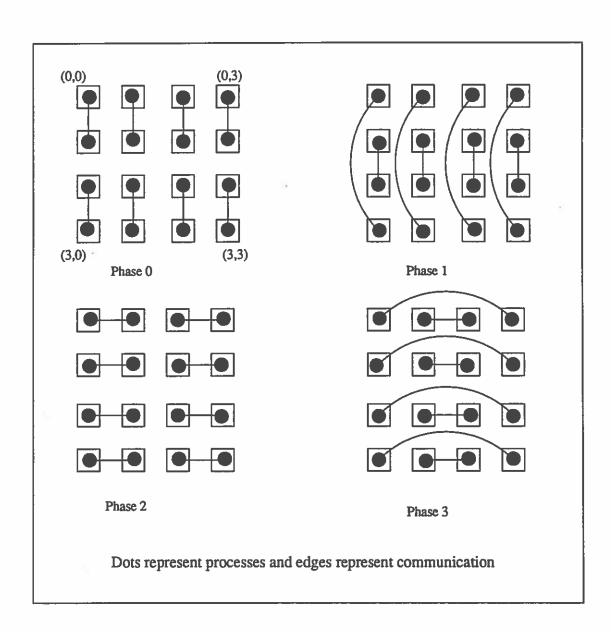

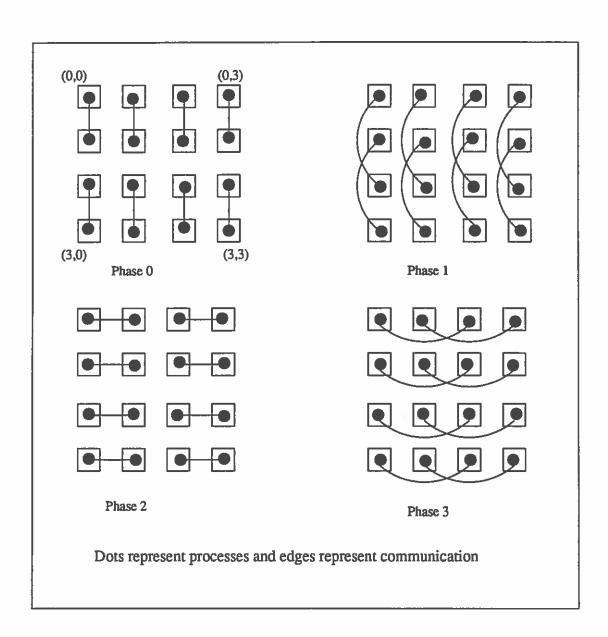

| 17.    | The Gray Code Mapping (Shown by Phase by Phase Communication) to Mesh of Size 16                                                                   | 62   |

| 18.    | The Identical Mapping (Shown by Phase by Phase Communication) to Mesh of Size 16                                                                   | 63   |

| 19.    | XY-Routing for 3 × 3 Matrix Transpose                                                                                                              | 81   |

|     |                                                                                                                                       | Page |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 20. | An Example Where Kandlur and Shin's Algorithm Generates a Deadlocked Wormhole Routing                                                 | 83   |

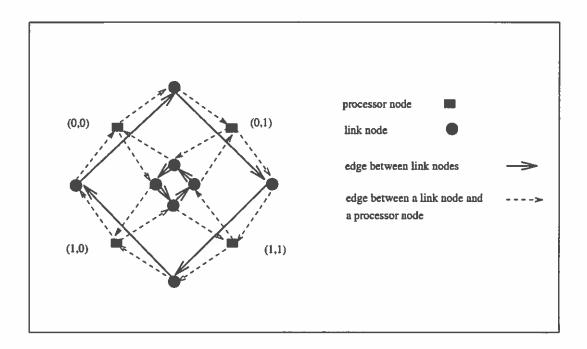

| 21. | The GPCDG of a 2 × 2 Mesh                                                                                                             | 88   |

| 22. | Outline of the Deadlock-Free Heuristic $DFH$                                                                                          | 89   |

| 23. | reroute Function                                                                                                                      | 92   |

| 24. | Updating Functions for a Transitive Closure and deadlock-free-test                                                                    | 94   |

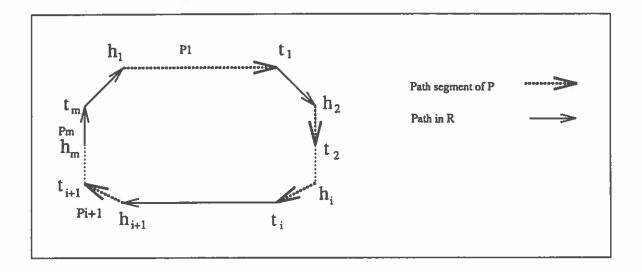

| 25. | Illustration of the Cycle $C$ for the Deadlock-Free Testing                                                                           | 95   |

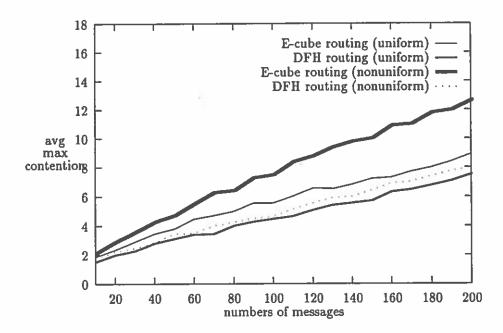

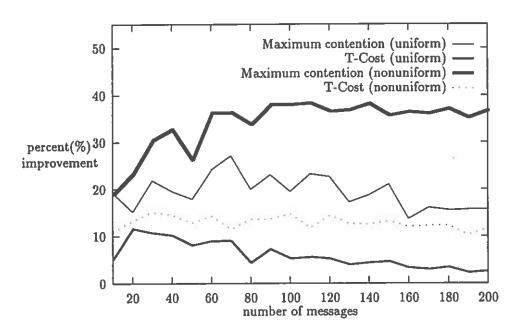

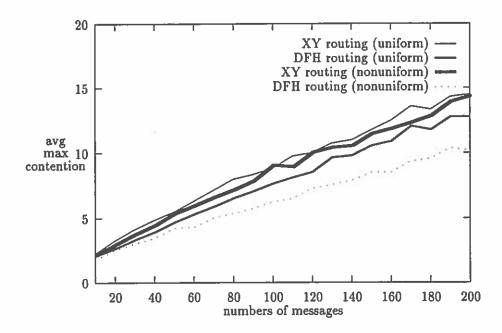

| 26. | Average Maximum Contention for a 5-Dimensional Cube for Both Uniform and Nonuniform Message Distribution                              | 99   |

| 27. | Percentage Improvement of Maximum Contention and T-Cost for a 5-Dimensional Cube for Both Uniform and Nonuniform Message Distribution | 99   |

| 28. | Average Maximum Contention for a 6 × 6 Torus for Both Uniform and Nonuniform Message Distribution                                     | 100  |

| 29. | Percentage Improvement of Maximum Contention and T-Cost for a $6\times 6$ Torus for Both Uniform and Nonuniform Message Distribution  | 100  |

| 30. | The Description of $n$ -Body Problem and Its Task Graph                                                                               | 101  |

| 31. | The Description of AVHTST Benchmark and Its Task Graph                                                                                | 102  |

| 32. | Illustration of the Proof of Theorem 1                                                                                                | 113  |

| 33. | Illustration of the Labeling Scheme in $BLOCK$                                                                                        | 115  |

| 34. | Calculating Freedom Function                                                                                                          | 115  |

| 35. | Outline of Heuristic BLOCK                                                                                                            | 117  |

| 36. | A Simple Example for the <i>BLOCK</i> Algorithm                                                                                       | 118  |

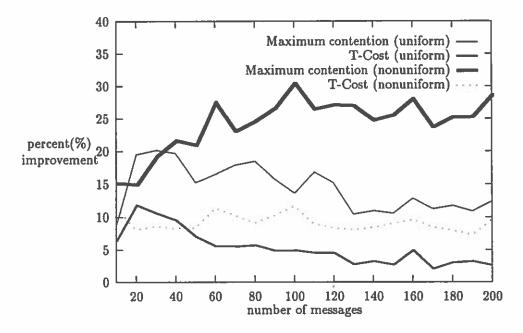

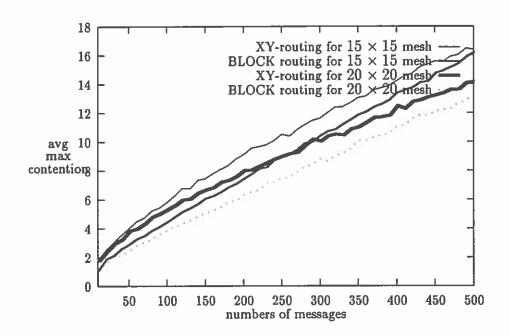

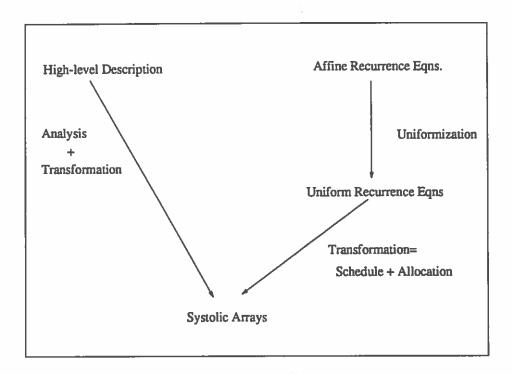

| 37. | Average Maximum Contention for 2-D $15 \times 15$ and $20 \times 20$ Meshes under Uniform Message Distribution                        | 120  |

| 38. | Percentage Improvement of Maximum Contention for 2-D $15 \times 15$ and $20 \times 20$ Meshes under Uniform Message Distribution      | 120  |

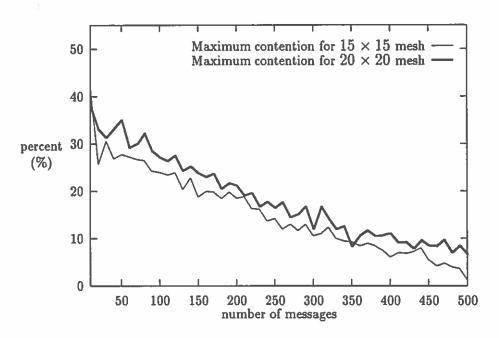

| 39. | Percentage Improvement of Maximum Contention for the Matrix Transpose                                                                 | 122  |

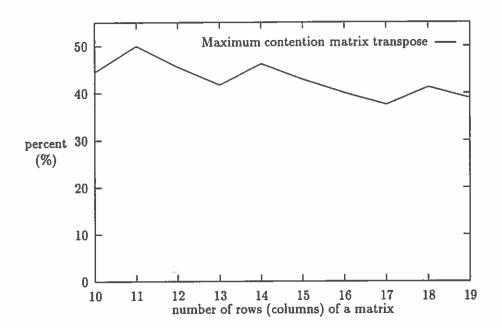

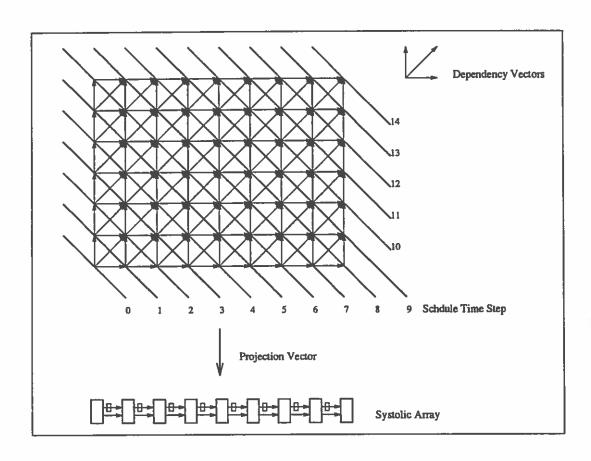

| 40. | Illustration of Systolic Array Design Process                                                                                         | 131  |

| 41. | The Design of a Systolic Array for Convolution Product                                                                                | 135  |

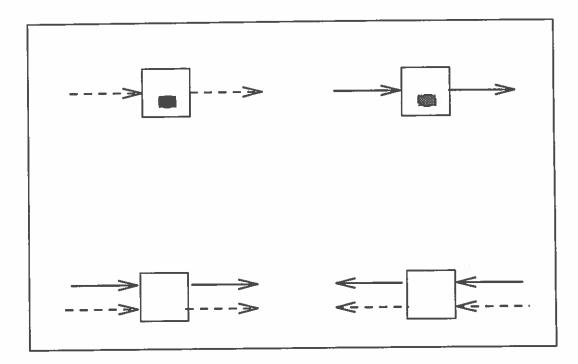

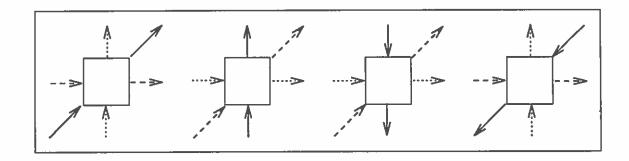

| 42. | The Only Four Linear Arrays That Can Be Derived from a Two-Dimension                                                                                         | al  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Recurrence                                                                                                                                                   |     |

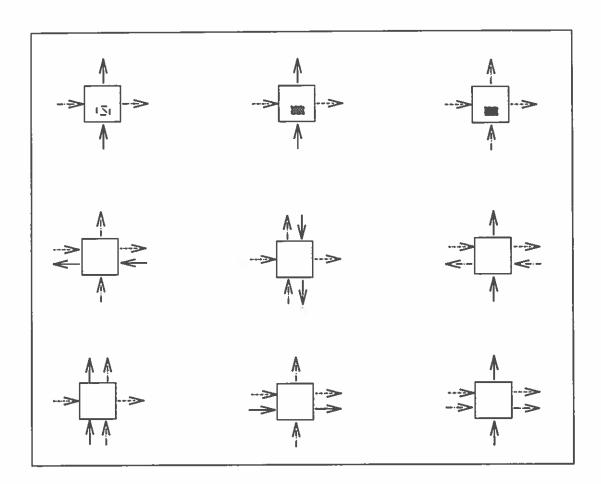

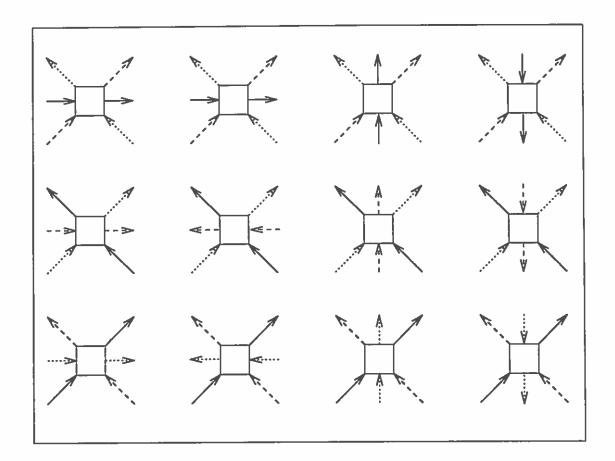

| 43. | All Distinct Two-Dimensional Arrays with Pure Mesh Connections                                                                                               | 175 |

| 44. | Additional Two-Dimensional Arrays If One Set of Diagonals Are Permitted $(\mathcal{P}_3)$                                                                    | 175 |

| 45. | Additional Two-Dimensional Arrays for Eight Nearest Neighbors, $(\mathcal{P}_4)$ .                                                                           | 176 |

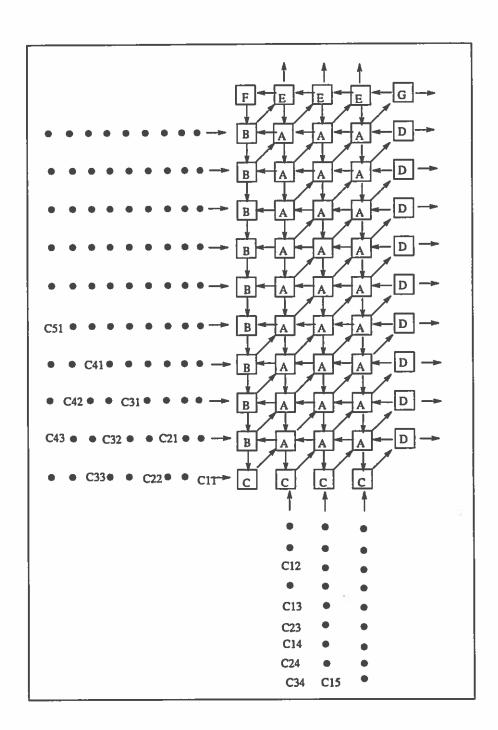

| 46. | Rote's Hexagonal Array for $10 \times 10$ Algebraic Path Problem                                                                                             | 220 |

| 47. | The Final Array for 10 × 10 APP Obtained by Merging Horizontally. A1, C1 and E1 Represent the Processors Merged from Type A, C and E Processors Respectively | 221 |

## CHAPTER I

## INTRODUCTION

Message passing machines are designed for scalable high performance computing. Recent developments in computer architecture as well as communication technology have shown that such machines are highly promising for a broad range of application areas. A message passing machine differs from other parallel architectures in that processes in different processors communicate with each other solely via message passing. The key features of a message passing machine are:

- 1. Processors are physically connected by a point to point network (i.e., direct network). Example networks are hypercubes, meshes and fat-trees.

- 2. Each processor element has its own local memory. No shared memory exists.

- 3. A message passing machine usually has a large number of processors. It can be scaled up to hundreds or thousands of processors.

In this thesis, we concentrate on two kinds of architectures: multicomputers and systolic arrays. Multicomputers are general purpose machines which are best for medium and coarse grain computations, while systolic arrays are application-specific machines which are well suited to fine-grain applications exhibiting massive parallelism. Although the two architectures are different, recent developments have led to the evolution of several machines which represent a hybrid between a multicomputer and a systolic array, as evidenced by the Intel iWarp system [14, 49].

Although the development in hardware of such machines has advanced dramatically in the last few years, software support for these machines has lagged far behind, which is the biggest hindrance to the widespread use of such machines. One of the major difficulties in programming such machines is the mapping problem. The mapping problem involves the mismatch that usually exists between the underlying ideal computation and communication structures of an application and the resources in a target architecture. This is a very important, challenging, cumbersome and error-prone process. It is important because it is vital to performance: a careless mapping may result in poor load balancing and large communication overhead. It is challenging because designing a good mapping may require detailed understanding of scheduling, graph theory, combinatorics and the properties of target architectures. It is also cumbersome since the mapping problem is an extra burden for the programmer in addition to the programming task. Finally, the task of developing a mapping is error-prone due to its complicated nature.

## The Mapping Problem

The performance of a program on a message passing machine is determined by two factors: the inherent parallelism in the program and the overhead incurred by the target architecture to achieve the inherent parallelism. The first factor is determined by the algorithm used in the program. For example, the maximum number of processes which can be executed at the same time may be limited. The second factor is determined by the degree of conflict between the demand for resources required from the program and the available resources of the target machine. In this thesis, we concentrate on the second problem.

The mapping problem [8, 80] can be described as the problem of assigning tasks

to processors and and assigning messages to paths in the target architecture. The programming paradigm used in this research belongs to the communicating sequential process paradigm [52]. More precisely, in this model, a parallel application consists of a set of sequential processes. Processes communicate with each other with explicit message passing. Many programming languages for message passing machines fall into this class [108, 82]. For example, the C programming language supported for the Intel Paragon is a standard C language with extensions for explicit message passing. Other languages or language interfaces which belong to this model include DINO [101] and PICL [42]. Recently, some specialized languages have been designed for the purpose of mapping [9, 81, 7, 8]. Such languages allow a mapping tool to effectively extract useful information needed in a mapping algorithm.

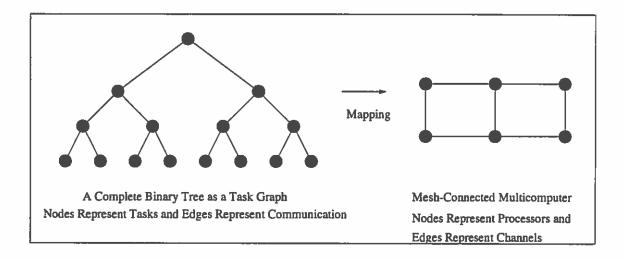

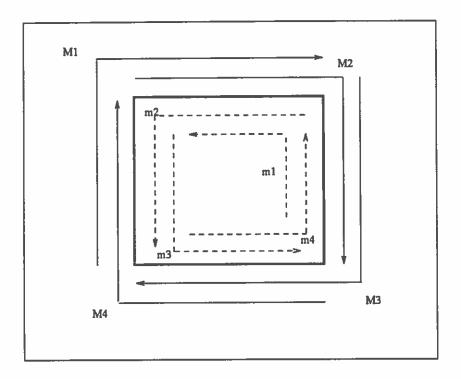

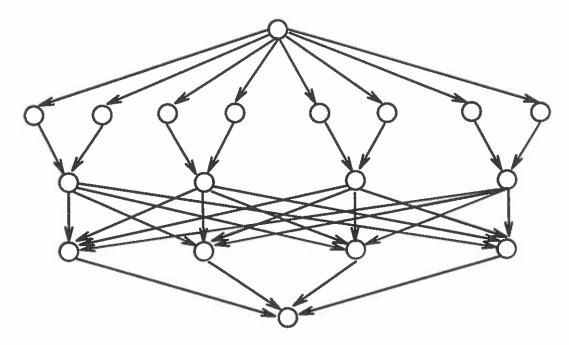

In general, two types of mismatch exist between a parallel application and a target message passing machine [8]. The first is due to the mismatch between the number of processors available in the target architecture and the number of processes in the application. Figure 1 shows an example of an application which is modeled as a complete binary tree and a mesh-connected target architecture. In this example, the number of processes is 16 but there are only 6 processors. To deal with this mismatch, one should be aware of the following factors. First, it is not always true that using the same number of processors as that of processes renders the maximum speedup. This is because communication overhead may seriously degrade the whole computation if the computation grain is too small. Second, if the number of available processors of the target machine is less than that of processes, several processes are forced to be clustered onto one physical processor. How to achieve load balancing and minimize communication overhead in order to maximize performance (or minimize

total completion time) is a difficult problem. Third, even though one is given a sufficient number of processors, some of them may be wasted due to the effect of synchronization. For example, a processor may be idle waiting for messages to arrive. This introduces the concept of efficiency (processor utilization) and a good mapping should try to maximize processor utilization. This problem is related to process scheduling.

Figure 1: An Example of Mismatch Between an Application and a Target Architecture.

The second type of mismatch is due to the difference between the ideal interconnection topology used in the application and the communication network topology of the target architecture. Such a mismatch causes communication overhead since messages are delayed due to long message paths and traffic congestion in the network. To cope with this type of mismatch, one should carefully assign processes to processors so that the topological mismatch is minimized based on various criteria. This step is called process placement. Different communication technologies may cause different communication overhead for the same placement strategy. Thus, the metrics used in

this step should be sensitive to the communication technology used. Furthermore, if the target architecture allows the user to control routing, one can further design an efficient routing for the specific application to reduce traffic congestion after processes have been assigned to processors.

To summarize, a message passing machine can be viewed as a system consisting of two types of resources: processors and communication channels. The mapping problem arises from the conflicting demands for these resources. The first mismatch is due to the conflicting demand for processors and the second mismatch is due to the conflicting demand for communication channels.

## Problems Addressed in the Dissertation

In this dissertation, we study the problem of mapping parallel algorithms to two kinds of architectures, namely, multicomputers and systolic arrays. The thesis correspondingly consists of two parts.

# Part I: Communication Issues in Mapping to Multicomputers

Reducing the topological mismatch in mapping parallel algorithms to a multicomputer has been one of the most important problems for the performance of an application in old generation multicomputers such as Intel's iPSC/1 and Caltech Cosmic Cube [40, 5, 8]. As the communication technologies used in a multicomputer advance, the communication overhead caused by the topological mismatch has been reduced dramatically. Such a change calls for a re-examination of the performance effect of the communication overhead for the new communication technologies. Specifically, we address three fundamental questions to better understand the nature of the communication overhead caused by the topological mismatch.

- Is the communication overhead caused by the topological mismatch still critical to performance under the new communication technologies? For old generation multicomputers which use the store-forward routing scheme, the communication overhead due to the topological mismatch was vital to mapping performance. For new generation multicomputers which use the wormhole routing scheme, however, there has been a claim that the communication overhead may no longer seriously affect performance. Other evidence indicates that the communication overhead continues to be important. A more careful investigation is necessary to resolve this issue.

- What contributes to the communication overhead? In the old generation multicomputers with store-forward routing, key factors such as dilation have been used in the development of mapping algorithms. For the new wormhole routing scheme, we need to develop new metrics to better characterize the communication overhead of a mapping.

- How to reduce communication overhead when designing a mapping algorithm?

We need to develop new mapping algorithms to reduce communication overhead based on the new metrics.

Part I of the thesis focuses on the above issues.

# Part II: Mapping to Systolic Arrays

In Part II, we consider the problem of designing systolic arrays starting from a high-level algorithm expressed as a class of programs called *Regular Iterative Algorithms* (RIAs). Based on well known techniques, the first step in designing a systolic array for RIAs is to schedule computations based on the dependencies in the RIAs,

and the second step is to assign computations of the RIA to physical processors, the so called processor allocation (assignment) problem.

In practice, a systolic array is designed based on various optimization criteria. Among many design criteria [68], the important ones include total completion time, number of processors, and processor utilization. Correspondingly, we address the following three problems.

- Optimal timing schedule to minimize execution time: To minimize execution time for each computation, one would desire to schedule the computation as early as possible with the constraint that the dependencies are not violated. To achieve this, we should investigate the nature of the optimal schedule and how to derive such a schedule.

- Processor allocation based on various design criteria: Many design criteria such

as the minimal number of processors are based on the way that processors are

allocated for computations. It is thus important to study methods to derive

processor allocation schemes.

- Processor efficiency: In the execution of the application, processors in the derived array may be only actively doing useful work at some time and are idle for the rest of time. It is thus very important to derive an array with maximum processor utilization during the execution of the application without sacrificing other optimization design criteria such as total completion time and processor complexity.

## Overview of the Dissertation

In the first part, we concentrate on communication issues in the mapping problem. We empirically study the effect of communication overhead caused by the topological mismatch in a multicomputer under two kinds of communication technology,

namely, the store-forward and the wormhole routing schemes. Empirical case studies

are carried out to qualitatively characterize the impact of several important mapping

metrics and architectural factors on the performance of benchmarks. We show that

the communication overhead caused by the topological mismatch can still significantly affect the performance of a benchmark. To quantify communication overhead,

we propose and validate analytical estimation formulae for message latency. The

formulae take runtime contention information into account and are directly sensitive

to an application. We discuss incorporation of the message latency formulae in a

general purpose multicomputer simulator, and a new parallel program performance

evaluation framework that uses the formulae is proposed.

We then study the problem of reducing communication overhead by utilizing knowledge of the message passing requirements in an application. We propose efficient application-specific routing algorithms to reduce communication overhead based on the newly developed metrics. The proposed techniques can be applied to parallel programs with intensive communication in a multicomputer with user-controlled routing capability such as Intel's iWarp systems or Meiko's transputer systems.

In the second part, the problem of mapping a class of algorithms called Regular Iterative Algorithms (RIAs) to a systolic array is studied. To achieve the inherent parallelism exhibited in a RIA, the problem of finding the optimal timing schedule is studied. To map such an algorithm to a systolic array which has constraints on its

physical connections, a systematic method to enumerate linear allocation functions is developed. Such a method can be used to design systolic arrays based on various optimization criteria. To fully utilize processor resources, we study the problem of deriving a fully efficient systolic array with respect to processor utilization. A systematic method is proposed to generate a 100% efficient array without slowing down the array and without adding extra functional units. Our work solves the problem of mapping RIAs to systolic arrays in three important aspects, namely, timing schedule, processor allocation, and processor utilization.

# Part I

# COMMUNICATION ISSUES IN MAPPING TO MULTICOMPUTERS

#### CHAPTER II

#### MAPPING TO MULTICOMPUTERS

From the store-forward flow control scheme in old generation multicomputers to the wormhole and circuit-switching schemes used in current advanced multicomputers, the transition of communication switching technologies has made communication orders of magnitude faster. These changes entail a careful re-examination of classic methods and metrics which have been used in designing a mapping tailored to an old generation multicomputer. Empirical studies should be conducted to reveal the nature of the communication overhead incurred by these new technologies and their effects on the performance of an application should be characterized. New mapping algorithms and metrics to reduce communication overhead in a mapping should be developed. This part of the thesis focuses on the above problems.

In this chapter, we describe the background knowledge needed to understand the communication issues related to the mapping problem. A general framework for mapping to a multicomputer is described. Several communication switching techniques used in multicomputers are introduced and different routing schemes are described. The deadlock problem, which is more critical in a wormhole routing scheme, is also introduced. We then identify three fundamental problems of communication overhead related to mapping and introduce communication overhead metrics which will be used throughout this part. Finally, we overview the work in Part I.

### Introduction

As the technology of multicomputer architecture advances, major factors which affect the performance of a parallel program on a multicomputer have changed. In particular, new switching technologies used on a multicomputer have reduced communication overhead dramatically. This change introduces a new research area to address performance issues related to communication overhead and how to reduce this overhead in a mapping.

Specifically, to achieve good performance for a mapping, one has to understand how the performance of a parallel program is related to communication overhead incurred by specific communication technologies, what are the major factors which affect the communication overhead in terms of a mapping, how to measure these effects for the purpose of mapping, and what kinds of new techniques can be used to reduce communication overhead.

Early work on mapping did not take the network communication technology into account or only used a very simple model of the multicomputer network. For example, in the pioneering work on mapping, Stone [112], Bokhari [11], Lo [77] and other researchers [105] proposed load balancing schemes based on simple static approximations of communication overhead. In such a model, little information about the dynamic runtime behavior of the application is assumed. In the task scheduling area, a traditional directed acyclic graph based model [106, 91] also assumes statically determined communication costs among tasks, represented as the weights of edges. These models assume an all or nothing character to communication overhead based on whether a pair of communicating tasks were assigned to the same processor (zero overhead) or different processors (fixed overhead). Lewis and Rewini [36]

used a limited model of a store-forward multicomputer network to reflect the possible communication overhead for a schedule. In their model, the communication overhead between two tasks is not only determined by the message size but also is determined by the number of hops and the approximate network traffic congestion for this message.

We believe that it is important to develop new approaches to understanding the communication overhead of multicomputers and their relation to mapping. Our study must be sensitive to new communication technologies, specifically the wormhole routing scheme. We must develop a framework and new metrics for communication overhead. Furthermore, mapping techniques to reduce the overhead need to be carefully designed and evaluated.

# A General Framework for Mapping to Multicomputers

This section describes a general framework for mapping to multicomputers. We describe characteristics of a multicomputer, the computation model used in mapping and general mapping approaches.

# Multicomputers

A multicomputer is a general purpose message passing machine. Below, we discuss the characteristics of a multicomputer.

- A multicomputer is an MIMD (multiple instruction, multiple data stream).

Each processor has its own control unit and executes its own instruction stream.

- 2. A multicomputer usually consists of powerful computing engines (ranging from several to hundreds of MFLOPS) in each processor element.

- Processors in a multicomputer are interconnected by a direct network. Examples of well-known multicomputer networks include a mesh, a tree, a hypercube and a torus.

- 4. A multicomputer has communication hardware responsible for message routing in each processor. Second generation multicomputers have dedicated communication modules separate from computation engines. Transmitting a message through an intermediate node does not need to interrupt the computation carried out by the local processor.

- 5. A multicomputer has moderate communication overhead. Second generation multicomputers support fast communication. For example, in an IPSC/2-SX system, sending a double-precision number to its neighboring processor only takes 3.0μs, less than that of performing a floating point operation (3.6μs) [4].

- 6. Processors in a multicomputer execute asynchronously. No global clock is available.

Typical commercial multicomputers include Thinking Machine's CM-5, Intel's Paragon, iPSC/860, iPSC/2, iWarp and Ncube's Ncube/3200 and Ncube/2.

## Computation Models

Several graph theoretic models of parallel computations have been designed and used in the mapping community. The static task graph [112, 11, 77, 105] statically represents a parallel application as an undirected weighted graph with nodes representing processes and edges representing communication between processes. Node weights are used to represent execution costs associated with the processes, and edge

weights are used to indicate the degree of communication between two processes. This has been one of the dominant models used in the parallel and distributed computing community for mapping. The model is simple and relatively easy to construct from the original program. One of the drawbacks of the model is that it does not capture the temporal behavior of the program, which may be vital to mapping.

The second predominant model is the Directed Acyclic Graph (DAG) [106, 91, 25, 3] model. In the DAG model, nodes represent tasks and directed edges represent a dependency relation (such as a message send/receive relation) between two tasks. Furthermore, a DAG can be weighted such that node weights represent the execution cost of tasks and edge weights represent size of messages between two tasks. The DAG model was originally developed for research in scheduling and has been used in parallelizing compilers that parallelize sequential code whose data and control graphs can be represented as DAGs. While the DAG model has been utilized in the mapping community, in a communicating sequential program, it fails to capture the identities of processes which persist over the lifetime of the computation.

Recently, a model called the Temporal Communication Graph (TCG) was proposed [78] to unify the two earlier models. In practice, many parallel applications proceed through computation and communication in a phase-by-phase fashion. Processes, however, in such a phase-by-phase execution, retain their identities during the lifetime of the program execution. The TCG model captures the process identity concept and also represents computation and communication phases explicitly. Compared with the static task graph model and the DAG model, a TCG represents both the topological and the temporal precedence information and is thus more general. A language called LaRCS has been designed specifically to describe the TCG

model [81]. In this thesis, we will use static task graphs as well as TCGs as our model of computation.

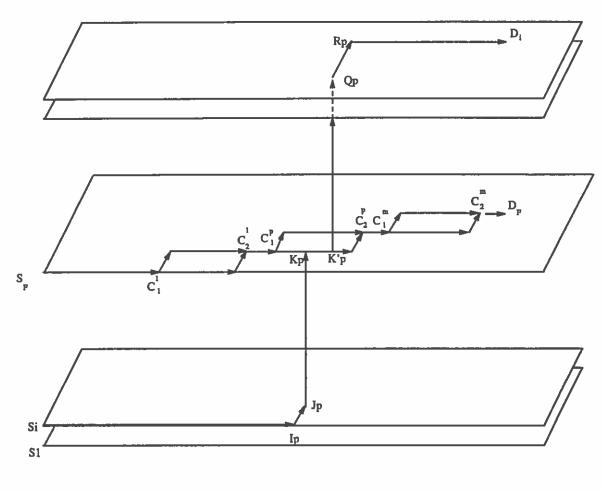

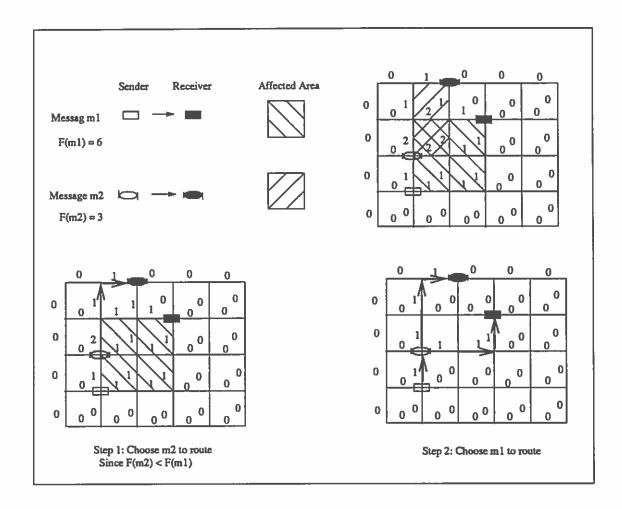

# Overview of Mapping Techniques

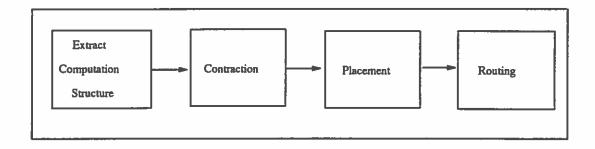

The problem of optimally mapping a general static task graph, a DAG, or a TCG to target architectures with respect to many well-known metrics is difficult. Such optimization problems are usually NP-hard [41, 25]. To simplify the complicated process, researchers have tried to decompose the mapping problem into several steps. First, information useful to the mapping is extracted from the initial description of the application, based on the computation model chosen. Several languages have been designed to represent computation models. Such languages can be a programming language such as the one used in Prep-P [9] or a special language such as LaRCS used in Oregami [81, 9]. Second, contraction is performed to minimize the mismatch between the number of available processors and the number of processes. Third, clustered processes are assigned (placed) to processors and fourth, if the target architecture allows the user to control routing or switching setting, application-specific routing can be performed to reduce traffic congestion. In addition to the above steps, if temporal information is considered, as in the DAG or the TCG model, scheduling can be performed to further specify the execution order of the processes to enhance the processor utilization. Figure 2 illustrates the first four steps of a mapping.

Notice, however, that several steps may be combined into a single step and some steps may not be necessary. For example, to take advantage of the difference in computing power of nodes in a heterogeneous environment so that processes with heavy execution cost can be assigned to faster nodes, the contraction and placement steps may need to be combined into a single step so that processes contracted are

Figure 2: Illustration of a Mapping Procedure.

assigned (placed) to specific nodes.

>

The contraction step in the mapping problem is usually performed to minimize process-processor mismatch, to balance processor workload, and to minimize interprocessor communication. A careful tradeoff is necessary since these these goals may conflict with each other. For the static task graph model, graph-theoretic methods have been proposed. These include Stone's classic minimal-cut network flow approach [112], which later was extended by Lo, Bokhari and others [77, 11]. Some other heuristics such as nearest neighboring clustering method have also been developed [105, 70].

For the DAG model, Sarkar [106], Kim and Brown [60], Papadimitrious [89] and recently Yang and Gerasoulis [44, 45] have studied the problem of clustering processes in a DAG to minimize the total completion time under the assumption that the number of processors is infinite. The clustered graph (which may no longer be a DAG) may be further clustered by heuristics used in the static task model.

For the TCG model, information on the temporal behavior of the computation can be used to improve processor utilization by clustering several processes which do not have conflicting computation phases. For example, for divide and conquer algorithms, the original complete binary tree computation structure can be contracted,

resulting in a binomial tree, to improve efficiency [79, 127], or a specific clustering can be tailored to the target architecture [123]. For a general TCG, no systematic work has been done.

The placement step is performed to minimize the topological mismatch by placing processes in order to minimize various metrics including maximum dilation, which is defined as the maximum distance messages have to travel in the target architecture. A large body of work has been carried out to develop embeddings from a task graph to the target interconnection network [100, 56, 71]. Quadratic assignment and other heuristics [50, 70] have also been studied for this purpose.

The routing step involves routing messages through a path in the network once processes have been assigned to processors. While many machines provide fixed routing schemes that are controlled by the hardware, several advanced multicomputers such as the Intel iWarp machines and MasPar machines allow the user to control routing. This provides an opportunity for the mapping software to design routings tailored for specific applications to minimize communication overhead.

The placement and the routing steps described above aim at minimization of communication overhead incurred by the topological mismatch. Different communication technologies of a multicomputer require use of different metrics for these steps. For a multicomputer, many switching techniques have been used and communication overhead varies from one scheme to the other. To achieve good performance, one needs to understand these techniques well. In the following, the communication techniques of store-forward, wormhole and other schemes such as circuit switching and virtual cut-through routing schemes are described.

# Communication Switching Techniques

The last few years have witnessed rapid development in communication switching technologies of a multicomputer network. As opposed to the old store-forward scheme, new flow control schemes have been used and these schemes have reduced communication overhead significantly. Among them, the wormhole routing and its variation, the circuit switching scheme, are the most popular ones. For example, Intel's iPSC/2 and iPSC/860 adopt the circuit switching technique, and Intel's iWarp, Intel's Paragon, NCUBE's NCUBE/2 and Ametek's Symult 2010 use the wormhole routing scheme. In the following, we review store-forward and these three newer techniques.

In an old generation multicomputer, communication through an intermediate processor may interrupt local computation on that node (an example is Intel's iPSC/1). In a new generation multicomputer, a node usually consists of three components: a compute engine, a local memory module and a communication module (also called a router). The compute engine, coupled with the local memory, is responsible for local computation. The communication module, along with communication channels, is responsible for message passing with other nodes in the network. Intermediate message passing does not interrupt local computation.

Communication in a multicomputer network is determined by two methods: flow control and routing. Flow control is the method used to regulate traffic in a network. It determines when a message or part of a message can advance and what communication resources can be allocated to a message. Routing is a method to choose a path for a message over a network. Most commercial machines use a fixed routing scheme which always routes messages through fixed routes. In the following,

we will describe different flow control schemes and in the next section, we will describe routing schemes.

Three concepts are important to understand a flow control scheme.

- Message: The logical unit of communication between processes.

- Packet: The smallest unit which contains routing information. A message is divided into one or more packets.

- Flit: The smallest unit which is transmitted as a unit. A packet is further divided into one or more flits. Only the first flit contains the routing information.

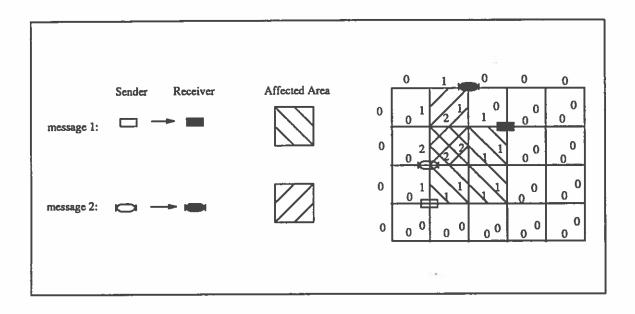

We call the time to transmit a message from its source node to its destination node message latency.

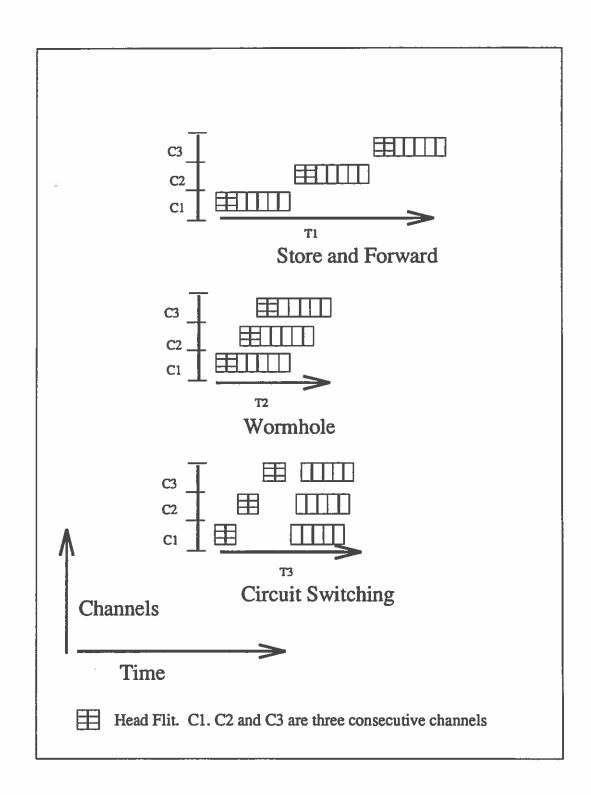

In the following, we discuss message latency under an assumption that messages are never blocked during their entire transmission (the contention-free assumption). In the store-forward flow control scheme, a packet is treated as a single flit. In an intermediate node, a packet is received and buffered completely before it is forwarded to its next node. Let D be the number of hops a packet has to travel, and let L be the packet length. The message latency  $T_1$  for a packet to reach its destination, under the contention-free assumption is

$$T_1 = D(w + L/b)$$

where w is a system dependent constant representing overhead for packet enqueuing and other bookkeeping, and b is the the bandwidth of a communication channel.

In the virtual cut-through or wormhole flow control scheme, a packet is divided into small flits. The first flit, also called the header, contains the routing information.

Communication channels are allocated flit by flit. The header reserves the communication channels it has traversed, which are allocated to its following flits. The last flit (also called the tail) releases a channel once it has passed across the channel. Since flits pass through channels in a pipelined fashion, the time for an entire packet to reach its destination, under the contention-free assumption is

$$T_2 = s + h * D + L/b$$

where h is the time to transmit the header across one channel and s is the startup time, i.e. the overhead for message injection into the network. In the current generation of multicomputers which utilize wormhole routing, h is small. For example, in iWarp, h is less than 20ns per byte [14].

Virtual cut-through and wormhole flow control schemes differ from each other when message contention is present. When the next channel for the header is unavailable, virtual cut-through buffers all the rest of the flits in the node where the header is. On the other hand, the wormhole flow control scheme is a blocking version of virtual cut-through in that all flits stay in the buffers where they are when the next channel for the header is unavailable. It can be seen that the wormhole flow control scheme requires substantially smaller buffer space. On the other hand, since flits stay in the network when a message is blocked in the wormhole flow control scheme, they may block other messages.

Another flow control scheme which has been used in commercial machines is called circuit-switching which is similar to the one used in a telephone network. In the circuit-switching scheme, when a packet is to be sent to its destination, its header, which contains routing information, is first transmitted along its intended path and

reserves the channels if it is possible. After the path is established, the whole packet is sent out. Message latency under the contention-free assumption is similar to that of wormhole routing.

Figure 3 illustrates the store-forward, wormhole and circuit-switching schemes.

It can be seen that when there is no contention, the wormhole scheme and the virtual cut-through scheme have considerably less overhead than the store-forward scheme. Furthermore, when L >> D, the distance (number of hops traveled) has negligible effect on the transmission time for the wormhole, virtual cut-through and circuit-switching schemes.

Because of such a dramatic message latency improvement from the store-forward to the wormhole routing, some industry vendors [26] claim that task placement is no longer an important issue. For example, in Intel's iPSC/2 user guide [26], it is claimed that "Direct-Connect routing imposes virtually no added penalty on multiple node communication. Consequently, you can view the machine as an ensemble of fully interconnected processors".

The above formulae, however, are based on the contention-free assumption. When messages are congested due to communication resource (channel or buffer) contention, the extra time caused by the contention may vary dramatically for different flow control schemes. To be more precise, the latency (T) of a message is the summation of the message latency (t) under the contention-free assumption and the time  $(C_t)$  spent due to communication resource contention. From the above description of the flow control schemes, many factors may affect T. In the store-forward flow control scheme, t is sufficiently large and therefore minimizing the message distance, which is the dominant factor for t, can be chosen as the major criterion. In a virtual

Figure 3: Illustration of Flow Control Schemes in a Contention-Free Situation.

cut-through, wormhole or circuit-switching scheme, however, t has dropped significantly and  $C_t$ 's role in T has increased. We therefore need to re-examine metrics related to the mapping and routings.

# Routings

Routing is the method used to choose a path for a message through the network. More precisely, a routing can be described as a permissible function  $\mathcal{P}$  and a selection function  $\mathcal{S}$ .

$$\mathcal{P}: C \times N \mapsto 2^C$$

$$S: \mathcal{P}(C) \times \beta \mapsto C$$

where C is the set of channels,  $2^C$  is a power set of C, N is the set of addresses of nodes and  $\beta$  is a set of network states which may include current traffic state, past history of the routing or even random information (generated by a random generator). Function  $\mathcal{P}$  identifies a set of *permissible* output channels in  $2^C$ , given the current input channel  $c \in C$  and the destination address  $n \in N$ . The selection function S chooses the output channel from the permissible channels  $\mathcal{P}(C)$ , based on the current network state  $\beta$ .

Depending on  $\mathcal{P}$  and  $\mathcal{S}$ , we can classify routings into fixed (deterministic), oblivious and adaptive categories. A deterministic routing chooses a path based only on the source and destination addresses of a message (i.e.,  $\mathcal{P}$  returns a single-element set for the output channel and  $\beta$  is an empty set). In an oblivious routing,  $\beta$  does not contain any information on the current traffic state of the network but may contain some other information such as time, randomness or the contents of messages. Finally, an adaptive routing is the most general and it may make a routing decision based on the current traffic state.

Deterministic routing has been widely used in multicomputers because of its simplicity and good performance when the network traffic is light. For example, many hypercube multicomputers (iPSC/2, Ncube) use E-cube routing, which chooses the outgoing channel for a message as the first most significant bit where the destination address and the current node address differs. In the standard hypercube binary code labeling scheme, it can be seen that E-cube routing routes a message from higher dimension (more significant bit) to lower dimension. For example, if a message is to be sent from 0010 to 1001 in a four dimensional binary cube, the path chosen by the E-cube routing is 0010, 1010, 1000, 1001. A similar routing scheme, called XY-routing, is used in a two dimensional mesh. The XY-routing always routes a message first along the X-direction (horizontal) and then along the Y-direction. The Intel Paragon and iWarp machines adopt this routing scheme as their default routing.

A classic oblivious routing scheme was proposed by Valiant and Brebner [116]. It first routes a message from its source to a randomly selected intermediate node and from there to its destination. In this routing,  $\beta$  contains some contents of the message (whether the message has reached its random intermediate node) and randomness information. It has been shown that for a permutation routing (i.e., a node sends only one message and receives only one message), this routing has  $O(\log N)$  time on an N node cube. Another oblivious routing scheme allows the router to choose the outgoing channel based on the instruction given in the message header. In such a routing scheme, the user can control the routing by appropriately setting the routing information in the message header. This has been adopted in the iWarp system [49].

Recently, several adaptive routing strategies have been proposed and studied. In these adaptive routing schemes, randomization is used to diffuse traffic. Two problems should be considered in designing an adaptive routing, namely, deadlock and livelock. Deadlock may occur because of circular waiting for channels (or buffers) (see, Section on page 26 for more detail). Livelock is a situation where a message moves indefinitely through the network and is never delivered to its destination. Ngai and Seitz [88] proposed an adaptive routing scheme for a virtual cut-through network. The routing uses randomness to misroute messages (i.e., send the message to a random output channel) once they are blocked and uses multiple buffers to solve the livelock problem. Another adaptive routing technique which uses randomness to solve the livelock problem has been proposed by Konstantinidou and Snyder [63]. The routing scheme is called the Chaos router because it uses random information to avoid the livelock problem with a high probability. Other adaptive routings for wormhole routed networks have been also proposed and studied [47, 46].

A restricted routing called permutation routing has been extensively studied in theory. Most work along this direction is based on the store-forward model. In a store-forward model, a permutation routing is closely related to the problem of sorting N elements on an N node network where initially, each node has one element. Many results, along with sorting results, are proposed for various topologies such as cubes, meshes and shuffle exchange networks [71]. Recently, there have been some interests in developing permutation routing on a wormhole or virtual cut-through routed network [83, 95].

### Deadlock Avoidance

A routing may result in deadlock due to circular waiting for communication resources (buffers or channels). Deadlock can be avoided by either a careful routing or through additional hardware support.

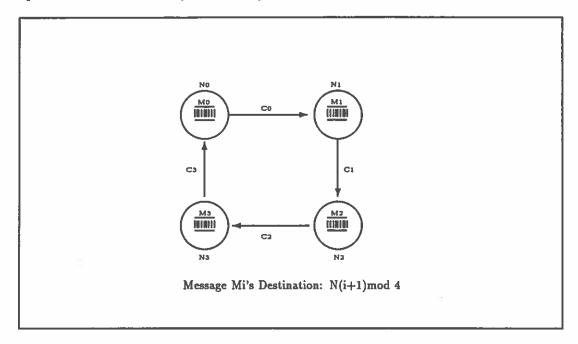

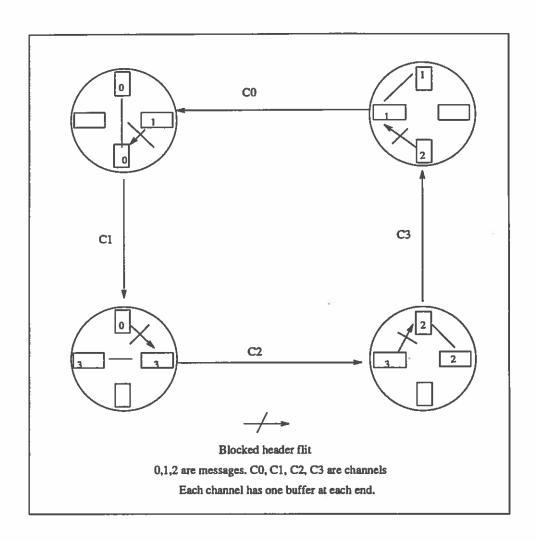

Store-forward, virtual cut-through and wormhole routing schemes all can result in deadlock if messages are waiting for communication resources in a circular fashion. In store-forward and virtual cut-through, the communication resources are the buffers for messages to be relayed in a node. Figure 4 shows a possible situation if the buffer space in a node can only hold one packet.

Figure 4: Deadlock in a Store-Forward Routing.

In wormhole routing, since the buffer space in a node for a relayed message can only hold one or two flits for each communication channel, it is more likely to result in a deadlock due to the occupancy of communication channels. Figure 5 shows such a possible situation.

More precisely, if there is a possibility for a routing to relay a packet or part of a packet from resource A to resource B, we say that resource A depends on B. This defines a binary relation  $\mathcal{D}$  over all resources. If  $\mathcal{D}$  is not partially ordered, then there is a possible circular dependency among resources, which corresponds to

Figure 5: Deadlock in a Wormhole Routing.

a potential deadlock situation. In a wormhole routing, the resources are the channels and it has been shown that there exits no deadlock iff the channel dependency graph for a routing is acyclic [30].

Thus, to test whether a wormhole routing creates a potential deadlock situation, we can construct the channel dependency graph (CDG) based on the routing and then test whether the CDG has a cycle or not. In Chapter IV, we propose another graph called the Generic Physical Channel Dependency Graph (GPCDG) to capture all the possible channel dependencies as well as their physical connections in a single structure. Such a structure facilitates the development of low-contention deadlock-free wormhole routing.

Two approaches have been adopted to avoid a deadlock. The first is to carefully design a routing strategy such that the channel dependency graph is guaranteed to be acyclic. This approach minimizes the hardware support but may eliminate some possible paths, hence reducing the connectivity of the network. The other approach is to design flow control to avoid deadlock with appropriate hardware support. Extra buffers are introduced. We discuss these two approaches in the following.

A way to avoid deadlock is to simply adopt a deterministic (fixed) routing which can be proved to be deadlock free. For example, both E-cube routing for a hypercube system and XY-routing for a two-dimensional mesh have been proved to be deadlock free with respect to store-forward and wormhole routing schemes [30], respectively. This is because the channel dependency graph for these two routings are acyclic.

A fixed routing scheme, however, eliminates too many potential paths. This may result in poor utilization of channel resources. Although some schemes have been proposed [22, 46, 73] to allow finding more paths which are deadlock free, many

paths provided by the network with rich connectivity such as a hypercube are still not usable.

A general scheme to provide more connectivity while avoiding deadlock is to create virtual resources which share the same physical resource. The flow control is modified to guarantee freedom from deadlock. Analogous to methods used to avoid deadlock in an operating system [90], a partial order on such resources is introduced to ensure that a routing is designed so that the partial order is satisfied and no circular waiting state is reached.

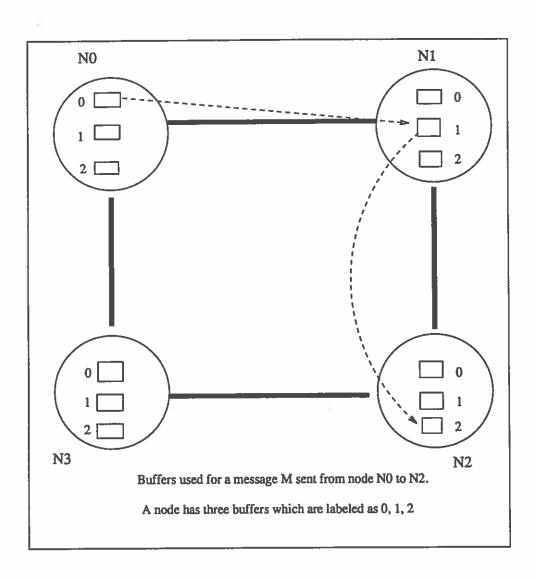

In a store-forward routing, a method called the structured buffer [43] is used to label buffers in ascending order. Packets, once buffered, can only be sent to a restricted set of buffers on the next node. A buffer dependency graph is created so that if there is a packet which can be routed from buffer A to buffer B, then A depends on B. Again, the graph should be acyclic to ensure deadlock freedom. A simple implementation of the structured buffer scheme creates D+1 buffers in every node where D is the network diameter. A packet can only be sent from a buffer labeled as n to another buffer whose label is larger than n. For example, the deadlock in Figure 4 can be avoided by introducing two more buffers for all nodes and the three buffers are labeled as 0,1,2. When the packet is injected into the network, it is first buffered in buffer 0 and then it can be only sent to buffers which have larger labels. Figure 6 illustrates this idea. It can be seen that this scheme requires a considerable amount of storage space for a large network.

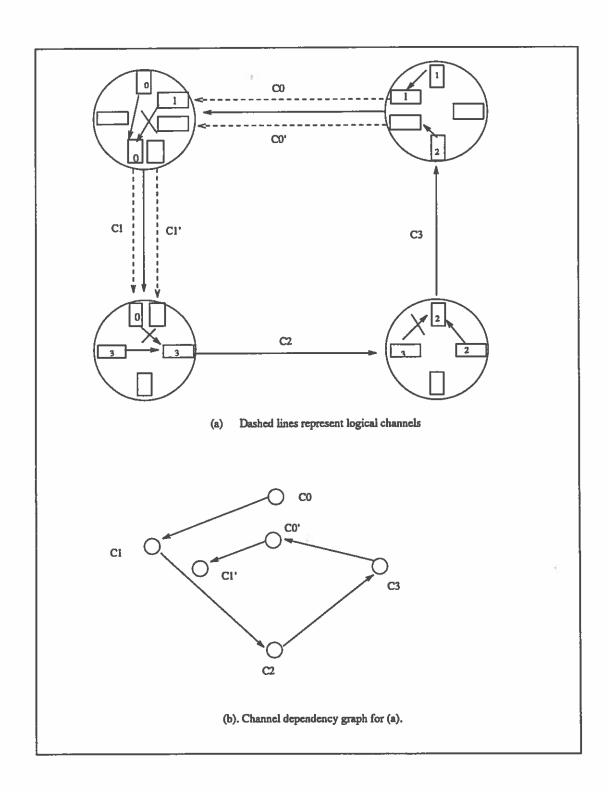

A similar technique called the *virtual channel* technique is used in wormhole routing to break any cyclic dependencies [30, 29]. The idea is to view communication channels as the resources for which different packet routes are competing. Multiple

Figure 6: Deadlock Avoidance in a Store-Forward Routing.

flit buffers are introduced for a channel. These multiple flit buffers are called virtual channels since they are essentially responsible for communication over the same physical channels. Again, a labeling scheme is introduced to ensure the resource dependency to be acyclic. The deadlock in Figure 5 is avoided by introducing one more logical flit buffer  $c'_0$  and  $c'_1$  for each channel  $c_0$  and  $c_1$  respectively, as shown in Figure 7(a). The channel dependency graph is shown in Figure 7(b). In addition to its use for deadlock avoidance, the virtual channel technique can also be used to increase network connectivity and support adaptive routing.

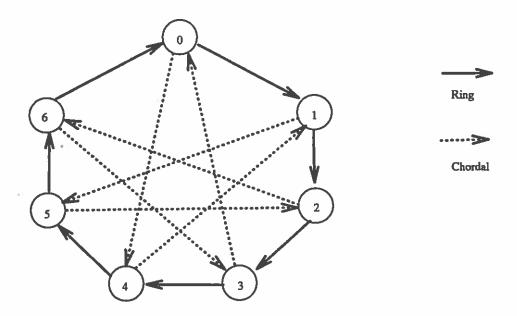

With virtual channels, a physical network can be also partitioned into several virtual networks. A virtual network consists of a subset of virtual channels. Virtual networks make it possible to support multiple topologies on a single multicomputer. The concept has been used in some advanced computers such as Intel's iWarp system.

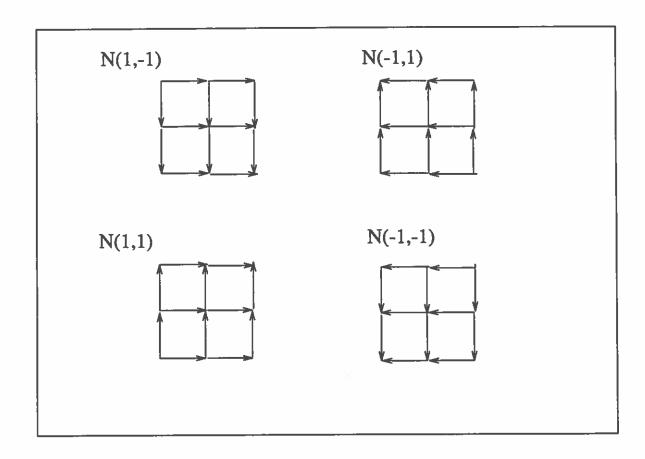

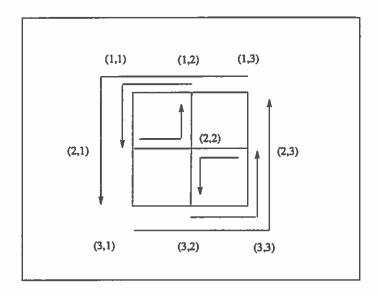

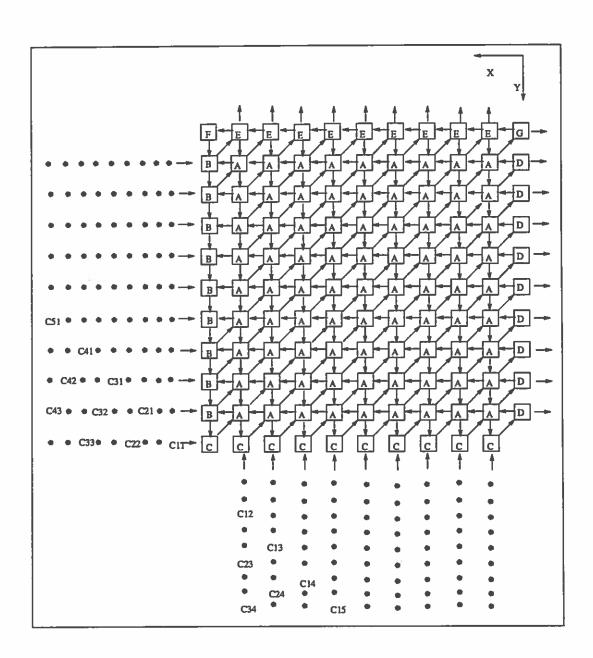

In [55], a simple way is proposed to partition an n-dimensional mesh into  $2^n$  virtual networks such that all Manhattan shortest paths are represented. A Manhattan shortest path has a shortest rectilinear distance between the source and the destination. More precisely, suppose that G is a n dimensional mesh with nodes labeled with standard Cartesian coordinates. Clearly, a given channel lies in a single dimension. The direction of each channel in G has two possibilities, specified as 1 or -1. G is partitioned into  $2^n$  virtual networks where each virtual network N is specified uniquely by a vector  $(d_1, \ldots, d_n)$  where  $d_i \in \{1, -1\}$ .  $N(d_1, \ldots, d_n)$  consists of all channels whose orientation is  $d_i$  in dimension i for each  $i = 1, \ldots, n$ . Figure 8 shows the partitioning on a 2-D mesh.

### Remarks:

1. It is easy to show that the above partition covers all possible Manhattan shortest

Figure 7: Deadlock Avoidance in a Wormhole Routing.

Figure 8: Partitioning of a 2-D Mesh into Four Virtual Networks.

paths in an n dimensional mesh.

2. If a routing routes message through a Manhattan shortest path in one of the virtual networks, then it is deadlock-free. This is because the virtual networks themselves are acyclic and hence their corresponding channel dependency graphs must also be acyclic.

The mesh which has such a virtual network support is called a partitioned mesh. The above scheme is best for a low dimensional mesh. For example, for a two dimensional mesh, the number of virtual networks is only two, which can be implemented practically. In fact, in the Intel iWarp system, two virtual networks are supported for a two dimensional torus, which is the physical configuration of the system [14, 49]. A similar virtual network partitioning scheme for k-ary n-cube has been proposed by Linder and Harden [74].

## Fundamental Issues in Communication Overhead

In this section, we identify fundamental issues in developing mapping algorithms to reduce communication overhead on a multicomputer.

The store-forward routing scheme was used in old generation multicomputers such as Intel iPSC/1 and Caltech Cosmic Cube machines. This has been replaced with advanced communication technologies such as the wormhole and the circuit switching routing schemes in the current advanced multicomputers such as Intel Paragon, iWarp and Ncube Ncube-2 machines. As we can see from the previous section, message latency under the contention-free assumption has been reduced dramatically from the store-forward routing to the wormhole routing. This change has a great impact on the mapping problem. In the following, we identify three fundamental issues.

The first question is: does task placement still matter for the performance of an application in an advanced multicomputer with the wormhole routing? It is very natural to raise this question since the communication overhead has been reduced dramatically in the wormhole routing scheme. However, when the channel contention factor is taken into account, intuitively, message latency will be affected by traffic congestion. It is thus important to understand how much a task placement scheme can do to reduce message latency. Several researchers [13, 23] have studied this problem based on various limited assumptions. However, the total completion time of actual benchmarks which are mapped with several mapping schemes has not been directly measured and studied.

The second question is: what factors contribute to the communication overhead? For the store-forward routing, maximum dilation is one of the major metrics used to develop a mapping. This has been changed for the wormhole routing. It is therefore necessary to develop and study new metrics to better characterize the communication overhead.

The third question is: how to reduce communication overhead when designing a mapping algorithm? How do we design good placement algorithms and good routing algorithms to optimize the new metrics identified? New methods should be studied to incorporate these new metrics into the design of mapping algorithms.

In this thesis, we focus on these problems in Part I.

# Communication Overhead Metrics

In this section, several mapping metrics related to communication overhead are described. For the purpose of this thesis, we ignore other mapping metrics which are not related to the communication overhead caused by the topological mismatch (such as processor load balancing).

Since we do not consider processor resource mismatch in this thesis, we simplify the mapping and assume that contraction has been done and thus, only a one-to-one placement in the mapping is considered.

We first define the metrics based on the static task graph model. A static task graph is a weighted graph  $C = (V, E, W_v, W_e)$  where the nodes V represent processes and edge  $e = (a, b) \in E$  between node a and b represents a communication (possibly bi-directional) between task a and task b with weight  $W_e(e)$ . This weight represents an estimation of the communication volume between a and b. Each process a is further associated with a weight  $W_v(a)$  which represents an estimation of the amount of computation performed by a. The topology of a multicomputer is modeled as a graph A = (V(A), E(A)), where V(A) represent processors and E(A) correspond to the processor-to-processor physical connections of the underlying interconnection network.

A mapping  $\mathcal{M}$  can be specified by two functions:  $\mathcal{M}_p$  and  $\mathcal{M}_r$  where  $\mathcal{M}_p$  is a function which maps nodes in V to nodes in V(A).  $\mathcal{M}_p$  is called a placement function.  $\mathcal{M}_r$  is a function which maps an edge (a,b) in E to a path  $p_0, p_1, \ldots, p_m$  in E(A) such that  $p_0 = \mathcal{M}_p(a), p_m = \mathcal{M}_p(b)$ .  $\mathcal{M}_r$  is called the routing function. When the architecture only provides a fixed routing,  $\mathcal{M}_r$  is completely determined by the fixed routing function.

The most widely used metrics for inter-processor communication overhead include dilation, channel contention and path level contention. Based on the static task graph model, we have the following definitions:

### Definition 2.1

The dilation of an edge  $m \in E$  is  $|\mathcal{M}_r(m)|$  (denoted as Dila(m)). The weighted dilation of m is  $W_e(m) \times |\mathcal{M}_r(m)|$  (denoted as WDila(m)).  $\square$

The dilation represents the the number of hops a message has to traverse.

# Definition 2.2

)

)