# TIMING ANALYSIS IN BINARY-TO-BINARY TRANSLATION

by

### INKYU KIM

# A DISSERTATION

Presented to the Department of Computer

and Information Science

and the Graduate School of the University of Oregon

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

June 1997

"Timing Analysis In Binary-To-Binary Translation," a dissertation prepared by Inkyu Kim in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science. This dissertation has been approved and accepted by:

Chair of the Examining Committee

May 25 1997

Date

Commitee in charge:

ccepted by;

Dr. Zary Segall, Chair

Dr. Arthur Farley

Dr. John Conery

Dr. Nancy Melone

Vice Provost and Dean of the Graduate School

© 1997 Inkyu Kim

)

An Abstract of the Dissertation of

Inkyu Kim

for the degree of

Doctor of Philosophy

in the Department of Computer and Information Science

to be taken

June 1997

Title: TIMING ANALYSIS IN BINARY-TO-BINARY TRANSLATION

Approved:

Do Zarv Segall

Research in TIBBIT (Timing Insensitive Binary to BInary Translation) proposed a methodology to provide timing equivalence as well as semantic equivalence in binaryto-binary translation of real-time applications by inserting synchronization at regular intervals. However, the timing equivalence of programs generated by TIBBIT is not guaranteed. In this dissertation, we provide a method to guarantee the timing equivalence of the generated target binary programs.

We use an interval-based approach, first invented by Allen and Cocke, to test timing equivalence of a translated target binary program with respect to a source binary program. We introduce the concept of timing sensitivity, the maximum timing difference between the source and target programs, to judge how closely the target program will mimic the source program's timing.

We say that a target program is executable with timing equivalence if the timing sensitivity can be reduced to zero, and with timing invariance if the timing sensitivity can be bounded by a constant. We have discovered necessary and sufficient conditions to provide timing equivalence and invariance for target programs.

If a target program is executable with timing equivalence or invariance, it must be enforced by a synchronization scheme. When the target program is executable with timing invariance, the timing sensitivity depends on how and where the target program is synchronized. We use a local synchronization scheme that removes local timing error to provide timing invariance. We develop a static method to measure timing sensitivity with the local synchronization scheme. We also develop optimization techniques to minimize timing sensitivity.

In summary, the main research contributions of this dissertation are 1) necessary and sufficient conditions for timing equivalent and invariant translation 2) an algorithm to find timing sensitivity of the target program and 3) techniques to minimize timing sensitivity of the target program.

0

#### CURRICULUM VITA

NAME OF THE AUTHOR: Inkyu Kim

PLACE OF BIRTH: Kyungbuk, Korea

DATE OF BIRTH: February 26, 1960

#### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon Oregon State University Yeungnam University, Taegu Korea

#### **DEGREES AWARDED:**

Doctor of Philosophy in Computer and Information Science, 1997, University of Oregon

Master of Science in Computer Science, 1990, Oregon State University

Bachelor of Engineering in Electronic Engineering, 1985, Yeungnam University

#### AREAS OF SPECIAL INTEREST:

Binary-to-Binary Translation Real-time Systems Optimizing Compiler Program Debugging Parallel Processing

#### PROFESSIONAL EXPERIENCE:

Research Assistant, Department of Computer and Information Science, University of Oregon, Eugene, 1993-1997

Research Staff, Department of Computer Science and Engineering, Oregon Graduate Institute of Science and Technology, Portland, 1992-1993

Research Assistant, Department of Computer Science, Oregon State University, Corvallis, 1988-1992

# DEDICATION

This dissertation is dedicated in loving memory of my father

Heetae Kim

who did not wait for my long studies.

#### ACKNOWLEDGEMENTS

Finally done (or, Phinally Done(Ph.D)!). Many thanks goes to many people:

First to my advisor, Zary Segall, for his patience, encouragement, support and ideas. To my committee members, Arthur Farley, John Conery and Nancy Melone for their comments and encouragements. Without them this would not be possible.

To the staff in the CIS department, Betty Lockwood, my American mom, Shelley Carlson, Wanda Weber and Jan Saunders, who gave me lots of smiles and help. They provided some of the best support.

)

To the graduate students who made rough times tolerable, Ferenc Rákóczi, Gunnar Sacher, Gerd Kortuem, Odile Wolf, Takunari Miyazaki, Ted Kirkpatrick, Yong Xiao, Kevin Glass, Jens Mache and Bei Li. They are wonderful to work with.

A special thanks goes to Dr. Bryce Cogswell for many discussions and suggestions. He read the first version of this thesis thoroughly and corrected many mistakes.

Even more thanks goes to my family, my wife, Geeyeoun for her persevering love and support throughout the years, my two sons, Hyunwoo and Hyunjin for the joy they bring me, my sister, Hyunkyu for her delicate mind and my two brothers, Junkyu and Changbum for their brotherhood. They are the source of my energy.

Last but not least thanks goes to my parents, one in this world, Byoungok Choi and the other in the other world, Heetae Kim. They are the reason. It was tough when he did not wait for me to finish my long studies in this world. I know he is happy now but I wish I could see his face with a big smile.

This work was sponsored in part by ARPA, monitored by the Air Force, under Contract Number F33615-93-C-1311, and Martin Marietta under TTM748365.

The view, opinions, and/or findings contained in this dissertation are those of the Author, and shall not be construed as an official Advanced Research Projects Agency, the United State Air Force, or University of Oregon position, policy or decision, unless designated by other documentation.

# TABLE OF CONTENTS

| Chapter                                                                                                                                                                                       |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| I. INTRODUCTION AND RATIONALE                                                                                                                                                                 | . 1                                  |

| Binary-to-Binary Translation Binary-to-Binary Translation of Real-Time Applications Rationale Related Work TIBBIT Project Overview Summary of Contributions Thesis Organization               | . 4<br>. 5<br>. 9<br>. 18<br>. 19    |

| II. BACKGROUND  Timelines and Events Real-Time Systems I/O Events Machine Models Synchronization Real-Time Languages and Programs Program Translation                                         | . 21<br>. 21<br>. 22<br>. 24<br>. 25 |

| Set                                                                                                                                                                                           | . 33<br>. 33<br>. 35<br>. 39         |

| IV. TIMING EQUIVALENT TRANSLATION  Execution Instances and Complete Paths Global Virtual Clocks and Synchronizations Timing Sensitivity Timing Equivalence, Invariance and Divergence Summary | . 43<br>. 45<br>. 48<br>. 53         |

|        |                                                                                                                                       | xii                                |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| V.     | TIMING EQUIVALENCE ANALYSIS                                                                                                           | 58                                 |

|        | Problem Statement Interval Analysis Timing Invariance Analysis Using Intervals Data-Flow Approach Timing Equivalence Analysis Summary | 58<br>67<br>80<br>85<br>100<br>101 |

| VI.    | ENFORCEMENT OF TIMING EQUIVALENCE                                                                                                     | 102                                |

|        | Problem Statement                                                                                                                     | 102<br>103<br>107<br>117           |

| VII.   | TIMING SENSITIVITY ANALYSIS                                                                                                           | 118                                |

|        | Problem Statement                                                                                                                     | 118<br>119<br>127<br>131<br>148    |

| VIII.  | OPTIMIZATION FOR TIMING EQUIVALENCE                                                                                                   | 149                                |

|        | Problem Statement                                                                                                                     | 149<br>151<br>171<br>174           |

| IX.    | IMPLEMENTATION ISSUES                                                                                                                 | 175                                |

|        | Engineering Problems                                                                                                                  | 175<br>178                         |

| X.     | SUMMARY AND FUTURE WORK                                                                                                               | 180                                |

|        | Significance of The Problem                                                                                                           | 180<br>181<br>184                  |

| י זמזמ | IOCD A DUV                                                                                                                            | 105                                |

# LIST OF TABLES

| Table |                                                                      | Page |

|-------|----------------------------------------------------------------------|------|

| 1.    | A Summary of Notations                                               | 42   |

| 2.    | Execution Time on Source and Target Machines for All Simple Paths in |      |

|       | Figure 21                                                            | 63   |

| 3.    | Execution Time on Source and Target Machine for All Simple Paths in  |      |

|       | Figure 28                                                            | 65   |

# LIST OF FIGURES

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

| 1.     | Binary-to-Binary Translation                                        | 2    |

| 2.     | Components of Binary-to-Binary Translation                          | 3    |

| 3.     | The Problem of Providing The Timing Equivalence Between Source and  |      |

|        | Target Programs                                                     |      |

| 4.     | TIBBIT Algorithm to Provide Timing Equivalence                      | 5    |

| 5.     | Timing Equivalent Translation with Slower Instructions              |      |

| 6.     | Timing Difference Between Source and Target Applications Limited by |      |

|        | a Constant                                                          |      |

| 7.     | The Overall Structure of TIBBIT                                     |      |

| 8.     | Timeline, Events and Time Duration Between Two Events               |      |

| 9.     | Timeline, I/O Events and Duration Between Two I/O Events            |      |

| 10.    | A Source Application for Source Machine and a Translated Target Ap- |      |

|        | plication for Target Machine                                        |      |

| 11.    | Synchronization of Corresponding I/O Events                         | 26   |

| 12.    | Synchronization of Source and Target Programs                       |      |

| 13.    | A Simple Real-Time Program                                          |      |

| 14.    | A Simple Real-Time Program with Event-Based Timing Constructs       |      |

| 15.    | Translator                                                          | 30   |

| 16.    | An Example of a Control Flow Graph                                  | 38   |

| 17.    | A Spanning Tree of The CFG Shown in Figure 16                       | 40   |

| 18.    | The Dominator Tree of The CFG Shown in Figure 16                    | 42   |

| 19.    | The Control Flow Graph for The Program Shown in Figure 13           | 44   |

| 20.    | Synchronization Algorithm                                           |      |

| 21.    | A Control Flow Graph with a Synchronized Edge                       | 47   |

|     |                                                                   | xv  |

|-----|-------------------------------------------------------------------|-----|

| 22. | Absolute Timing Sensitivity                                       | 49  |

| 23. | A Complete Path on The Source and Target Machine                  | 50  |

| 24. | Relative Timing Sensitivity                                       | 51  |

| 25. | Two Cases Where $\Psi(cp) = 2 \times \Delta(cp)$                  | 52  |

| 26. | Timing Equivalence, Invariance and Divergence of Paths            | 55  |

| 27. | A Complete Path                                                   | 57  |

| 28. | An Example of Control Flow Graph                                  | 64  |

| 29. | A Complete Path Divided into Simple Paths                         | 66  |

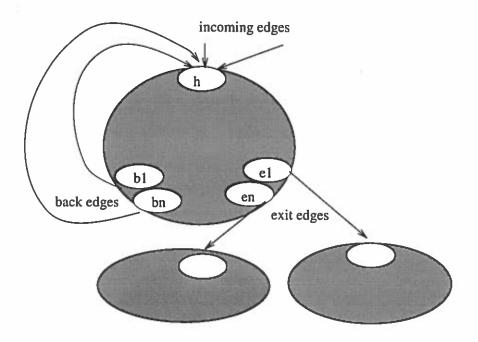

| 30. | The Structure of an Interval                                      | 68  |

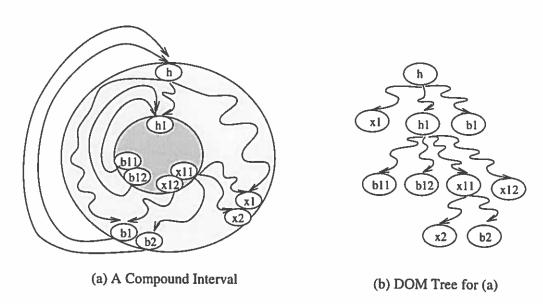

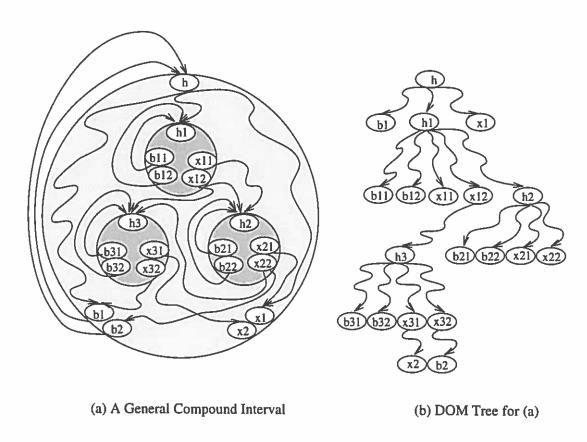

| 31. | A Nested Interval and Its Dominator Tree                          | 69  |

| 32. | A General Compound Interval and Its Dominator Tree                | 70  |

| 33. | The Dominator Tree of The $G$ Shown in Figure 28                  | 73  |

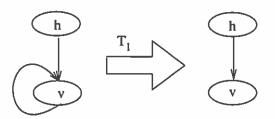

| 34. | Graphical Representation of $T_1$ Transformation                  | 75  |

| 35. | Graphical Representation of T <sub>2</sub> Transformation         | 76  |

| 36. | An Interval Algorithm                                             | 78  |

| 37. | The Modified Control Flow Graph $G_M$ of $G$ Given in Figure 16   | 82  |

| 38. | The Modified Control Flow Graph $G_M$ of $G$ Given in Figure 28   | 83  |

| 39. | Algorithm for Timing Analysis                                     | 89  |

| 40. | Algorithm for Modified Reduce()                                   | 90  |

| 41. | Algorithm for $T_2()$ Transformation                              | 91  |

| 42. | After $I(e)$ is Reduced                                           | 97  |

| 43. | After $I(d)$ is Reduced                                           | 99  |

| 44. | An Example of Control Flow Graph for Global Synchronization       | 104 |

| 45. | With Global Synchronization Scheme                                | 106 |

| 46. | Algorithm for Local Synchronization                               | 108 |

| 47. | With Local Synchronization Scheme                                 | 112 |

| 48. | An Example of Control Flow Graph for Local Synchronization Scheme | 113 |

49.

|     |                                                                                | xvi |

|-----|--------------------------------------------------------------------------------|-----|

| 50. | With Local Synchronization Scheme                                              | 115 |

| 51. | Adding Additional Synchronization to Optimize Local Synchronization            | 116 |

| 52. | With Optimized Local Synchronization Scheme                                    | 116 |

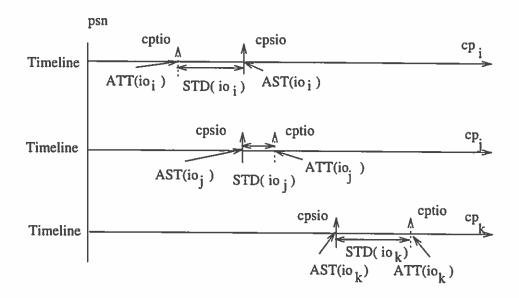

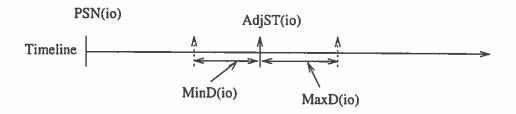

| 53. | Previous Synchronization Node of an I/O node                                   | 120 |

| 54. | Simple Paths from a Previous Synchronization Node                              | 122 |

| 55. | Adjusted Source Timing of io for a Previous Synchronization Node psn           | 123 |

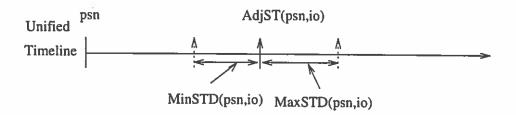

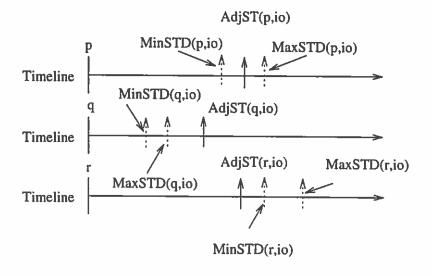

| 56. | Multiple Previous Synchronization Nodes                                        | 124 |

| 57. | Unification of Timelines for Multiple Previous Synchronization Nodes .         | 125 |

| 58. | An Example of Control Flow Graph for Timing Sensitivities                      | 126 |

| 59. | Previous I/O Nodes for io                                                      | 128 |

| 60. | MaxPIO(io) and MinPIO(io)                                                      | 129 |

| 61. | MaxMin(io) and MinMax(io)                                                      | 129 |

| 62. | Phase 1: Finds $\Delta(G_M)$ and $MaxPIO(v)$ and $MinPIO(v)$ for All $v \in V$ | 135 |

| 63. | Algorithm for $P_1T_2()$                                                       | 136 |

| 64. | After Initialization in Phase <sub>1</sub> ()                                  | 138 |

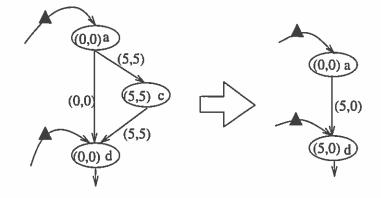

| 65. | Before and After $P_1T_2(a,c,d)$                                               | 139 |

| 66. | Before and After $P_1T_2(a,d,e)$                                               | 139 |

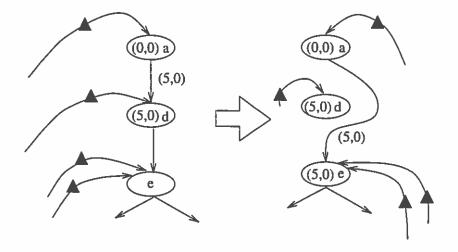

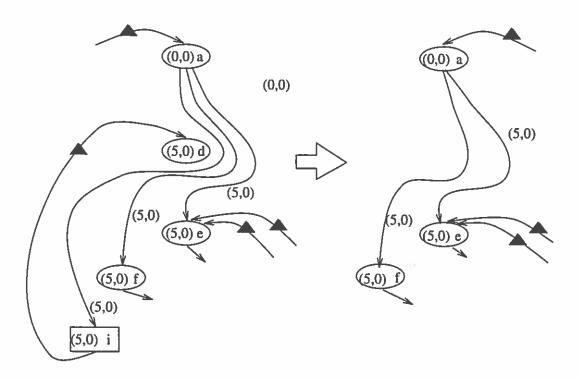

| 67. | Before and After $P_1T_2(a,i,d)$                                               | 140 |

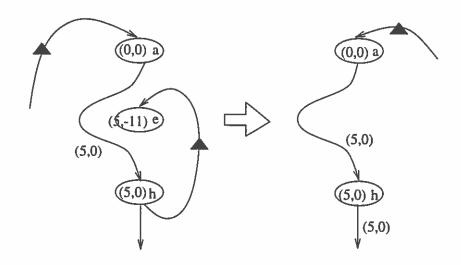

| 68. | Before and After $P_1T_2(a,h,e)$                                               | 141 |

| 69. | Phase II: Finds Relative Timing Sensitivity of $G_M$                           | 143 |

| 70. | Algorithm for $P_2T_2()$                                                       | 144 |

| 71. | The Control Flow Graph After Phase I                                           | 145 |

| 72. | Insertion of Synchronization at io                                             | 153 |

| 73. | Legal but Not Positive                                                         | 154 |

| 74. | Unsafe but Positive                                                            | 156 |

| 75. | After The Insertion of Synchronization on io                                   | 157 |

| 76. | Algorithm for Timing Optimization by Inserting Local Synchronizations          | 162 |

| 77. | An Example of Control Flow Graph for Optimization                              | 164 |

|     |                                                 | xvii |

|-----|-------------------------------------------------|------|

| 78. | After The Two Inner-Most Intervals are Reduced  | 165  |

| 79. | After All Sub-Intervals are Reduced             | 166  |

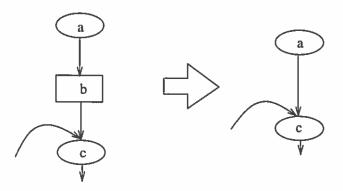

| 80. | Before and After $IST_2(a,b,c)$                 | 168  |

| 81. | Before and After $IST_2(a, p, d)$               | 169  |

| 82. | After The Insertion of a Synchronization on $e$ | 170  |

| 83. | An Example for Lazy Synchronization             | 171  |

| 84. | Algorithm for LazySync()                        | 172  |

| 85. | Timing Sensitivity with Lazy Synchronization    | 173  |

| 86. | Source and Target Control Flow Graphs           | 176  |

| 87. | Multiple Local Clocks                           | 177  |

)

)

)

)

)

0

)

)

#### CHAPTER I

### INTRODUCTION AND RATIONALE

The goal of this thesis is to investigate timing issues in Binary-To-Binary Translation (BBT) of real-time applications. While BBT provides a means of smooth migration of legacy software to newer architectures, it does not handle real-time applications properly. In real-time applications, it is often the case that doing something too quickly is as unacceptable as doing it too slowly. Thus, the translation of real-time applications must preserve timing equivalence of all visible events as well as semantic equivalence of the source application programs. The TIBBIT [14, 13] (Timing Insensitive Binary to BInary Translation) project introduced the problem of providing timing equivalence in binary-to-binary translation of real-time applications. The TIBBIT system delays the execution of the target program at regular intervals assuming the target machine is faster than the source machine. However, the TIBBIT system does not guarantee timing equivalence of the generated target binary programs when some instructions take more time on the target machine. This thesis provides a method to guarantee the timing equivalence of the TIBBIT-generated target binary programs. Major questions this thesis answers include:

How to guarantee timing equivalence of the TIBBIT-generated target binary programs.

- What are the necessary and sufficient conditions to guarantee timing equivalence of the generated target programs.

- How to convert a target binary program that is not timing equivalent into an equivalent one.

- How to minimize timing differences between source and target programs.

# Binary-to-binary Translation

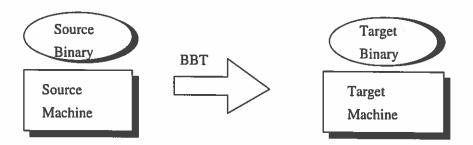

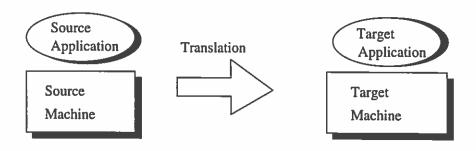

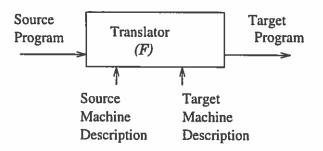

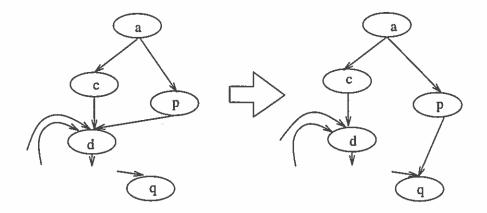

Binary-to-binary translation (BBT) is a method that takes a binary executable program (source binary) for a machine (source machine) and translates it into another executable program (target binary) to run on another machine (target machine), without referencing the original source program[51, 5]. The translated target binary program is a sequence of target machine instructions that reproduces the behavior of the source binary program. Figure 1 depicts the binary-to-binary translation scheme.

Figure 1: Binary-to-binary translation

The main advantage of this approach is that it is not necessary to have access to the original source program in order to perform the translation. A complicated application includes many software components developed using many different tools and compilers. One example of this is Microsoft Word, which is partly written in its

own macro language, with other portions written in C and assembly language. Porting this complicated software to a new architecture requires all tools and compilers available on the target machine before one starts. BBT provides a method to avoid this complication. The BBT technique has been used by many companies such as IBM [50], DEC [51], Tandem[5], and Apple.

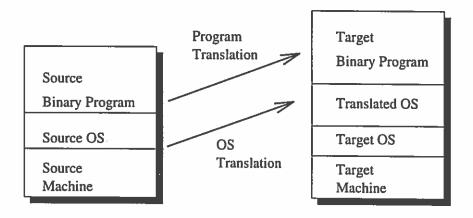

The translation of a binary code involves two program translations. One is the application binary code translation and the other is operating system code translation as shown in Figure 2.

Figure 2: Components of binary-to-binary translation

)

5

Translation of operating system code involves many complicated issues as discussed in [50]. We concentrate on real-time embedded-systems where the operating system and application binary program are combined together.

The main disadvantage of the BBT approach is performance degradation. In general, for the given set of instructions on the source machine, finding an optimal set of instructions on the target machine that reproduces the behavior of the source instruction set is a difficult problem. Also, some conditional statements must be added to make sure the architectural differences between the two machines are handled

correctly. Detailed discussion on these issues can be found in [50].

)

)

# Binary-to-binary Translation of Real-Time Applications

Previous Binary-to-binary Translation (BBT) approaches provide only semantic equivalence between source and translated target programs where the optimization goal is reducing the total execution time of the program on the target machine.

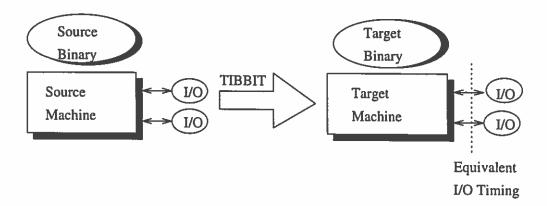

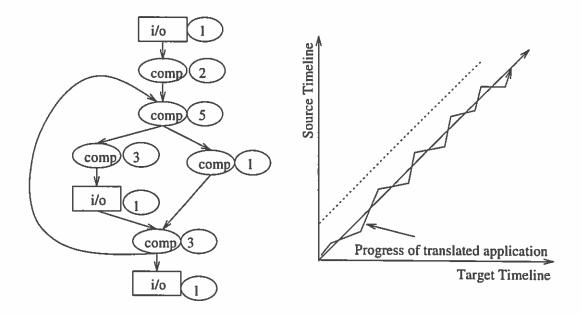

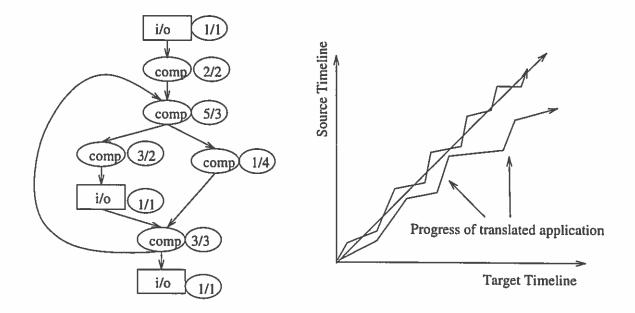

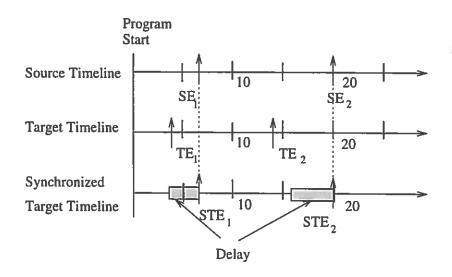

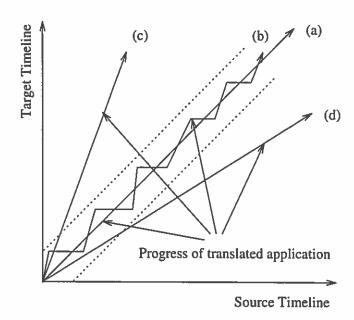

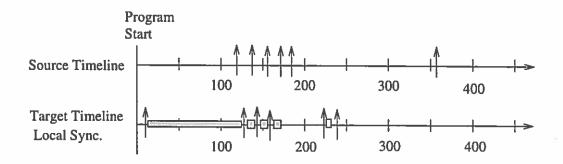

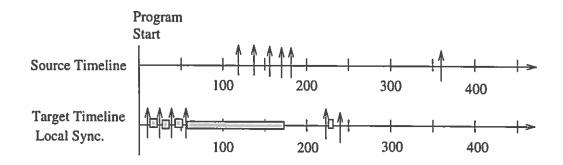

For real-time applications, however, the translator must preserve the timing equivalence as well as semantic equivalence of the source binary program. In this case, the goal of optimization is to reduce the timing difference between source and target programs. Figure 3 depicts the problem of preserving the timing equivalence of all visible events (i/o events).

Figure 3: The problem of providing the timing equivalence between source and target programs

The TIBBIT project [14, 13] addressed this timing issue, i.e., the problem of preserving the timing equivalence between source and translated target programs. In TIBBIT, the time required for each basic block on the source machine is computed. While running on the target machine, the TIBBIT system compares source and target timing at regular intervals and adjusts the execution of the target program. The

translated target program executes faster than the source on the target machine, but is periodically delayed.

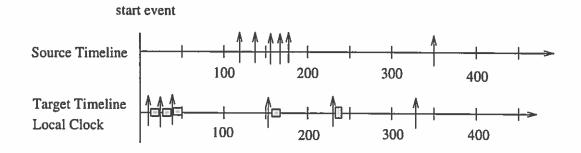

Figure 4: TIBBIT algorithm to provide timing equivalence

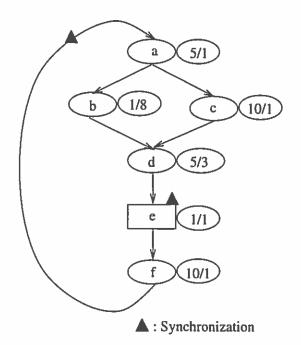

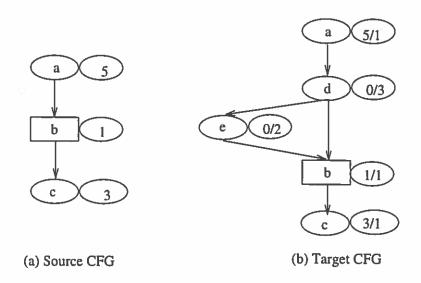

The example shown in Figure 4 depicts the algorithm used in TIBBIT. A node v in the control flow graph has an extra node that contains the execution time required on the source machine  $M_S$ , denoted by  $(ExecTime(v, M_S))$ . A limitation of TIBBIT is that it generates timing equivalent target binary programs only if all basic blocks take less time on the target machine.

#### Rationale

To provide timing equivalence in binary-to-binary translation, it is important to know the processing speed difference between the two machines, source and target. At minimum, the target machine must be faster than the source machine. However, the concept of processing speed difference of two machines is ambiguous. Modern

processors, such as RISC-based architectures, achieve their speedup over old processors through optimization of the most frequently used instructions while paying some penalty for less frequently used ones. On average, these newer processors are faster than older ones, but some instructions are actually slower than those of corresponding instruction sequences in the old processors.

Also, some translation overhead exists. As mentioned, it is a difficult problem to find the optimal corresponding set of target machine instructions for the given set of source machine instructions. In addition, there exists runtime overhead added to target binary programs. Some information that is available to higher-level translators is not available to a binary-to-binary translator. Thus, even when all corresponding instructions in the target machine take less time than the source machine instructions, some basic blocks in the translated target binary program may take longer on the target machine, simply because of translation overhead.

For these two reasons, the current TIBBIT system is not sufficient. When there exist some basic blocks that take a longer time on the target machine, the execution time difference between source and target program cannot be maintained by delaying the program execution (synchronization) on the target machine.

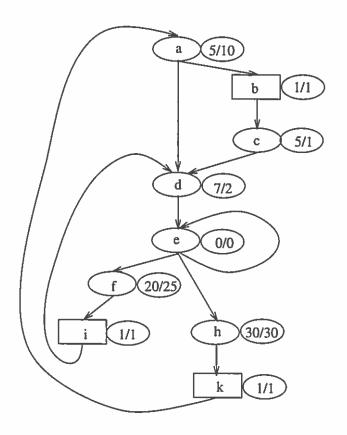

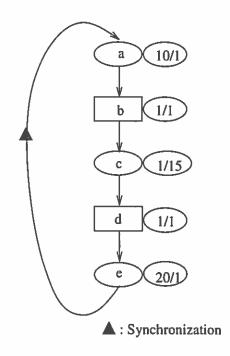

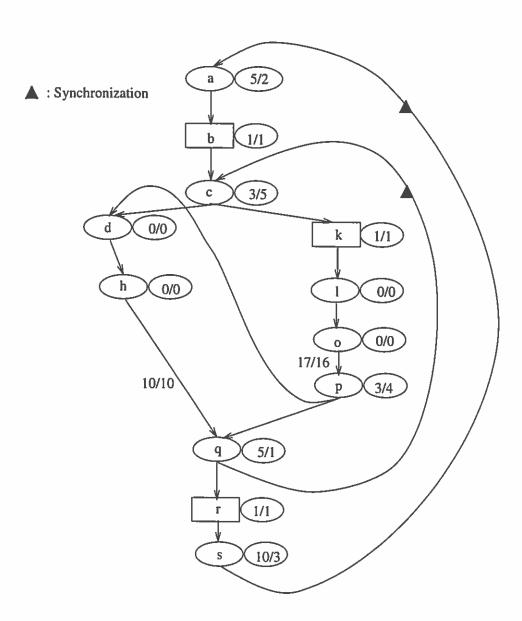

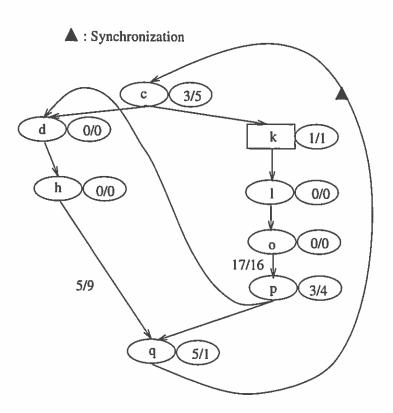

Consider the example given in Figure 5. We assume that the time required to execute a given basic block is computable for both source and target machines. We also assume that the required execution time for all i/o instructions remain the same on the target machine. Each node v in the control flow graph has an extra field containing the execution time required on both source and target machines for the node v, represented as  $(ExecTime(v, M_S)/ExecTime(v, M_S))$ . The target machine is faster than the source machine on average. However, one basic block

takes a longer time on the target machine. When executed on the target machine, the application may execute faster or slower depending on how often this slow basic block executed at the particular execution. When the application executes faster on the target machine, inserting synchronizations on the target program provide timing equivalence. However, when the application executes slower on the target machine, inserting synchronization does not provide timing equivalence.

Figure 5: Timing equivalent translation with slower instructions

Considering these factors, the goal of this research is to develop a method that analyzes a program to determine if it is always possible to execute a program timing equivalence.

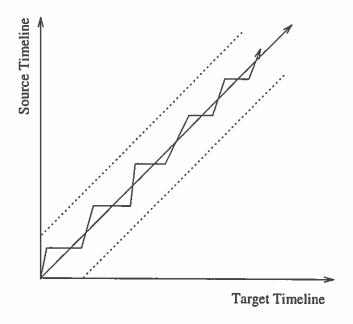

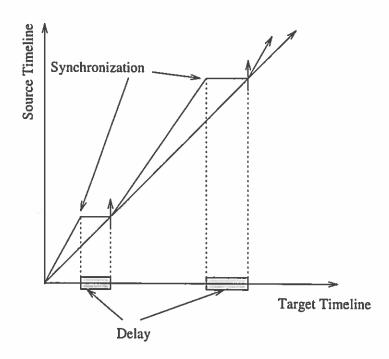

Here, we are to test if the maximum timing difference between source and target (the maximum drift) can be bounded by a constant. The maximum drift between source and target applications is shown in Figure 6. In the graph, the timing difference between source and target is bounded by a constant denoted by the distance between

two dotted lines.

Figure 6: Timing difference between source and target applications limited by a constant

This dissertation answers the following questions.

- When is the maximum drift bounded by a constant?

- How to find the maximum drift (the constant) if it is bounded?

- How to ensure that bounds exist?

- How to reduce the maximum drift?

To answer these questions, we assume the following.

- The control flow graph of the translated target program is given with execution time required for each basic block on both source and target machines.

- Environments, such as networks and i/o devices, remain the same, i.e., only the

processor and possibly part of the memory system are replaced.

#### Related Work

# Binary-to-Binary Translation

Many commercial companies use binary-to-binary translation schemes to provide a speedy upgrade path to newer architectures. Most of these binary-to-binary translation schemes have been developed with a particular source and target platform in mind. The optimization goal of these binary-to-binary translators is to minimize total execution time on the target machine. Issues of providing timing equivalence for real-time applications are completely ignored.

#### <u>DEC</u>

)

Kronenberg [37] and Sites [51] at Digital Equipment Corporation (DEC) use binary-to-binary translation techniques to port VAX VMS, MIPS Ultrix, and 80x86-based programs to the Alpha architecture. They successfully ported a large number of applications to the new architecture in minimal time. Because the Alpha architecture was designed with binary translation of MIPS code in mind, the performance of binary translated programs are comparable to that of native compiler generated programs.

#### <u>IBM</u>

Silberman and Ebcioglu at International Business Machines (IBM) developed a binary-to-binary translator that supports migration of system code as well as self-modifying code [50]. Applications are represented in both "migrant" and "native" forms, and a hardware-assisted "migrant engine" is used to execute sequences of code when the native engine fails due to either untranslatable or self-modifying code.

## Tandem Non-Stop Systems

Tandem Non-Stop Systems used a BBT system [5] to upgrade all of its vendor and user software from a proprietary stack-based CISC architecture to new R3000-based RISC machines. Both the operating system and applications were ported, and relied upon a combination of static translation and run-time interpretation.

#### HP

)

D

D

Bergh [7] at Hewlett Packard relies on a combination of object code translation and emulation to execute HP3000 software on the HP Precision architecture family, using a "compatibility mode" environment in the target operating system.

#### **Hunter Systems**

Hunter Systems developed a system called XDOS [25] for binary-translating DOS applications to UNIX environments. The system was intended to be used by developers as an aid to porting, and relied upon a combination of human- and machine-translation techniques.

#### Decompilation

Decompilation is a process that reads a binary executable program and translates it into an equivalent program in a high-level language. Decompilation techniques are useful in understanding the binary code during the maintenance process [8] and in verifying compiled binary programs for safety-critical systems [52, 46]. All of these systems ignore timing issues that occur in many real-time systems. One exception is the original version of the TIBBIT translator which takes an executable binary

program and generates C code that is both semantically and temporally equivalent to the binary code.

# Breuer and Bowen

Breuer and Bowen [8] describe a method to decompile programs generated by a simple Occam-like compiler. They construct an abstract syntax tree from the executable binary code and generate an equivalent program in the logic programming language, *Prolog*.

#### Spector and Pavey

NASA used a decompilation technique [52] to verify the program called System Management (SM), which is used in their space shuttle. The decompiler decompiles the memory images generated by the SM preprocessor and compare the results with the original inputs.

Pavey and Winsborrow [46] also used a decompilation technique to compare the source code and PROM contents of a safety-critical system used in the UK nuclear industry.

#### Gough and Cifuentes

Gough and Cifuentes [11, 10] describe issues in decompiling 80x86 binary programs. Many optimization techniques that have been used in optimizing compilers are used in their decompiler. Their goal is similar to that of binary-to-binary translation but it also provides portability.

## Cogswell and Segall

A version of the TIBBIT translator [13] takes an executable binary program and generates C code to provide portability. The generated C code can be compiled for any target machine. This version of the TIBBIT translator computes execution times on the source machine for each basic block. For each basic block, the translator inserts C code that accumulates the execution time of basic blocks in a global counter that accumulates these execution times. The TIBBIT-generated target C program is compiled by a C compiler on a specific machine. The TIBBIT system interrupts the execution of the target binary program at regular intervals and delays the execution if it runs too fast.

# Timing Analysis

For a real-time program, we must be able to predict the computation time of the program on the target machine. There are a number of techniques that predict the execution times of programs written in both low-level and high-level languages.

In our analysis, it is assumed that the execution time required for any basic block on both source and target machines is computable. In Chapter IX, we discuss how to deal with instructions that have non-constant execution time.

#### High-level Languages

Shaw [49, 45] describes a method to predict the execution time of high-level language statements. The method takes a program written in a high-level language (C), and bounds for each loop, and predicts the upper and lower bounds on execution time of each source level construct. The method decomposes programs into basic blocks

and predicts the implementation of each basic block. The execution time of each basic block is determined for a specific target machine. The accuracy of the predicted execution time is dependent on how accurately it can predict the implementation.

#### Low-level languages

Most older processors have a constant execution time for each instruction. If we know the bounds of each loop, it is not difficult to compute the execution time of programs written in low-level languages such as assembly language. However, the execution time of instructions on a newer processor with pipelines and cache is not constant. Issues of computing tight worst-case execution time of instructions for these machines are discussed in [40, 19, 60].

Zhang [60] presents a method to find worst-case execution times of instructions on pipelined processors.

Caches are extensively used in most recent computer systems to improve performance of the system. While caches improve performance of the system on average, they impose significant difficulties on timing analysis. Min [40] describes an analysis technique that accurately predicts the worst-case execution times of programs in the presence of caches.

Most timing analysis techniques are machine dependent. Since machine architectures evolve rapidly, developing a retargetable timing analysis method is important. Harmon [19] describes a portable timing analysis technique called *micro-analysis*. It predicts best and worst-case bounds for point-to-point execution times, based on a pattern matching scheme that uses a machine description and a set of timing rules. This scheme is capable of taking into account the architectural characteristics of the target processors and their effect on instruction execution time.

# Translation of Real-Time Programs

Translation of real-time applications must preserve both functional and temporal requirements specified in the source programs. Temporal requirements are specified either implicitly or explicitly depending on the language used in the source program. Some source programs are written in higher-level languages with real-time constructs in which case all temporal requirements are expressed explicitly. Other are written in assembly language in which cases all temporal requirements are expressed implicitly.

#### RT-ASLAN

0

RT-ASLAN [6] is a real-time programming language which allows programmers to express timing constraints explicitly in a program. The kind of systems specifiable in RT-ASLAN are loosely coupled systems communicating through formal interfaces. From RT-ASLAN specification, performance correctness conjectures are generated. These conjectures are logic statements whose proof guarantees the specification meets critical time bounds.

#### Real-Time Euclid

Real-Time Euclid [33] does not allow some general programming constructs, including while(), recursion, and recursive data structures. The schedulability analyzer of Real-Time Euclid computes the worst-case execution time of a task by assuming the execution time of each instruction is constant.

#### Modechart

Mok [27] describes a real-time specification language called Modechart. The semantics of Modechart is given in terms of RTL (Real Time Logic) [26] that is amenable to reasoning about the timing of events. The translation of a Modechart specification into RTL formulas results in a hierarchical organization of the resulting RTL assertions. This hierarchical organization allows filtering of assertions that concern lower levels of the abstraction.

#### <u>Flex</u>

)

D

In many hard real-time systems, obtaining an approximate result before the deadline is more desirable than obtaining an exact result after the deadline. Flex [31] is a real-time programming language that allow computations to return imprecise results. This provides the flexibility needed to guarantee all important events meet their deadlines under all circumstances.

#### TCEL

In most real-time programming languages, timing constraints can be specified on blocks of code. In most real-time applications, however, these timing constraints are imposed on observable i/o events. TCEL [17] allows a programmer to express timing constraints between i/o events. In TCEL, unstructured constructs such as goto are not allowed. The compiler takes programs written in this high-level language and generates binary executable target programs. The compiler tests if the real-time scheduler can schedule the program so that the timing constraints expressed in the program can be guaranteed. If not, the compiler decomposes the program

into reference blocks and constraint blocks. By moving code in reference blocks, the compiler improves schedulability of the program. If the program is not schedulable with a single processor, the compiler schedules it with multiple processors. If worst case timing of the control structure in the constraint blocks does not meets its timing requirements, it is not schedulable.

Since the compiler takes a program written in a high-level language and does not allow unstructured constructs, the control flow of the program is known and all control flow in constraint blocks is well structured.

Since we take binary executable programs as input, control flow of the programs, which may be unstructured must be determined. We use interval analysis to find the control flows in the program. The timing requirements also have to be found by analyzing the control flow of the program. The model we use here is more general than that of TCEL in the sense that timing requirements do not have to be expressed explicitly between constraint blocks.

#### **TIBBIT**

3

The TIBBIT system is a binary-to-binary translator for real-time systems. In binary source codes, timing requirements are implicitly expressed. Thus, the TIBBIT system must analyze the timing of all instructions in the binary source code and generate a target binary code which mimics its timing behavior. It assumes that execution time for an instruction on the source machine is constant.

# Program Analysis

Program analysis is to facilitate optimization of programs where the meaning of optimization is subjective. To optimize programs, a compiler must perform some sort

of program transformation based on the information obtained through the analysis of source programs. Typical two analyses a compiler performs are control flow and data-flow analysis.

# Control Flow Analysis

9

9

Control flow analysis [2, 1] is used to find the control structure of a program so that the information can be used for optimizing transformations and other analysis. In control flow analysis, the most important goal is finding loops. One way to find loops is to find strongly connected regions (SCR) as discussed in [53]. While this methods finds all cycles in a control flow graph, it does not reveal hierarchical structures of the program.

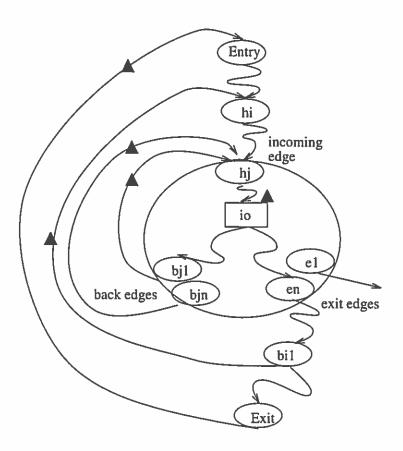

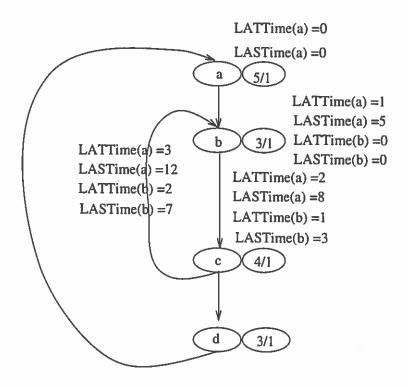

Another way to analyze the structure of a control flow graph is interval analysis, which finds hierarchical structures in the control flow graph. Interval analysis, as formulated by Allen and Cocke, provides a way to solve data flow equations more efficiently. There are a number of quite different proposals in defining intervals [3, 2, 20, 18, 4, 48]. In general, an interval is a special form of loops. The specific definition of interval we use is the one defined in [18].

# Data-flow Analysis

Data-flow analysis [43, 30, 20, 21, 23] is used to find where variables (data) are defined and used. Data-flow information is required for many optimization techniques. We use similar analysis methods to find how the timing differences between source and target machines flow over the control flow graph.

# Comparison to Previous Work

All of the binary-to-binary translators and decompilers discussed above ignore timing issues required in translation of real-time applications. Most translators for real-time programs deal with programs written in a high-level language, where timing constraints are explicitly expressed. We are dealing with binary programs where timing constraints are expressed implicitly.

The current TIBBIT [13] system provides some degree of timing equivalence in binary-to-binary translation of real-time applications. The condition required to make the TIBBIT approach work is that every basic block takes less time on the target machine. This condition is stronger than the conditions presented here for timing equivalent translation. Even with stronger conditions, the TIBBIT system does not provide timing equivalence since it uses a dynamic synchronization scheme, e.g., synchronize every 10 ms. We present necessary and sufficient conditions for timing equivalent and invariant translation even in cases where some basic blocks in target binary are slower than corresponding block in the source binary program. When the timing equivalent translation is not possible, we provide the worst case timing error.

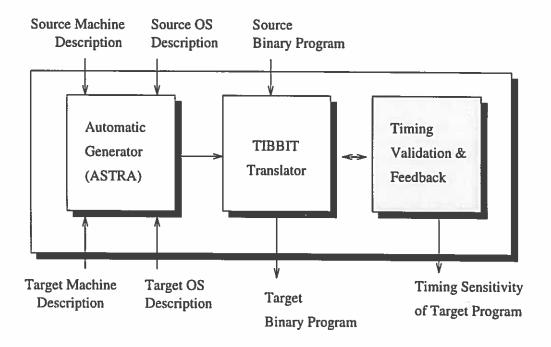

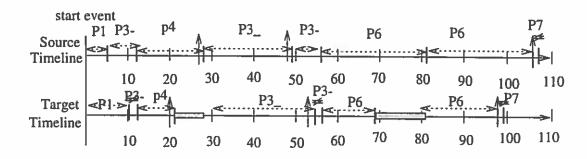

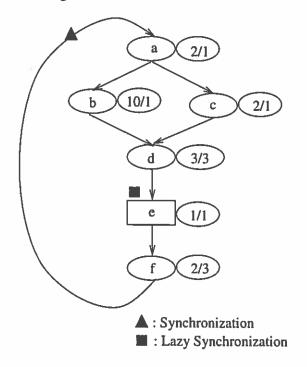

#### TIBBIT Project Overview

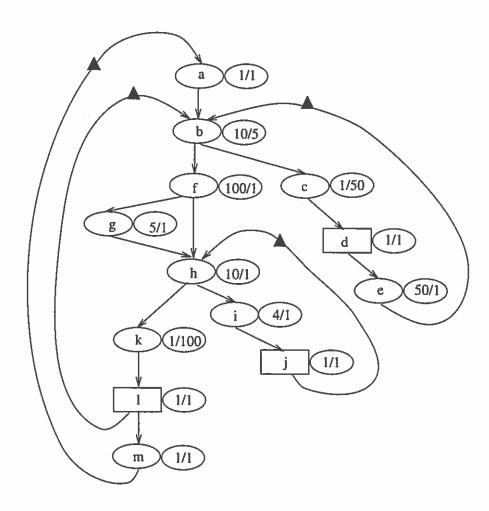

This research has been conducted as part of the TIBBIT project. An overview of the TIBBIT project is depicted in Figure 7.

ASTRA is a program that takes the description of source and target OS's and machines and generates a TIBBIT translator. This thesis describes partially the Timing Validation and Feedback part of the project. New algorithms are added to test

Figure 7: The overall structure of TIBBIT

if the generated target binary program is timing equivalent with respect to the source binary program. It also provides methods to reduce the maximum drift between the source and target programs.

#### Summary of Contributions

The goal of this thesis is to investigate timing issues in binary-to-binary translation of real-time applications. For the translation of real-time applications, preserving both semantic and timing equivalence are important, where others require preservation of semantic equivalence only. With the given source and translated target binary applications, the necessary and sufficient conditions that can guarantee timing equivalence have been found. Also, a number of optimization techniques which reduce the timing difference between the source and target applications are applied. The major

)

contributions of this dissertation include the following:

- A framework to analyze timing equivalence between source and target programs.

- Necessary and sufficient conditions for timing equivalent and timing invariant translations.

- Relevant timing sensitivities for "real-world" usage.

- A method to find timing sensitivities of the given target program.

- Optimization techniques for timing equivalence.

# Thesis Organization

The rest of this dissertation is organized as follows. In Chapter 2, we define real-time system terminology and provide necessary background on real-time systems. In Chapter 3 we define basic terminology for compiler-related concepts to be used throughout this dissertation. In Chapter 4 we define timing equivalence between source and target systems. In Chapter 5 we present an analysis algorithm for timing equivalence testing. In Chapter 6 we present two synchronization schemes which enforce timing equivalence. In Chapter 7 we present algorithms that find timing sensitivities for the given source and target programs. In Chapter 8 we present algorithms that minimize the timing difference between the source and target programs. In Chapter 9 we discuss a number of implementation issues. Finally, in Chapter 10 we summarize our result and provide future research directions.

## CHAPTER II

#### BACKGROUND

This chapter presents necessary background on real-time systems. We first define terminology related to time and events. We then present issues on real-time languages, programs and translators of them.

# Timelines and Events

)

)

)

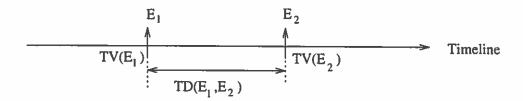

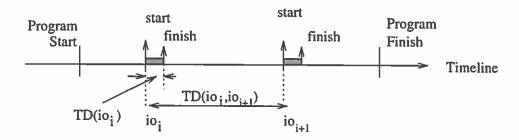

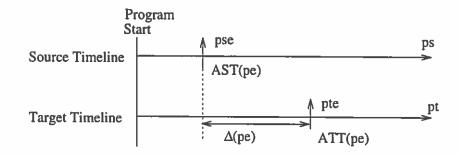

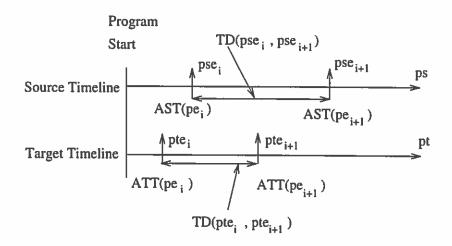

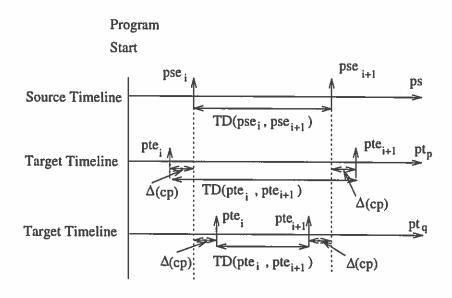

A timeline is a progression of time from the past to the future. An event, E, is an occurrence at a point in time, i.e., a happening at a cut of the timeline, which itself does not take any time. These terms are borrowed from Koepet and Ochsenreiter [36]. The time value of an event(E), denoted by TV(E), is the value of the time at the event E. The time duration of two events  $E_i$  and  $E_{i+1}$ , denoted by  $TD(E_i, E_{i+1})$ , is the time interval between these two events, i.e., the section of the timeline between the two events.  $TD(E_i, E_{i+1})$  is defined as Equation II.1. Figure 8 depicts timeline, events and time duration between two events.

$$TD(E_i, E_{i+1}) = |TV(E_{i+1}) - TV(E_i)|$$

(II.1)

# Real-Time Systems

An application is a program running on a specific machine. A real-time application is an application that interacts with the external world in a way that involves

Figure 8: Timeline, events and time duration between two events.

time-related conditions. A real-time system is a more general term to refer to a combination of software and hardware that deals with outside events that have time constraints. The main characteristic of real-time programs is the existence of temporal (or timing) requirements in addition to functional requirements. Temporal requirements specify timing constraints for sequences of events, while functional requirements specify required transformations of inputs to produce outputs of the system. Typical real-time systems are control systems (manufacturing systems, robotics), monitoring systems (patient monitoring, air traffic), and communication systems. The potentially high cost associated with incorrect operations of these systems has created a demand for rigorous testing and implementation for both functional and temporal requirements.

)

## I/O Events

An application generates i/o events to communicate with outside systems, i.e., receives inputs and generates outputs. All observable events from outside the system are i/o events. Most systems generate these i/o events by reading and writing data from/to one or more of the system i/o ports. Since i/o events are generated by a computer, every i/o event takes some time to complete. Thus, every i/o event io has two events associated with it,  $start(io_s)$  and  $finish(io_f)$ . The time duration of an i/o

event io, denoted by  $TD(io_s, io_f)$  or TD(io) for short, is the time interval between  $io_s$  and  $io_f$ . An i/o event is represented by its start event. Thus, the time duration of two i/o events,  $io_i$  and  $io_{i+1}$ , is the time interval between start events of  $io_i$  and  $io_{i+1}$ . An application P has two special events,  $Program\ Start(P_S)$  and  $Program\ Finish(P_F)$  events, which are not i/o events but we treat as i/o events. Both  $P_S$  and  $P_F$  events take no time to complete. Figure 9 shows two i/o events  $io_i$  and  $io_{i+1}$  with program start and finish events.

0

Figure 9: Timeline, i/o events and duration between two i/o events.

Suppose an application PS is running on a machine  $M_S$ . The application time value (ATV) of an i/o event (PSE) in PS, denoted by  $ATV(PSE, M_S)$ , is a function that returns the time duration from the point of the  $Program\ Start(PS_S)$  to PSE. The  $ATV(PS_S, M_S)$  is zero and  $ATV(PS_F, M_S)$  is equal to the total execution time of PS on  $M_S$ . The  $ATV(PS_F, M_S)$  is  $\infty$  if the application never finishes. Now, suppose the application PS is translated into PT so that it can be executed on a machine  $M_T$ . The  $ATV(PT_S, M_T)$  is zero and  $ATV(PT_F, M_T)$  is equal to the total execution time of PT on  $M_T$ . Here,  $ATV(PS_S, M_S) = ATV(PT_S, M_T) = 0$  but  $ATV(PS_F, M_S)$  is not necessary equal to  $ATV(PT_F, M_T)$ .

## Machine Models

Suppose a real-time application (source application) running on a specific machine (source machine) is translated into another application (target application) so that it can run on another machine (target machine) as shown in Figure 10.

0

Figure 10: A source application for source machine and a translated target application for target machine.

To provide timing equivalence on the translated target application, the target machine must be at least as fast as the source machine. However, it is not so clear what we mean by "a machine is faster than the other." We thus define the meaning of faster and slower machine more clearly.

Let the sets  $I_T$  and  $I_S$  be instruction sets of machines  $M_T$  and  $M_S$ , respectively. Let OCIS be an ordered combination of instructions, where every element  $ocis \in OCIS$  is in  $I_S$ . Also, let OCIT be an ordered combination of instructions, that is functionally equivalent to OCIS, where every element  $ocit \in OCIT$  is in  $I_T$ . The execution time required for an ordered combination of instructions OCI on machine M is written as ExecTime(OCI, M). We say machine  $M_T$  is definitely faster than machine  $M_S$  if for all OCIS, there exists a functionally equivalent set of instructions OCIT such that OCIT takes less time than OCIS, i.e.,

$$(\forall OCIS)[\exists OCIT \ni ExecTime(OCIT, M_T) \le ExecTime(OCIS, M_S)]. \tag{II.2}$$

Machine  $M_T$  is said to be average faster than machine  $M_S$  if for any large n,

$$\frac{\sum_{i=1}^{n} ExecTime(OCIT_{i}, M_{T})}{n} \leq \frac{\sum_{i=1}^{n} ExecTime(OCIS_{i}, M_{S})}{n}.$$

(II.3)

## Synchronization

Suppose source and equivalent target applications are running on source and target machines, respectively. The goal of synchronization is the elimination of timing differences between the two systems. Synchronization of the target application with respect to the source application can be always achieved by delaying the execution of the target application when the target machine is definitely faster than the source machine.

While synchronization can be performed at any time/place in the target application, the timing of i/o events is significant for real-time applications. The reason is that only i/o events are observable from the outside. Thus, we are only concerned with timing differences between corresponding i/o events on source and target applications. A target application that is semantically equivalent to the source application said to be timing equivalent if all i/o events in the target application are synchronized with respect to the corresponding i/o events in the source application.

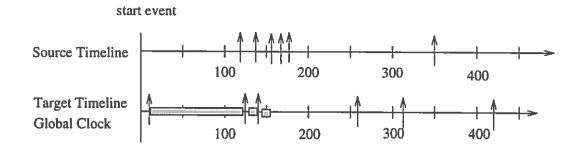

)

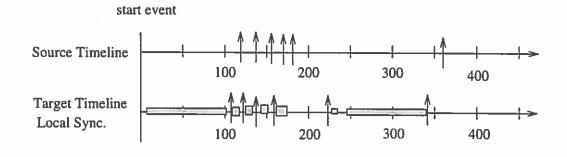

9

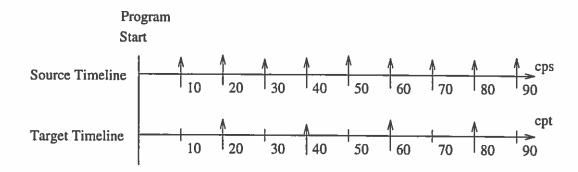

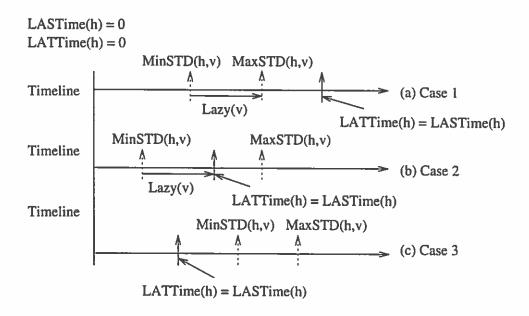

Figure 11 shows such an example. An i/o event is represented as  $\uparrow$ . There are two i/o events,  $SE_1$  and  $SE_2$ , in the source application. The application time value of these events on the source machine are  $ATV(SE_1, M_S) = 6$  and  $ATV(SE_2, M_S) = 6$

Figure 11: Synchronization of corresponding i/o events

0

20. The application time value of corresponding events,  $TE_1$  and  $TE_2$ , on the target application are  $ATV(TE_1, M_T) = 4$  and  $ATV(TE_2, M_T) = 14$ . Through synchronization, these two applications are timing equivalent, i.e.,  $ATV(STE_1, M_T) = 6$  and  $ATV(STE_2, M_T) = 20$ .

The same synchronization also can be viewed as shown in Figure 12. Synchronization can be performed either statically or dynamically. Dynamic synchronization methods decide synchronization points at run-time. The TIBBIT system [14] uses a dynamic synchronization method. In TIBBIT, the target application is synchronized at regular time intervals, every 10ms for example. Static synchronization schemes decide synchronization points statically over the control flow graph so that synchronization is performed every time the particular point in the control flow graph is executed. One simple static synchronization method is synchronization of all i/o nodes.

Figure 12: Synchronization of source and target programs

)

D

0

# Real-Time Languages and Programs

In real-time programs, temporal requirements must be expressed in addition to functional requirements. These temporal requirements can be expressed either explicitly or implicitly in the program. Most older real-time programs are written in assembly languages because of lack of suitable real-time programming languages and compilers. Timing requirements in this case are expressed implicitly in the program. Programmers must embed timing requirements in the program implicitly by inserting some delay code. More recently, real-time languages are proposed and developed to allow programmers to express timing constraints explicitly in the program by providing timing constructs in the programming language. Language constructs to express timing requirements are discussed in [15, 33, 6].

Figure 13 shows an example of a real-time program written in a high-level

real-time programming language. This example has three i/o nodes, i.e., one input (receive()) and two outputs (send()). In this program, the timing requirements are explicitly specified in the program with special timing constructs, every (stime) do. In this specification, timing constraints are imposed on blocks of code.

```

every 10ms do

receive(Sensor, &data)

cmd1 = nextCmd(state, data, s1);

cmd2 = nextCmd(state, data, s2);

state = nextState(state,data);

send(Actuator1, cmd1);

send(Actuator2, cmd2);

enddo

```

Figure 13: A simple real-time program

In most real-time applications, however, these timing constraints are imposed on observable i/o events. More advanced real-time programming languages called event-based real-time programming languages are proposed to allow the programmer to specify timing constraints between observable events. One such real-time programming language is Time-Constrained Event Language (TCEL)[17]. Figure 14 shows the same example of real-time program written in TCEL (also see related work section in Chapter I). In this program, the timing constraint are specified between i/o events.

Once a program is written, it is the compiler's duty to translate the real-time program into target machine code which preserves both temporal and functional requirements specified in the source program.

```

every 10.0 ms do

receive(Sensor, &data)

start after 1.0 ms finish within 5.0 ms

begin

cmd1 = nextCmd(state, data, s1);

cmd2 = nextCmd(state, data, s2);

state = nextState(state,data);

send(Actuator1, cmd1);

send(Actuator2, cmd2);

end

enddo

```

Figure 14: A simple real-time program with event-based timing constructs

)

)

#### Program Translation

In general, program translation can be viewed as a process that converts a program executable on one machine model to an equivalent program that is executable on another machine model. Consider a program written in a higher-level programming language. This program can be viewed as a program that is executable on the conceptual machine, which is described in the language specification. A translator (or compiler) converts this program into another program that is executable on a specific target machine. A translator takes source program and source and target machine descriptions and generates a target program which is an executable on the target machine. Figure 15 depicts such a translator.

A program translation can be formulated as a function as shown in Equation II.4, where TP is target program, SP is source program, SM is source machine, TM is target machine and  $\mathcal{F}$  is a translation function or translator.

Figure 15: Translator

$$TP = \mathcal{F}(SP, SM, TM). \tag{II.4}$$

The characteristics of the translator depend on a number of categories: equivalence between source and target programs, "optimality" of the generated target program, and input and output languages.

# Equivalence

While the equivalence test of two programs in general is an undecidable problem, two programs are said to be "equivalent" if all transformations performed by the translator are sound and complete within the boundary of "equivalence." Every translator must provide some degree of equivalence between source and target programs. We consider two different categories for the equivalence: functional (semantic) and temporal (timing) equivalence. For most systems, only semantic equivalence is required.

## Definition 2.1

D

D

A translator  $\mathcal{F}$  preserves semantic equivalence, denoted by TP  $\stackrel{SE}{=}$  SP, if SP and TP are semantically equivalent.

In this case, all functional requirements specified in the source program (SP) are preserved in the target program (TP). All compilers or translators must preserve the semantic equivalence. For real-time applications, however, preserving timing equivalence is also important.

#### Definition 2.2

)

0

9

A translator  $\mathcal{F}$  preserves timing equivalence, denoted by TP  $\stackrel{TE}{=}$  SP, if SP and TP are semantically equivalent and for all corresponding i/o events  $io_s$  and  $io_t$ ,  $ATV(io_t, M_T) = ATV(io_s, M_S)$ .

In this case, both functional and temporal requirements specified in the source program (SP) are preserved in the target program (TP).

# Optimality

The goal of optimization may vary depending upon system requirements. In most cases, the goal of optimization is to reduce the total execution time using fewer resources (performance optimization). Performance optimization has a long history [1, 3, 39]. However, the major goal of optimization for real-time systems is to meet the timing requirements specified in the source program, i.e., providing timing equivalence between two programs, source and target. One such example is TCEL [17, 16, 24]. The TCEL compiler optimizes target programs to comply with the timing constraints specified in programs.

# Input and Output Languages

Both input and output can be anything from binary object code to programs written in high-level languages such as C or Prolog. In *TCEL*, like most other com-

pilers, input programs are written in a higher-level programming language and the output is binary executable code. *Decompilers* [8] takes binary executable codes as input and generates high-level codes such as C or Prolog. *A binary-to-binary translator* [51] takes binary executable code for a machine and generates another binary code which is executable on another machine.

# CHAPTER III

## THEORETICAL TERMINOLOGY AND NOTATION

Most compilers use a form of control flow graph, an intermediate representation of programs, to analyze and optimize programs. This chapter explains our control flow graph used in timing analysis. We first provide some mathematical notations to define control flow graphs. We then define the control flow graph and spanning and dominator trees for it. A table providing a summary of notations is given at the end of this chapter.

## Set

A set S is a collection of distinct objects. An element s is a member of set S, written  $s \in S$ , if s is an object that is in the set S. The cardinality of a set |S| is the number of elements in the set S. A set is empty, written  $\emptyset$ , if |S| = 0. A set is an infinite set if  $|S| = \infty$ . A set S is a subset of T,  $S \subseteq T$ , if every element of S is also an element in T. A set S can be partitioned into k nonempty disjoint subsets whose union is equal to S.

## Directed Graph, Paths and Trees

A directed graph  $G = \langle V, E \rangle$  consists of a set of nodes V and a set of edges E, where each edge  $e \in E$  is an ordered pair of nodes, written  $\langle v_1, v_2 \rangle$ , and  $v_1, v_2 \in V$ . An edge e also can be denoted as  $v_1 \to v_2$ . If the edge  $v_1 \to v_2 \in E$ , the node  $v_1$  is called tail and  $v_2$  is called head of the edge. If  $v_1 \to v_2$  is an edge of G then  $v_1$  is the predecessor of  $v_2$  and  $v_2$  is the successor of  $v_1$ . The set SUCC(v) is the set of all successors of v and the set PRED(v) is the set of all predecessors of v. The in-degree of a node v is the number of edges of the form  $u \to v$ , and the out-degree of v is the number of edges of the form  $v \to w$ . A node is a source if its in-degree is zero and a sink if its out-degree is zero. A graph H is a sub-graph of G if  $V_H \subseteq V_G$  and  $E_H \subseteq E_G$  such that an edge in  $E_H$  has both the tail and head nodes in  $V_H$ .

A path p of length k is a sequence of nodes  $\langle a_0, \ldots, a_k \rangle$  such that there is an edge  $\langle a_i, a_{i+1} \rangle$  for all  $i = 0, \ldots, k-1$ . We say a node v supports a path p if v appears in p. A path  $\langle a_0, \ldots, a_k \rangle$  can be divided into smaller paths called sub-paths. A particular sub-path  $\langle a_0, \ldots, a_{k-1} \rangle$  of p is denoted by  $p^o$ . We say a sub-path  $\langle a_i, \ldots, a_j \rangle$  of  $\langle a_0, \ldots, a_k \rangle$  supports the path  $\langle a_0, \ldots, a_k \rangle$ . A trivial path is a path of length zero, i.e., a single node. A path is simple if all nodes in the path are distinct. A non-trivial path p from x to y is a cycle if x = y and is a simple cycle if it is a cycle and  $p^o$  is simple. An edge  $\langle v_1, v_2 \rangle$  is called a self looping edge if  $v_1 = v_2$ . For a given two nodes  $x, y \in G$ , there may exist many distinct paths which are denoted by the set p(x,y). The set p(x,y) can be infinite if there exist cycles between two nodes. The set of all simple paths from x to y is denoted by  $\sigma(x,y)$ .

9

D

A directed acyclic graph (DAG) is a directed graph with no cycles, i.e., any path between two nodes in a DAG is simple. A directed graph is cyclic if it is not a DAG. A tree of a directed graph is a DAG with the following three properties: There is a single source node, called root which has zero in-degree; every node in the tree except the root has in-degree of one; and for every node in the tree, there exists a simple path from the node root. If there is a path from u to v in the tree i.e.,  $u \stackrel{*}{\to} v$ , then

u is an ancestor of v and v is descendant of u. The node u is proper ancestor of v and v is a proper descendant of u if  $u \neq v$ , i.e.,  $u \stackrel{+}{\to} v$ . The node u is an immediate ancestor of v and v is an immediate descendant of u if the length of the path is one, i.e.,  $u \to v$ .

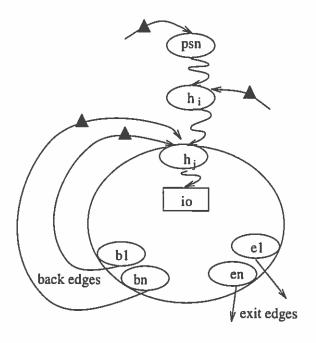

## Control Flow Graphs

Our control flow graph is a directed graph G with a set of nodes and edges. A node represents a basic block, where a basic block can be either an i/o basic block (denoted by a rectangle) or computation basic block (denoted by an oval). A computation basic block contains a sequence of instructions in which the flow of control enters at the beginning and leaves at the end, without halt or possibility of branching except at the end. If any instruction in a basic block is executed, all instructions in that basic block will be executed. An i/o basic block contains an i/o function call but nothing else.

9

0

Assume  $M_S$  is the source machine and  $M_T$  is the target machine. For each node  $v \in V$ , the execution time on source and target for v, denoted by EST(v), is an ordered set  $(ExecTime(v, M_S), ExecTime(v, M_T))$ . This ordered set is denoted as  $(ExecTime(v, M_S)/ExecTime(v, M_T))$  in the graph. We assume that our control flow graph is obtained from the translated target program, where it may contain some nodes that are not in the control flow graph obtained from the source code. If  $v \in V$  is not in the control flow graph obtained from the source code,  $ExecTime(v, M_S) = 0$ . The required execution time difference between source and target machine for a node  $v \in V$ , STD(v), is defined as  $ExecTime(v, M_T) - ExecTime(v, M_S)$ .

An edge represents potential flow of control between basic blocks. Conditional branches are represented by nodes with two successors. A control flow graph G can

be represented as a triple  $G = \langle V, E, Entry \rangle$ , where

- V is a set of nodes, where each node can be either an i/o node or a computation node;

- E is a set of edges which is subset of  $V \times V$ ;

- The Entry is a node in V with zero in-degree (source).

- $(\forall v \in V)[Entry \stackrel{*}{\rightarrow} v].$

)

0

A node  $v \in V$  with zero out-degree is called an *exit* node. There may exist multiple *exit* nodes in G. The set of all i/o nodes in G is denoted by IO(G).

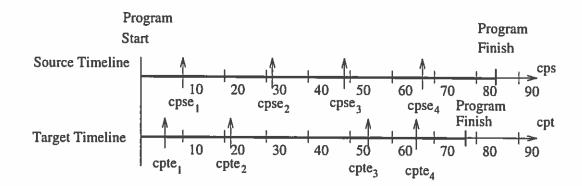

A complete path(cp) of G is a path from the Entry to an exit node. The set of all complete paths of G is denoted by CP(G). A cp is a complete simple path(csp) if it is simple. The set of all complete simple paths in the graph G is denoted by CSP(G). A  $cp \in CP(G)$  that is not a member of CSP(G) contains a  $csp \in CSP(G)$ . The set CP(G) is roughly equivalent to all execution instances of the program represented by the graph G. A node  $v \in V$  may support a  $cp \in CP(G)$  many times if it is in cycles in G. The set  $INST(v,cp) = \{iv_1,\ldots,iv_n\}$  represents instances of v on cp, where  $iv_i$  is an execution instance of v in cp. We denote a complete path cp over a specific control flow graph G as  $\{iEntry_1,\ldots,iExit_1\}$ , where  $iEntry_1$  abd  $iExit_1$  are the only instances of Entry and Exit nodes, respectively.

A complete path  $cp \in CP(G)$  is denoted by cps if it is running on the source machine. The set of all complete paths on the source machine is denoted by CPS(G). A complete path  $cp \in CP(G)$  is denoted by cpt if it is running on the target machine, while set of all complete paths on the target machine is denoted by CPT(G). An instance  $cpv_i$  on cp has corresponding instances on both cps and cpt, which are  $cpsv_i$

on cps and  $cptv_i$  on cpt. Here, cp is a conceptual path defined in the graph G while cpt is the execution of cp on target machine and cps is the execution of cp on source machine. Also, the path cpt can be viewed as a translated target path from cps by a translator.

The set SC(G) is the set of all  $simple\ cycles(sc)$  in G. A path is repeatable if it is in a cycle and non-repeatable if it not in a cycle. The number of executions for a repeatable path is not generally known statically while the number of executions for a non-repeatable path is at most one. A repeatable path is simple if it is in a simple cycle. Any repeatable path can be sub-divided into simple repeatable paths. Suppose a simple cycle sc is given. The  $maximum\ simple\ repeatable\ path$  of sc, denoted by msrp(sc), is  $sc^{\circ}$ .

The set of all maximum simple repeatable paths in G is denoted by MSRP(G). Any  $cp \in CP(G)$  is decomposable with a  $csp \in CSP(G)$  and multiple instances of  $msrp \in MSRP(G)$ . In a cp, nodes that support a csp or msrp may not be in consecutive order.

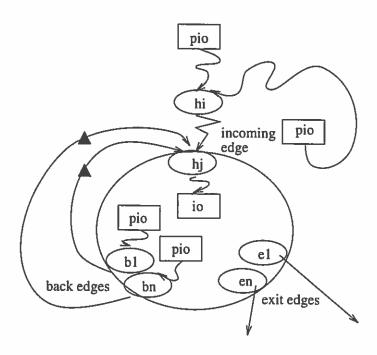

#### Example 3.1

D

0

9

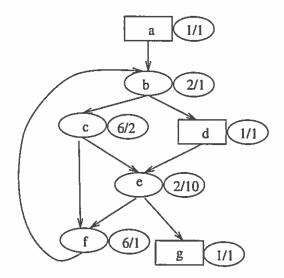

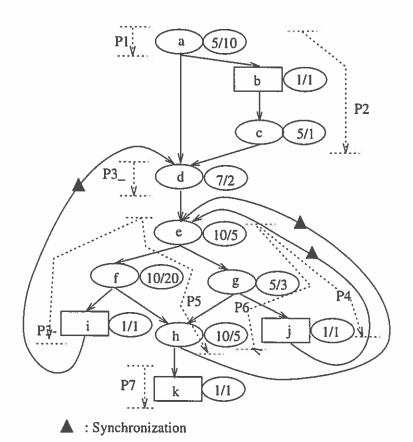

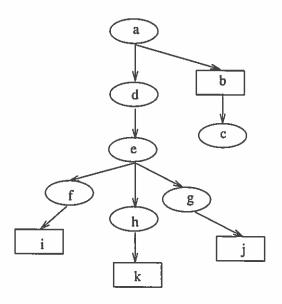

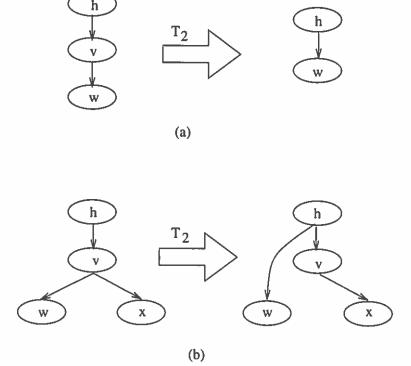

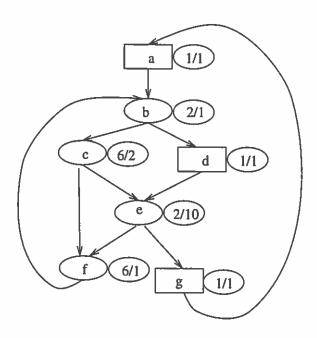

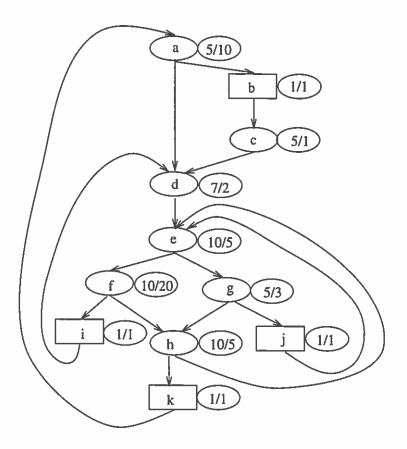

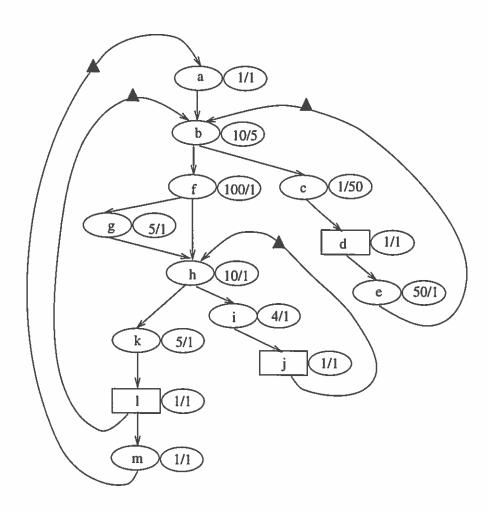

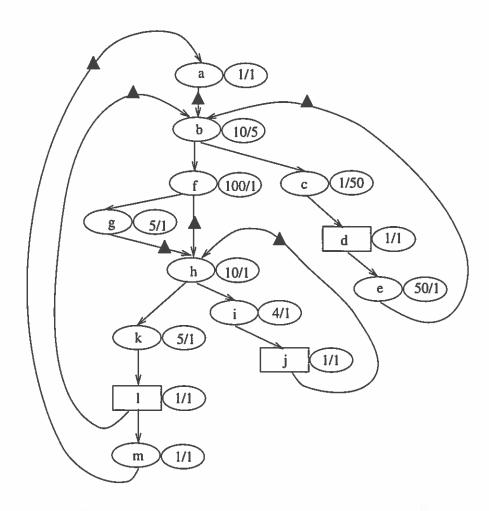

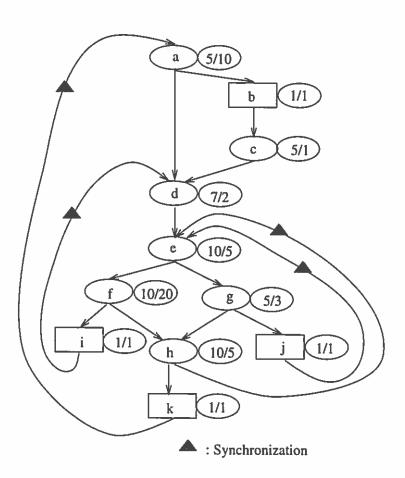

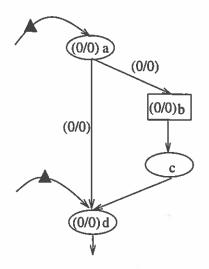

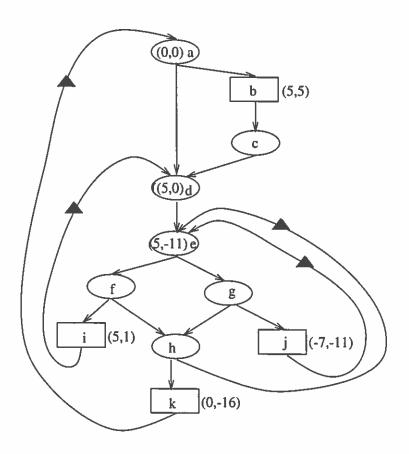

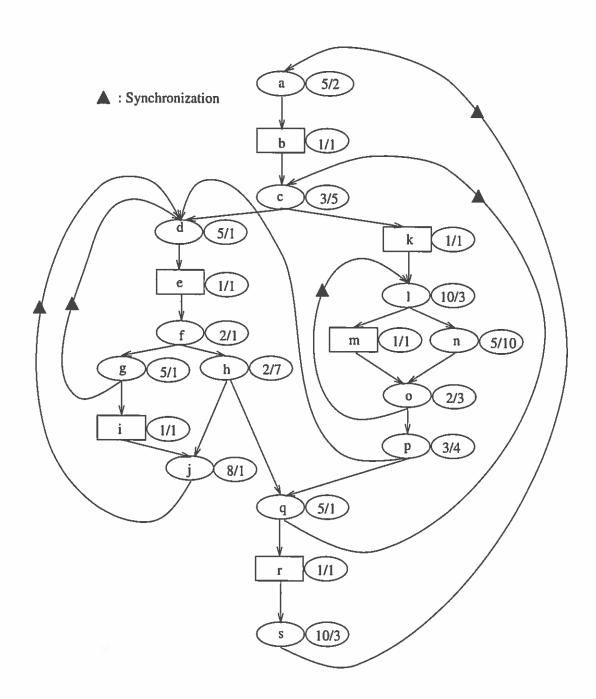

Figure 16 shows a control flow graph G. In this graph, the Entry node is labeled with a. Each node  $v \in V$  has another oval which is labeled with EST(v). The node g is the only exit node in G and the set IO(G) is  $\{a,d,g\}$ . There are many complete paths in G including;

$$\langle ia_1, ib_1, c_1, ie_1, ig_1 \rangle$$

,

$\langle ia_1, ib_1, c_1, if_1, ib_2, ic_2, ie_1, ig_1 \rangle$ ,

$\langle ia_1, ib_1, c_1, if_1, ib_2, ic_2, if_2, ib_3, ic_3, ie_1, ig_1 \rangle$ , etc...

Figure 16: An example of a control flow graph

The set CP(G), in this case, is *infinite*.

3

2

0

9

D

D

The set CSP(G) is  $\{\langle ia_1, ib_1, ic_1, ie_1, ig_1 \rangle, \langle ia_1, ib_1, id_1, ie_1, ig_1 \rangle\}$ .

The set SC(G) is  $\{\langle b, c, f, b \rangle, \langle b, c, e, f, b \rangle, \langle b, d, e, f, b \rangle\}$ . Thus, the set MSRP(G) is  $\{\langle b, c, f \rangle, \langle b, c, e, f \rangle, \langle b, d, e, f \rangle\}$ . Consider a complete path  $\langle ia_1, ib_1, ic_1, if_1, ib_2, ic_2, if_2, ib_3, ic_3, ie_1, ig_1 \rangle$  over the graph G. The first node  $ia_1$  is an instance of node a and is a part of a csp. The maximum simple repeatable path  $\langle b, c, f \rangle$  is repeated twice after  $ia_1$ . The rest of the complete simple path  $\langle ib_3, ic_3, ie_1, ig_1 \rangle$  finishes the cp.

Suppose a path  $p = \langle a_1, \ldots, a_{k-1}, a_k \rangle$  in G is given. The execution time required for a path p on a machine M is represented as ExecTime(p, M) as defined in Equation III.5.

$$ExecTime(p, M) = \sum_{i=1}^{k} (ExecTime(a_i, M))$$

(III.5)

For the given path p, EST(p) is  $((ExecTime(p, M_S), ExecTime(p, M_T))$ . The

execution time difference between source and target machine for the path p, STD(p), is defined as  $ExecTime(p, M_T) - ExecTime(p, M_S)$ . Consider two nodes  $x, y \in V$ . A  $\sigma_i \in \sigma(x, y)$  is a simple path from x to y. The function MaxEST(x, y) returns the  $EST(\sigma_p)$  such that

$$STD(\sigma_p) = \max_{\sigma_i \in \sigma(x,y)} (STD(\sigma_i(x,y))).$$

(III.6)

The function MinEST(x,y) returns the  $EST(\sigma_q)$  such that

$$STD(\sigma_q) = \min_{\sigma_i \in \sigma(x,y)} (STD(\sigma_i(x,y))). \tag{III.7}$$

## Example 3.2

)

)

)

9

0

D

Consider the control flow graph given in Figure 16, again. The set  $\sigma(b, f)$  is  $\{\langle b, c, f \rangle, \langle b, c, e, f \rangle, \langle b, d, e, f \rangle\}$ .

$$EST(\langle b, c, f \rangle) = (14,4), EST(\langle b, c, e, f \rangle) = (16,14), \text{ and } EST(\langle b, d, e, f \rangle) = (11,13).$$

$$STD(\langle b, c, f \rangle) = -10$$

,  $STD(\langle b, c, e, f \rangle) = -2$ , and  $STD(\langle b, d, e, f \rangle) = 2$ .

Thus, MaxEST(b, f) returns (11,13) and MinEST(b, f) returns (14,4).

# Spanning Trees and Edges

A spanning tree of  $G = \langle V_G, E_G, Entry_G, \rangle$  is a tree  $ST = \langle V_T, E_T, Root_T \rangle$  such that  $V_T = V_G$ ,  $E_T \subseteq E_G$  and  $Root_T = Entry_G$ . In general, ST of a G is not unique by definition. Two different spanning trees of G have two different subsets of edges from  $E_G$ . Given a spanning tree ST of a graph G, edges in G are partitioned into four groups.

- Tree edges are edges  $(v_1, v_2)$  in G that are also edges in ST.

- Forward edges are edges  $\langle v_1, v_2 \rangle$  in G that are not in ST but  $v_2$  is a descendant of  $v_1$  in ST.

- Retreating edges are edges  $\langle v_2, v_1 \rangle$  in G such that  $v_2 = v_1$  or  $v_1$  is an ancestor of  $v_2$  in ST.

- Cross edges are edges  $\langle v_1, v_2 \rangle$  in G such that  $v_2$  is neither an ancestor nor a descendant of  $v_1$  in ST.

# Example 3.3

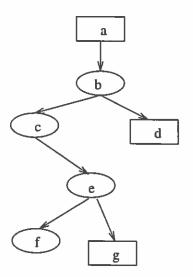

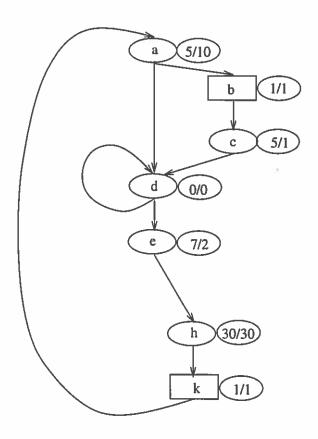

Figure 17: A spanning tree of the CFG shown in Figure 16

Figure 17 shows a spanning tree ST of the control flow graph G given in Figure 16. For the given ST,  $d \to e$  is a cross edge,  $c \to f$  is an advancing edge and  $f \to b$  is a back edge.

## Dominators and The Dominator Tree

A node x dominates node y, denoted by  $x \stackrel{DOM}{\longrightarrow} y$ , if every path from the Entry to y includes x. If  $x \stackrel{DOM}{\longrightarrow} y$ , then any path  $Entry \to y$  can be split into two parts:  $Entry \stackrel{*}{\longrightarrow} x$  and  $x \stackrel{*}{\longrightarrow} y$ . A node x strictly dominates y, denoted by  $x \stackrel{SDOM}{\longrightarrow} y$ , if  $x \neq y$  and  $x \stackrel{DOM}{\longrightarrow} y$ . A node x immediately dominates y, denoted by  $x \stackrel{IDOM}{\longrightarrow} y$ , if  $x \stackrel{SDOM}{\longrightarrow} y$  and there is no node z such that  $x \stackrel{DOM}{\longrightarrow} z$  and  $z \stackrel{DOM}{\longrightarrow} y$ . It is easy to see that each node has a unique immediate dominator if it has any [41]. The dominator tree (DOM tree in short) of a control flow graph  $G = \langle V_G, E_G, Entry_G \rangle$  is a tree  $DT = \langle V_T, E_T, Root_T \rangle$ , where  $V_T = V_G$ ,  $Root_T = Entry_G$  and  $E_T$  is the set of edges of the form  $x \stackrel{IDOM}{\longrightarrow} y$ . The DOM tree of a G is unique since every node has a unique immediate dominator [41]. A node u is a proper ancestor of v if  $u \stackrel{SDOM}{\longrightarrow} v$ . An algorithm to find dominator relationship can be found in [41, 54]. A more efficient algorithm is shown in [38]. A back edge in G is an edge  $\langle v_1, v_2 \rangle$  such that  $v_2$  is a predecessor of  $v_1$  in the DOM tree. A back edge also defines a loop which is different than that defined by a retreating edge in a spanning tree.

#### Example 3.4

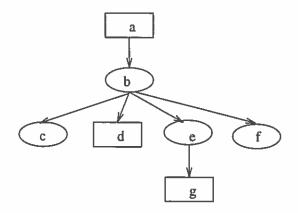

3

Figure 18 gives the DOM tree of the control flow graph shown in Figure 16. There is only one back edge in G, which is  $f \to b$ .

Figure 18: The dominator tree of the CFG shown in Figure 16

# Summary

In this chapter, we provided some mathematical notations. Using these notations, we defined our control flow graph. The definitions of spanning trees and the dominator tree of a control flow graph are also provided. A summary of notations is shown in Table 1.

| Definition    | Description                                                                                 |

|---------------|---------------------------------------------------------------------------------------------|

| $p^{\circ}$   | A sub-path $\langle a_0, \ldots, a_{k-1} \rangle$ of $p = \langle a_0, \ldots, a_k \rangle$ |

| $\rho(x,y)$   | Set of all paths from $x$ to $y$                                                            |

| $\sigma(x,y)$ | Set of all simple paths from $x$ to $y$                                                     |

| EST(v)        | $(ExecTime(v, M_S), ExecTime(v, M_T))$                                                      |

| STD(v)        | $ExecTime(v, M_T) - ExecTime(v, M_S)$                                                       |

| CP(G)         | Set of all complete paths in G                                                              |

| SC(G)         | Set of all simple cycles in G                                                               |

| MSRP(G)       | Set of all maximum simple repeatable paths in G                                             |

| MaxEST(x,y)   | $EST(\sigma_p(x,y))$ such that $STD(\sigma_p(x,y)) =$                                       |

|               | $\max_{\sigma_i(x,y)\in\sigma(x,y)}(STD(\sigma_i(x,y))).$                                   |

| MinEST(x,y)   | $EST(\sigma_q(x,y))$ such that $STD(\sigma_q(x,y)) =$                                       |

|               | $\min_{\sigma_i(x,y)\in\sigma(x,y)}(STD(\sigma_i(x,y))).$                                   |

Table 1: A summary of notations

#### CHAPTER IV

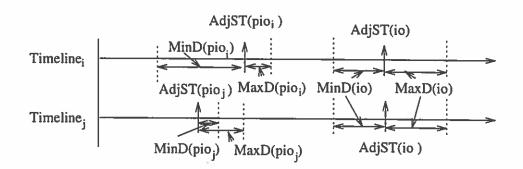

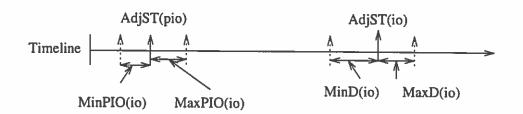

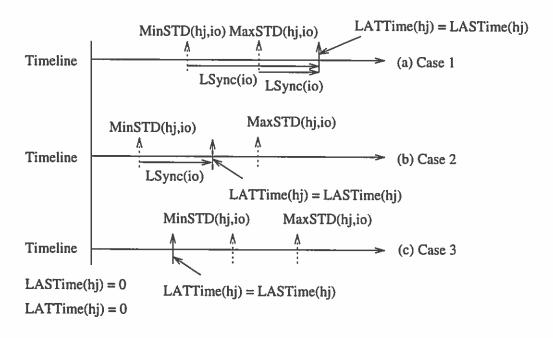

# TIMING EQUIVALENT TRANSLATION