# REASONING ABOUT LINEAR CIRCUITS IN SINUSOIDAL STEADY STATE

by

JUAN JOSE FLORES ROMERO

# A DISSERTATION

Presented to the Department of Computer

and Information Science

and the Graduate School of the University of Oregon

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

August 1997

"Reasoning About Linear Circuits in Sinusoidal Steady State," a dissertation prepared by Juan Jose Flores Romero in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science. This dissertation has been approved and accepted by:

Dr. Art Farley, Chair of the Examining Committee

20 August 1997

Date

Commitee in charge:

Accepted by

)

D

Dr. Art Farley, Chair

Dr. Andrzej Proskurowski

Dr. David Etherington

Dr. Davison Soper

Vice Provost and Dean of the Graduate School

An Abstract of the Dissertation of

Juan Jose Flores Romero

for the degree of

Doctor of Philosophy

in the Department of Computer and Information Science

to be taken

August 1997

Title: REASONING ABOUT LINEAR CIRCUITS IN SINUSOIDAL

STEADY STATE

Approved:

9

Dr. Art Farley

Most of the work on behavior prediction on the field of Qualitative Reasoning has focused on transient behavior and responses to perturbations; very little has been done about systems in steady state. A large class of systems, especially in the area of power systems, are designed for sinusoidal steady-state operation. Thus, an understanding of the steady state of electrical circuits is very important.

This dissertation presents a framework for reasoning about linear electrical circuits in sinusoidal steady state. The reasoning process relies on a constraint-based model of the circuit, derived from electro-magnetic theory and generated automatically from the structure of the circuit. In a linear circuit operating in steady state, all quantities are sinusoidals of the same frequency as the source. Since any sinusoidal can be expressed as the real part of a complex exponential, we use the complex form,

which simplifies computations; this complex form, characterized by magnitude and angle, is called a phasor. In order to capture magnitude and phase angle information in the model, all constraints operate on phasor variables.

Constraint propagation (CP) is the main inference mechanism. The CP module reasons with as much information and precision as the user provides, ranging from qualitative to quantitative. Intervals provide a general representation mechanism.

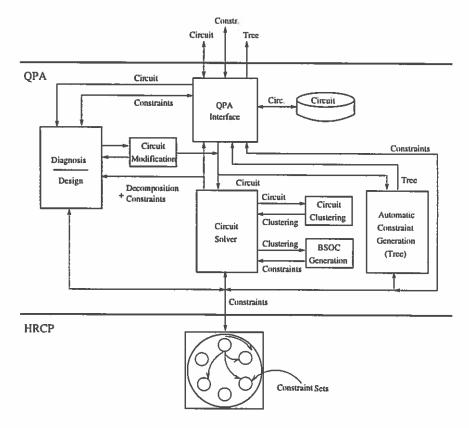

The framework presented in this dissertation has been implemented in a program called Qualitative Phasor Analysis (QPA), which performs the following reasoning tasks: analysis, parameter design, diagnosis, control design, and structure simplification. Circuits with multiple sources are solved using the superposition principle.

Power systems can be modeled as linear circuits and normally operate in steady state. A power system problem is translated to a circuit problem and solved by QPA; the results are then translated back to the original power system.

By extending the circuit ontology to include phasor information, this dissertation extends the range of problems that can be solved by qualitative reasoning.

#### CURRICULUM VITA

NAME OF THE AUTHOR: Juan Jose Flores Romero

PLACE OF BIRTH: Zamora, Michoacan, Mexico

DATE OF BIRTH: June 2nd, 1961

### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon Centro de Investigacion y Estudios Avanzados, IPN Univesidad Michoacana de San Nicolas de Hidalgo

#### **DEGREES AWARDED:**

Doctor of Philosophy in Computer and Information Science, 1997,

University of Oregon

Master of Science in Computer Science, 1986,

CIEA, IPN, Mexico,

B.Sc. in Electrical Engineering, 1983,

UMSNH, Morelia, Mexico.

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Art Farley, for his guidance and encouragement to achieve my goals. He spent so many hours of discussion about different issues in my research, proof-read every paper I submitted and this dissertation.

I would also like to thank Professors Andrzej Proskurowski, David Etherington, and Davison Soper for serving on my Ph.D. committee, reading the drafts, attending to meetings, and giving valuable comments. James Crawford had to leave the University of Oregon and therefore my committee, but he still kept reviewing and commenting my work. Elizabeth Bradley, from the University of Colorado, and Edmundo Barrera, from the University of Michoacan, took the time to read the drafts and held various discussions about the applicability of this work in Electrical Engineering. I appreciate the cheers and help from several Mexican graduate students in other Universities and my fellow grad students at the University of Oregon.

I want to thank my wife, Gina, for her love, understanding, and support. I thank my children: Gina, Mayra, and Pablo, for understanding so many times that I had to go back to work, instead of staying with them. Thanks to my father for always encouraging me to keep studying, and to my mother (que en paz descanse) for teaching me, by example, to live in God's way. Thanks to my brothers and sisters, who always helped me with all sorts of paper work back home. Thanks to my aunts

)

and my wife's family, who kept alive the desire to go back home.

This research was supported by a Conacyt-Fulbright scholarship, the Universidad Michoacana de San Nicolas de Hidalgo, and the University of Oregon

viii

DEDICATION

To my wife: Gina

)

)

# TABLE OF CONTENTS

| Chapter |                                                                                                                                                                                                                   | Page                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| I.      | INTRODUCTION                                                                                                                                                                                                      | . 1                                    |

|         | Background                                                                                                                                                                                                        | 6<br>16<br>17                          |

| II.     | ELECTRICAL CIRCUITS AND PHASORS                                                                                                                                                                                   | 21                                     |

|         | Phasors Power Factor and Phase Angle Complex Fans Related Work Chapter Conclusions                                                                                                                                | 25<br>28<br>69                         |

| III.    | HYBRID REPRESENTATION CONSTRAINT PROPAGATION                                                                                                                                                                      | 72                                     |

|         | Constraint Propagation Order of Magnitude Constraints Value Propagation First-Order Reasoning Mixed Propagation Propagation Across Algebraic Constraints User Interface Examples Related Work Chapter Conclusions | 77<br>82<br>85<br>86<br>88<br>89<br>91 |

| IV.     | REASONING ABOUT ELECTRICAL CIRCUITS                                                                                                                                                                               | 106                                    |

|         | Constraint-Based Circuit Model                                                                                                                                                                                    | 111<br>116                             |

|       | Diagnosis                   | 8 |

|-------|-----------------------------|---|

|       | Related Work                |   |

|       | Chapter Conclusions         | 3 |

| V.    | POWER SYSTEMS               | 2 |

|       | Power Systems Modeling      | 4 |

|       | Control Design              | 9 |

|       | Power System Analysis       | 3 |

|       | Topological Simplifications | 3 |

|       | Related Work                | 3 |

|       | Chapter Conclusions         | 5 |

| VI.   | CONCLUSION                  | 3 |

|       | Evaluation                  | 8 |

|       | Limitations and Future Work | 9 |

|       | Contributions               | 3 |

| APPE  | NDIX                        |   |

|       | EVALUATION EXAMPLES         | 3 |

|       | Circuit Examples            | _ |

| BIBLI | OGRAPHY                     | Q |

# LIST OF TABLES

| Table |                                              | Page  |

|-------|----------------------------------------------|-------|

| 1.    | Properties of Circuit Elements               | . 23  |

| 2.    | AND Table for OM Constraints                 | . 80  |

| 3.    | OR Table for OM Constraints                  | . 81  |

| 4.    | AND Table for Angle Order Constraints        | . 82  |

| 5.    | OR Table for Angle Order Constraints         | . 82  |

| 6.    | Constraints for Single Elements              | . 110 |

| 7.    | Constraints for Series and Parallel Clusters | . 113 |

| 8.    | Generation of the BSOC                       | 113   |

| 9.    | Selected Diagnosis Rules                     | . 124 |

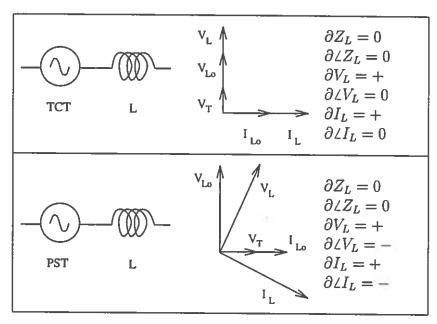

| 10.   | Design Rules for Control Transformers        | . 154 |

# LIST OF FIGURES

| Figure | ]                                                               | Page |

|--------|-----------------------------------------------------------------|------|

| 1.     | An Electrical Circuit, its Configuration, and Constraints       | 8    |

| 2.     | A Possible Phasor Diagram for Circuit in Figure 1               | 11   |

| 3.     | Tree Containing All Fully Constrained Models                    | 12   |

| 4.     | Structural Simplification by Order of Magnitude Reasoning       | 13   |

| 5.     | Faulty Observed Behavior                                        | 13   |

| 6.     | Diagnosed Fault                                                 | 14   |

| 7.     | QPA's Architecture                                              | 18   |

| 8.     | Graphical Representation of $Ce^{j\omega t}$                    | 22   |

| 9.     | An Electrical Circuit                                           | 24   |

| 10.    | A Possible Phasor Diagram for Circuit in Figure 9               | 24   |

| 11.    | Power in a Circuit with Unity Power Factor                      | 27   |

| 12.    | Power in a Circuit with Lagging Power Factor                    | 27   |

| 13.    | RL Circuit and Corresponding Phasor Diagram                     | 28   |

| 14.    | RLC Circuit and Corresponding Phasor Diagram                    | 28   |

| 15.    | Example of a Complex Fan                                        | 30   |

| 16.    | Notation                                                        | 32   |

| 17.    | Imprecision Added by Representation Changes                     | 33   |

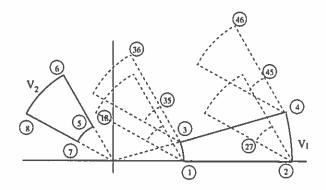

| 18.    | Phasor Addition, Case 1                                         | 37   |

| 19.    | Maximum and Minimum Angles in Phasor Addition                   | 38   |

| 20.    | Pseudo-Code for Case 1                                          | 42   |

| 21.    | Fan Addition in the Second Case.                                | 46   |

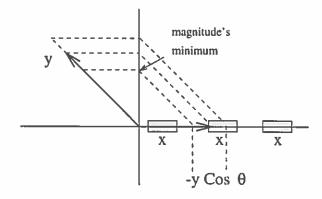

| 22.    | Minimum Magnitude of Phasor Addition; $x$ and $y$ Are Intervals | 46   |

|     |                                                               | xiii |

|-----|---------------------------------------------------------------|------|

| 23. | Pseudo-Code for Magnitude, Case 2                             | 47   |

| 24. | Case where Correction Is Needed, and Computation of $\phi$    | 48   |

| 25. | Pseudo-Code for Angle, Case 2                                 | 50   |

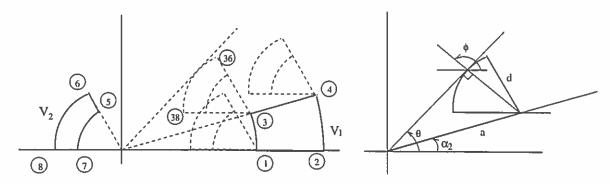

| 26. | Fan Addition, Case 3                                          | 51   |

| 27. | Pseudo-Code for Magnitude, Case 3                             | 52   |

| 28. | Fan Addition, Case 3                                          | 53   |

| 29. | Angle Correction for Case 3                                   | 53   |

| 30. | Pseudo-Code for Angle, Case 3                                 | 54   |

| 31. | Spurious Results in Complex Fan Addition                      | 57   |

| 32. | Complex Fan Addition Is Not Associative                       | 58   |

| 33. | Magnitude to Magnitude Influence                              | 62   |

| 34. | Pseudo-Code for Magnitude to Magnitude Influence              | 64   |

| 35. | Pseudo-Code for Magnitude to Angle Influence                  | 65   |

| 36. | Pseudo-Code for Angle to Magnitude Influence                  | 66   |

| 37. | Angle to Angle Influence                                      | 66   |

| 38. | Pseudo-Code for Angle to Angle Influence                      | 68   |

| 39. | Waltz's Algorithm                                             | 74   |

| 40. | Global Propagation Algorithm                                  | 76   |

| 41. | The Floyd-Warshall Algorithm                                  | 78   |

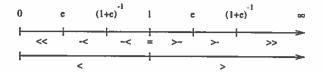

| 42. | Order of Magnitude Operators                                  | 78   |

| 43. | Value Propagation Algorithm                                   | 84   |

| 44. | Value Refinement from OM relations                            | 88   |

| 45. | An Electrical Circuit                                         | 91   |

| 46. | Example 1. Reducing the Number of Possible Behaviors          | 93   |

| 47. | Graphical Representation of Complex Fans for Example 1        | 95   |

| 48. | Example 2. Value Refinement by Order of Magnitude Constraints | 95   |

| 49. | Example 3. Detecting Inconsistencies                          | 96   |

| 50. | Example 4. Discovering OM Constraints from Value Constraints  | 97   |

|     |                                                         | λiv |

|-----|---------------------------------------------------------|-----|

| 51. | Example 5. First Order Reasoning                        | 98  |

| 52. | Explanation for Example 5                               | 99  |

| 53. | Iteration Loop in Value Propagation                     | 104 |

| 54. | Qualitative Phasor Analysis (QPA)                       | 108 |

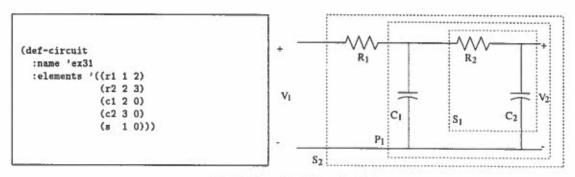

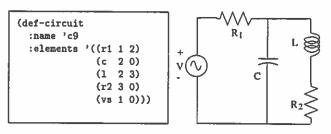

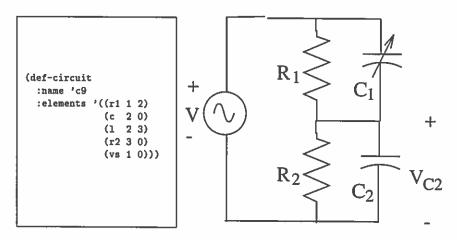

| 55. | Circuit Definition                                      | 111 |

| 56. | Simple Circuit                                          | 112 |

| 57. | Printout of a Circuit Model                             | 114 |

| 58. | Example of Parameter Design                             | 117 |

| 59. | Part of the Behavior Tree for Model of Figure 57        | 120 |

| 60. | Fault in an Element of a Series Cluster                 | 121 |

| 61. | A capacitor Being Short Circuited by a Resistor         | 123 |

| 62. | Pseudo-Code for Diagnosis                               | 127 |

| 63. | Observations for Circuit of Figure 57                   | 128 |

| 64. | Results of Diagnosis                                    | 129 |

| 65. | Pseudo-Code for Design-Step                             | 132 |

| 66. | Pseudo-Code for Incremental Design                      | 133 |

| 67. | Design Task #1 and Solution                             | 134 |

| 68. | Design Task #2 and Solution                             | 134 |

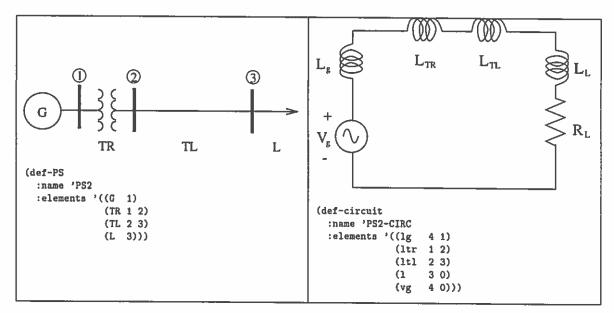

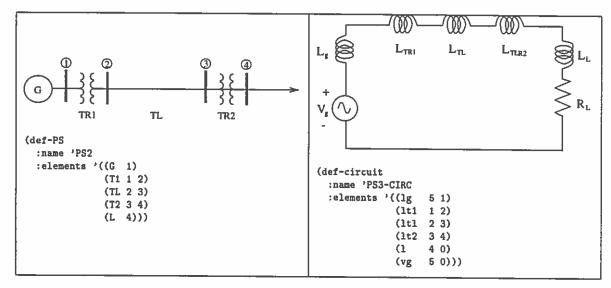

| 69. | Architecture of the Complete System                     | 145 |

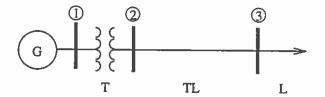

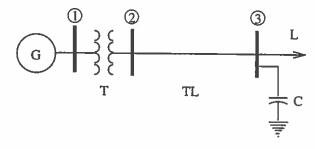

| 70. | One-Line Diagram of a Simple Power System               | 146 |

| 71. | Modeling of PS Elements                                 | 147 |

| 72. | Definition of the Power System of Figure 70             | 148 |

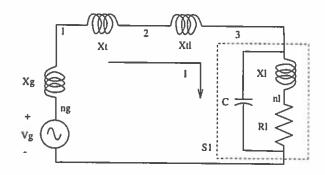

| 73. | Circuit Model of PS of Figure 70                        | 148 |

| 74. | Design Task Definition for Power Factor Correction      | 150 |

| 75. | Circuit Design Task Definition Produced by PSAD         | 150 |

| 76. | QPA Solutions to a Power Factor Correction Problem      | 151 |

| 77. | Circuit Solution to the Power Factor Correction Problem | 151 |

| 78. | Translation of QPA's Solution                           | 151 |

)

| 79.  | Power System Translation of Circuit in Figure 77                  | 151 |

|------|-------------------------------------------------------------------|-----|

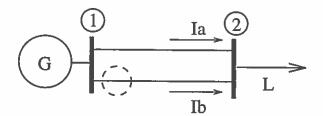

| 80.  | A Power Distribution Problem                                      | 152 |

| 81.  | Design Task Definition for a Power Distribution Problem           | 153 |

| 82.  | Translation of QPA's Solution                                     | 155 |

| 83.  | Rerouting Current by Inserting a Capacitor                        | 155 |

| 84.  | Rerouting Current by Inserting a Control Transformer              | 156 |

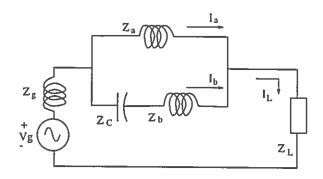

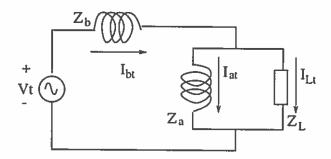

| 85.  | Superposition Algorithm                                           | 157 |

| 86.  | Component Due to $V_g$                                            | 157 |

| 87.  | Component Due to $V_T$                                            | 158 |

| 88.  | Printout of Component Due to $V_g$                                | 159 |

| 89.  | Printout of Component Due to $V_T$                                | 160 |

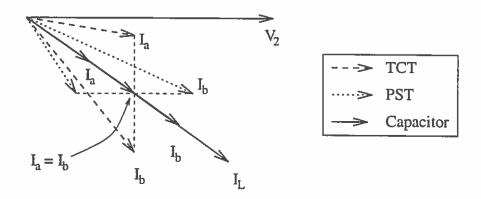

| 90.  | Different Solutions to the Power Distribution Problem             | 161 |

| 91.  | Verifying Design Using FOR                                        | 162 |

| 92.  | Reduction of Circuit of Figure 87 by Order of Magnitude Reasoning | 163 |

| 93.  | Circuit #2                                                        | 180 |

| 94.  | Results for Circuit #2                                            | 180 |

| 95.  | Circuit #3                                                        | 181 |

| 96.  | Results for Circuit #3                                            | 181 |

| 97.  | Circuit #4 and Design Task                                        | 182 |

| 98.  | Results for Circuit #4                                            | 182 |

| 99.  | Circuit #5                                                        | 183 |

| 100. | Results for Circuit #5                                            | 184 |

| 101. | Circuit #6, Definition, Input, and Output                         | 185 |

| 102. | Results for Circuit #6                                            | 186 |

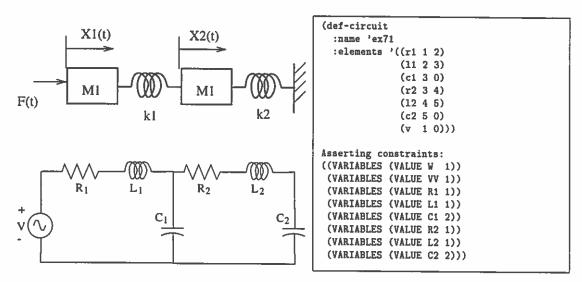

| 103. | Mechanical System and Equivalent Circuit                          | 187 |

| 104. | Results for Circuit #7                                            | 188 |

| 105. | Circuit #8                                                        | 189 |

| 106. | Results for Circuit #8                                            | 189 |

Þ

9

D

|      | AVI                                                 |

|------|-----------------------------------------------------|

| 107. | Circuit #9                                          |

| 108. | Circuit #10                                         |

| 109. | Results for Circuit #10                             |

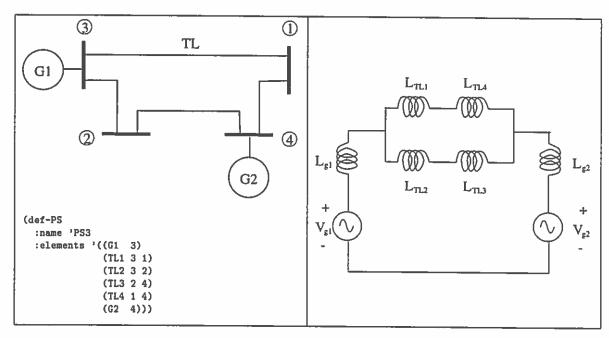

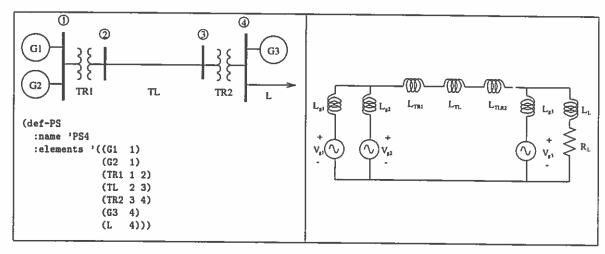

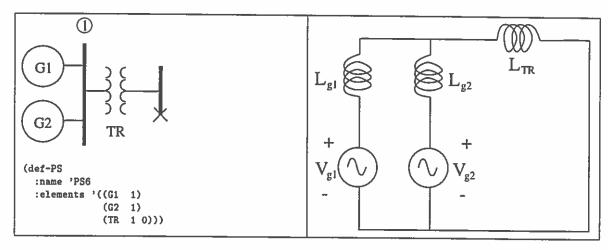

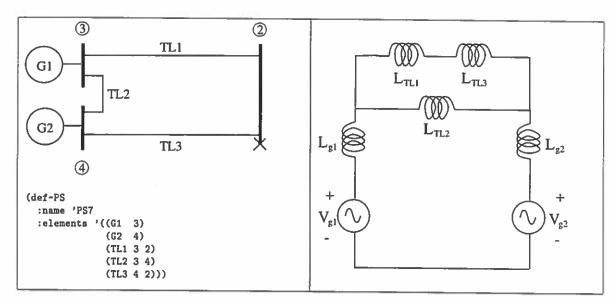

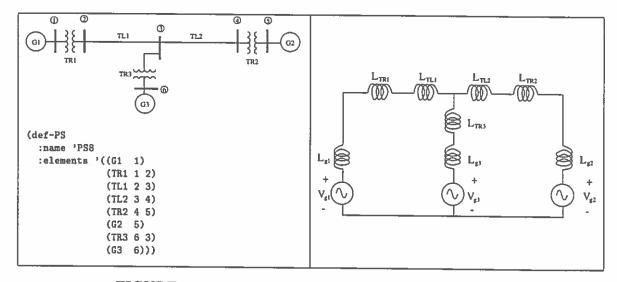

| 110. | Power System #2, and Its Circuit Model              |

| 111. | Results of Power System #2                          |

| 112. | Design Task on Power System #2                      |

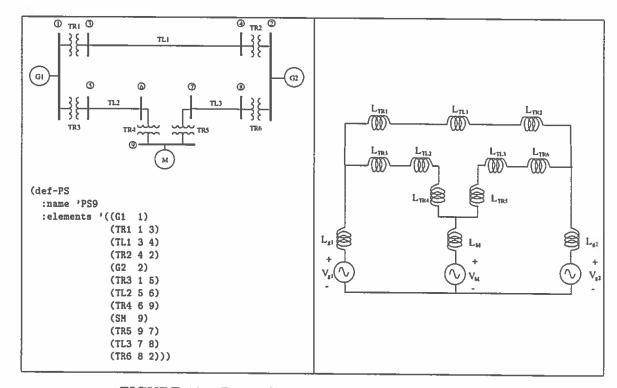

| 113. | Power System #3, and Its Circuit Model              |

| 114. | Results of Power System #3                          |

| 115. | Power System #4, and Its Circuit Model              |

| 116. | Results of Power System #4                          |

| 117. | Power System #5, and Its Circuit Model              |

| 118. | Results of Power System #5                          |

| 119. | Power System #6, and Its Circuit Model              |

| 120. | Results of Power System #6                          |

| 121. | Power System #7, and Its Circuit Model              |

| 122. | Analysis of Power System #7 under Normal Conditions |

| 123. | Short-Circuit Analysis of Power System #7           |

| 124. | Power System #8, and Its Circuit Model              |

| 125. | Results of Power System #8                          |

| 126. | Short-Circuit Values for Sources of Power System #8 |

| 127. | Power System #9, and Its Circuit Model              |

| 128. | Results of Power System #9                          |

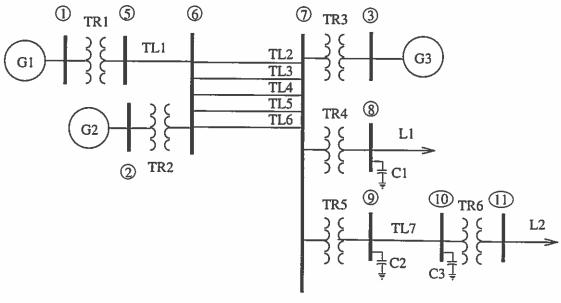

| 129. | Power System #10                                    |

)

)

D

)

)

### CHAPTER I

# INTRODUCTION

One of the main objectives of qualitative reasoning is to derive the behavior of a system from a description of its components and their interrelationships [12, 17, 28, 52]. Prediction of behavior has been achieved by traditional physics at different levels and in different areas. In particular, in the area of circuit analysis there are a number of numerical methods to analyze circuits of different kinds and under different conditions [27, 49]. Those methods take as input a circuit topology and exact values for the parameters, perform some computation (mainly based on linear algebra or iterative methods to solve non-linear or differential equations), and return exact values for the variables representing the unknown quantities. In this process, causality and explanation are discarded; the only goals are precision and efficiency.

This dissertation presents a framework for performing qualitative analysis of linear circuits in sinusoidal steady state. We call this approach Qualitative Phasor Analysis (QPA). QPA is based on three main ideas regarding modeling and qualitative physics. First, it develops a constraint-based model of the circuit, where the constraints are derived from general knowledge of circuit theory and the circuit's topology. A constraint-based model can be generated automatically, this feature

)

)

)

Ъ

9

makes the system able to analyze any series/parallel decomposable circuit. Another feature provided by constraint-based reasoning is that the order of computation is not fixed, i.e., any variable can be used as input or output. This property allows us to perform parameter design, based on circuit analysis.

Second, it is able to propagate constraints of different kinds (e.g., algebraic, value, order of magnitude, etc.). Constraints of different types are kept in different sets, and the rules to propagate those constraints are different. Value propagation is extended to deal with interval values. Mixed constraint propagation allows us to derive order of magnitude relations from values and to refine values from order of magnitude relations.

Third, phasor analysis can be done with as much information about circuit parameters and quantities as provided by the user, ranging from qualitative (sign) to numerical (real) values. This characteristic is implemented by uniformly representing all values as intervals. Signs can be represented as intervals with open infinite extremes, and reals can be represented as point intervals. Value propagation can also handle phasors with interval magnitudes and phase angles.

b

9

)

Based on the results of circuit analysis, several reasoning tasks can be performed. The reasoning tasks we have in mind are qualitative/quantitative circuit analysis, parameter design based on first-order reasoning, circuit analysis, circuit simplification by order of magnitude reasoning, the derivation of all possible qualitatively different phasor diagrams (corresponding to qualitatively different states of the circuit), fault

diagnosis, and control design.

1

This chapter explains the basic problems this dissertation addresses, states the thesis, and identifies some of the important research issues. It then discusses implementation and evaluation.

### Background

The foundational contributions to the field of qualitative reasoning are those by DeKleer [12], Kuipers [28], and Forbus [17]. DeKleer proposed an approach based upon confluences, which captures a sense of causality and reasons about change. Forbus developed qualitative process theory, QPT, a mechanism that allows us to reason about physical objects and their interaction modeled as processes. Kuipers developed QSIM, a system that predicts all possible transient behaviors of physical systems, for systems that can be described by sets of ordinary differential equations.

Several systems have been built to reason about and derive the qualitative behavior of electrical circuits. Most of them focus on either digital circuits or DC analog circuits (see for example, DeKleer [10], Hamscher [22], Williams [52]). None has addressed the analysis of linear circuits in sinusoidal steady state. QSIM can simulate the behavior of linear circuits, but since it is based on differential equations, its scope is limited to transient state analysis. Also, QSIM's formalism is not able to represent a sinusoidal source in terms of the given types of constraints. The response description given by QSIM is at a microscopic level with respect to time, describing

the possibilities at each distinguished time point. It is a well known fact that all variables in a circuit in steady state will be steady sinusoidals; there is no point in trying to find out if a peak (defined by a landmark) will be greater, equal or less than the next one. That microscopic view prevents us from getting the big picture of what is happening in the circuit and generates unnecessary ambiguity.

DeKleer's confluences allows us to reason about change, but only in terms of magnitudes of scalar quantities. Since the main tool used to solve steady state problems is phasors (i.e., a particular kind of vector), we need a way to represent angular information and the interaction between the magnitudes of different quantities and their phase angles.

Trying to describe the behavior of an electrical circuit in terms of processes is awkward. Similar to Kuiper's approach, the kind of description that QPT yields would be at the microscopic level. This kind of representation would involve charges, and how the process of moving charges (i.e., electrical current) would result from the application of an electrical field. We need something at a higher level of abstraction, where the existence of a stable oscillation of alternating currents is already known and not the goal to be established. Thus, QPT is not suited to solving the problems addressed in this dissertation.

Few researchers have worked on qualitative analysis of power systems. Struss [42, 43] developed a system to diagnose faults in power transmission networks. He follows a relational approach to the modeling of power system components; consistency-based

)

9

diagnosis is used to find faults in the system, based on the reading of "distance protection relays". The analysis he performs is not based on circuit theory; it focuses on what relays have tripped and if the observations are consistent with the models of those relays.

0

)

9

1

9

0

QPA is able to simplify a circuit, based on order of magnitude relations. If QPA determines (based on order of magnitude relations given by the user) that a current (voltage) is negligible, it can discard that part of the circuit, replacing it by an open (short) circuit. We call this feature structural exaggeration. A similar kind of transformation is presented by Liu's ARC [32], which eliminates parts of a circuit if the operating region of an element indicates it behaves like an open circuit. The system is then recasted according to its new topological configuration. Also related to model changes, Struss presents a diagnosis system that works with models at different levels of abstraction. The simplifications presented in his work deal with the internal model of each device, refining it to yield more accurate results when necessary. The overall structural description of the system does not change with the use of different models. QPA's structural exaggeration, by contrast, can simplify the overall structure of the circuit, supported on the circuit's operating conditions.

Bibliographic surveys are given at the end of each chapter to contrast the contributions presented in this work with previous results in related fields.

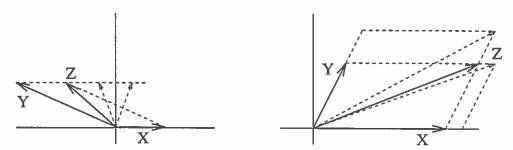

# Qualitative Phasor Analysis

The electrical engineering community has been very successful in predicting behavior of linear circuits in steady state. The main tool they use in circuit analysis is the phasor. Phasors [27, chapter 5] are a mathematical transformation that maps sinusoids from the time domain to the frequency domain, allowing us to replace complicated simultaneous differential equations by simultaneous algebraic equations in the complex domain. In addition to their power to solve linear circuits, phasors can be expressed in an intuitive graphical form; the so called *phasor diagrams*. These diagrams allow electrical engineers to have a better understanding of what happens inside a circuit and can be used to produce causal explanations of physical phenomena. This characteristic of phasors is the one that we want to capture in a suitable representation, allowing us to reason about linear circuits in the same way as in explanations found in books.

1

A mathematical model of a circuit includes a set of algebraic relations that constrain its behavior. For instance, we know that current and voltage are in phase in a resistor or that the currents of two parallel branches add to the total current of the combination. We can capture this information and represent it as a set of qualitative constraints, which will enable us to reason about a circuit's behavior.

To determine the set of algebraic constraints, we will represent the circuit as a recursive structure of series/parallel clusters [32]. We can recursively traverse that clustering structure, generating constraints for each cluster and single element we en-

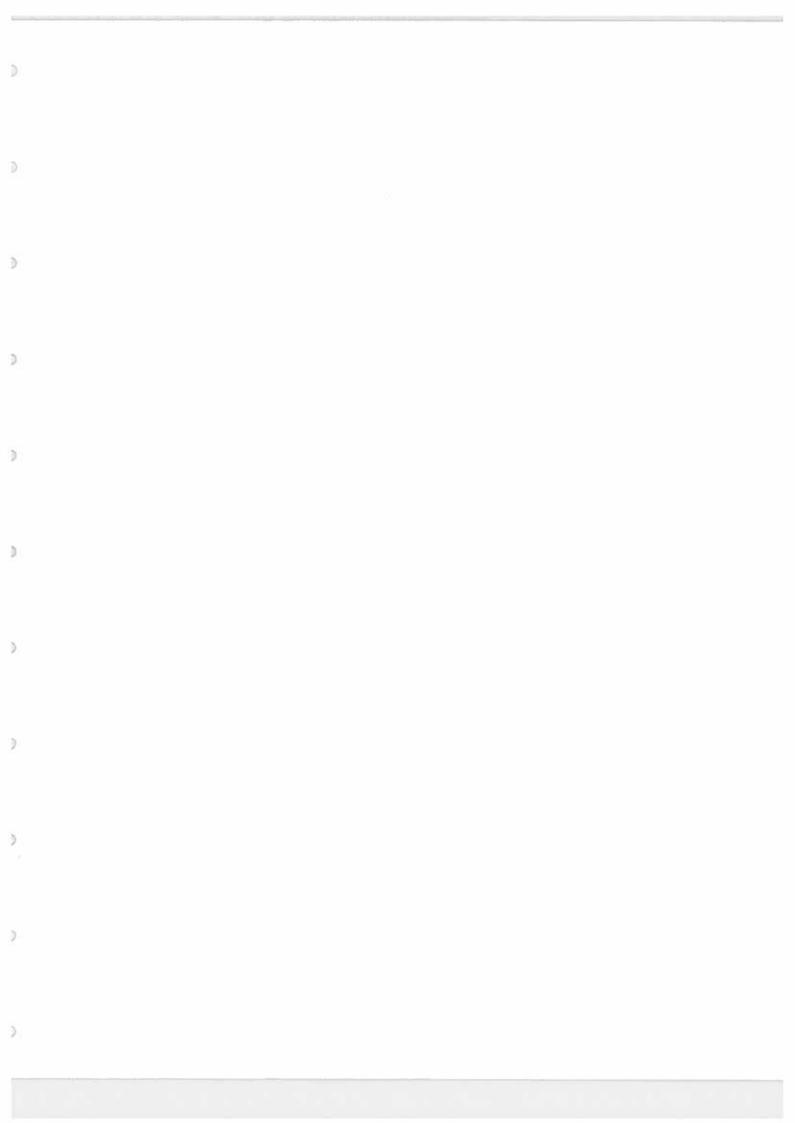

counter. The resultant set of constraints can be partitioned into constraints of several types: Algebraic (e.g.,  $V_{R2} = Z_{R2} * I_{R2}$ ), Ordering (e.g.,  $I_{R1} > I_C$ ), Order of Magnitude (e.g.,  $I_{R1} \gg I_C$ ), Phase Angle (e.g.,  $V_{R2}$  InPhase  $I_{R2}$ ), and Confluences<sup>1</sup> (e.g.,  $\partial V_R - \partial Z_R - \partial I_R = 0$ ). These constraints are derived from basic electro-magnetic and circuit theories. Confluences, which represent the dynamic properties of the circuit, can be derived from algebraic constraints.

)

)

9

9

D

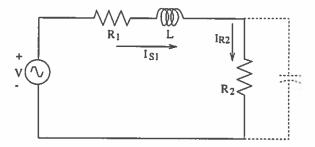

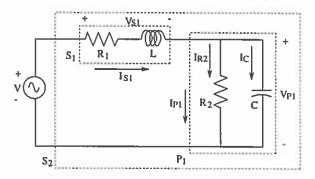

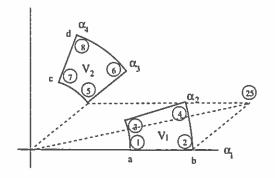

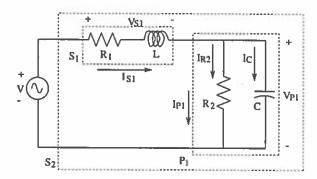

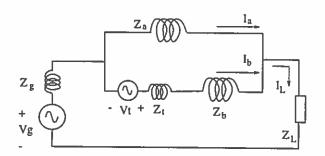

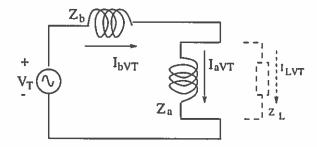

Let us consider the circuit of Figure 1, which shows a circuit and its topological configuration in terms of series/parallel clusters. Figure 1 also shows examples of the type of constraints that can be generated for each component and cluster of the circuit.

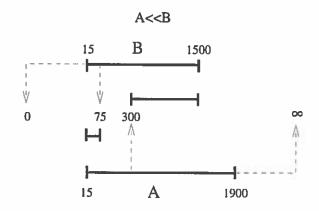

The set of all constraints that can be derived from the circuit topology, based solely on electrical circuit theory, are what we call the Basic Set of Constraints (BSOC). Once the BSOC has been generated, propagation is used to maintain the transitive closure of the constraints and their implications. For instance, from the constraints  $I_{S1} = I_{R1}$  and  $I_{S1} = I_{L}$  we can derive that  $I_{R1} = I_{L}$ . If the user has any further information about features of the circuit, he or she can express them in the form of additional constraints. For instance, the user can say that  $Z_{R2} < Z_{C}$ ; propagation will return to the user the implied constraints, informing him or her that  $I_{C} < I_{R2}$ .

<sup>&</sup>lt;sup>1</sup>A confluence has the usual meaning and use [12]. For instance, for Ohm's law in a resistor  $V_R = Z_R I_R$ , we have the qualitative counterpart  $\partial V_R - \partial Z_R - \partial I_R = 0$ . This confluence indicates (among other things) that if  $Z_R$  decreases and  $V_R$  does not change,  $I_R$  increases.

FIGURE 1. An Electrical Circuit, its Configuration, and Constraints

)

)

9

The values that variables can take on range from qualitative signs to reals. In between those extremes, one can specify values by intervals, with as much precision as needed. Of course, the more precise the provided information is, the more precise the results will be. While analyzing a circuit, one can specify values for some of the variables, and propagation will compute the resulting values for the rest of them. For instance, for the circuit of Figure 1, one can specify W = 60,  $V_S = 100$ , C = [0.0024, 0.0026],  $R_2 = [14.9, 25.1]$ , etc. QPA will solve for the rest, e.g.,  $V_{S2} = 100$ ,  $I_C = [1.4857, 1.9539] \angle [301.37, 307.32]$ ,  $I_{R2} = [0.3867, 0.5365] \angle [211.37, 217.32]$ , etc. (all these quantities are phasors; the first interval represents the magnitude and

the second one the angle -see Chapter II)

0

3

0

)

If the user then asks if  $I_C < I_{R2}$  can be true, the system can respond with the following answer:

Contradiction detected.  $I_C < I_{R2}$  contradicts the constraints

$I_C = [1.4857, 1.9539] \angle [301.37, 307.32],$  and

$I_{R2} = [0.3867, 0.5365] \angle [211.37, 217.32].$

The set of all quantities in a circuit represents the set of possible behaviors the circuit can exhibit. When the quantities are allowed to range in intervals (magnitudes and angles of phasors as well), each possible combination of assignments of values to variables represent a behavior. Thus, the set of constraints represents a set of acceptable behaviors of the circuit. Reducing the interval domains of the variables (by asserting new constraints) reduces the number of possible behaviors. If all quantities take on real number values, the behavior of the circuit is unique. By refining the interval values of quantities until all of them become point intervals (i.e., real numbers), the set of predicted behaviors reduces to one and coincides with the behavior predicted by a conventional circuit solver.

Mixed propagation can also be performed. That is, from value constraints, order of magnitude relations can be discovered. The converse is also possible, given order of magnitude constraints, the values of the involved variables can be refined to make sure the given relation does not result in an inconsistency.

Causal reasoning, also known as First Order Reasoning<sup>2</sup> (FOR) is important if we want to be able to explain a circuit's behavior. Confluences capture the interaction among different variables in the circuit, and how changes in one variable can produce changes in other variables. For example, if the user asks "what happens if C increases?" (expressed as the constraint  $\partial C = +$ ), the system replies<sup>3</sup>

)

)

9

"If C increases,  $Z_C$  decreases, which causes  $Z_{P1}$  and  $Z_{S2}$  to decrease. This makes  $I_{S2}$ ,  $I_{S1}$ , and  $I_{P1}$  increase. If  $I_{S1}$  increases,  $V_{S1}$  increases, and since  $V_{S2}$  is constant, this causes  $V_{P1}$ ,  $V_{R2}$ , and  $V_C$  to decrease. If  $V_{R2}$  decreases,  $I_{R2}$  decreases, causing IC to increase. Since  $I_{R2}$  decreases and IC increases, the phase angle  $L(I_{R2}, I_{P1})$  will increase and the angle  $L(I_{P1}, I_{C2})$  will decrease."

Confluences are equations, whose variables are rates of change, taking on values from the domain of qualitative signs (i.e., -,0,+). Our value propagation mechanism propagates changes in variable values through a network of algebraic equations, where the values variables take on can be reals, intervals, or qualitative signs, all of them uniformly represented as intervals. Therefore, first order reasoning is a particular case of value propagation with interval values.

The BSOC is a Partially Constrained Model (PCM) of the circuit, which will

<sup>&</sup>lt;sup>2</sup>The term First Order Reasoning comes from the fact that we are dealing with the first order derivatives of quantitites. Similarly, value propagation is called Zeroth Order Reasoning

<sup>&</sup>lt;sup>3</sup>No natural language interface has been built or used. In the rest of this document, we paraphrase all questions and answers. Example 5 (figures 51 and 52, on pages 98 and 99) show a transcript of the system interaction and the results of explanation.

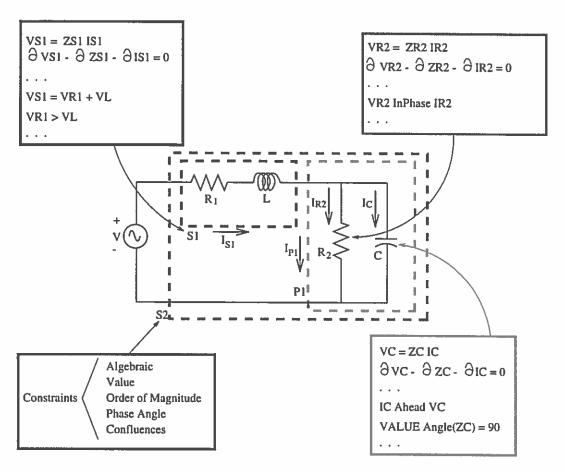

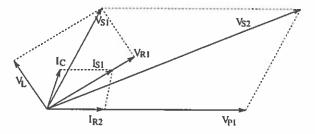

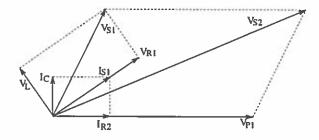

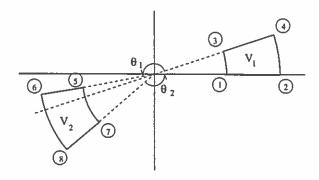

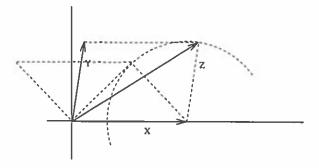

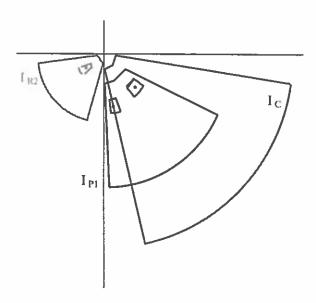

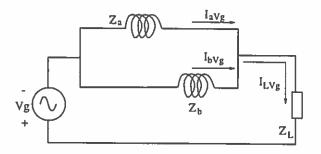

allow us to perform the reasoning task we have in mind. A PCM corresponds to a set of circuit behaviors; the more constrained the circuit model is, the smaller the set of possible behaviors is. For instance, we can tell that the phase angle of  $S_1$  lies in the interval (0, 90), represented by the constraint  $\angle Z_{S1} = (+\angle[0 \ 90])$ . After asserting that  $I_C < I_{R2}$ , we know that  $\angle Z_{S1} = (+\angle[0 \ 45])$ . The set of constraints represents the set of possible behaviors a circuit can exhibit. Figure 2 shows one phasor diagram (behavior of the circuit), of the many possible for the circuit model of Figure 1. That phasor diagram was drawn under the added assumptions  $I_{R2} > I_C$ ,  $V_L > V_{R1}$ , and  $V_{S1} > V_{P1}$ .

FIGURE 2. A Possible Phasor Diagram for Circuit in Figure 1

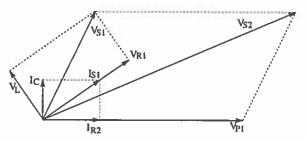

After the user has provided a number of constraints, it is more likely that further constraints are rejected as inconsistent with the partial solution. At that point the user can say "OK, give me all possible, fully constrained models ...". Even if the user was able to provide all constraints available, one of the goals of the system is to produce all possible, fully constrained models of the circuit (i.e., all possible qualitative behaviors of the circuit under the actual set of constraints). Traversing the circuit's structure, QPA determines what variables are interrelated and produces all relevant constraints. If no constraint involving those variables is found in the

PCM, all possible constraints that include those variables are produced. Nodes with constraints that produce inconsistencies are pruned and not included in the tree. The result is a tree like the one shown in Figure 3<sup>4</sup> where the leaves correspond to sets of constraints representing fully constrained models of the circuit.

)

FIGURE 3. Tree Containing All Fully Constrained Models

QPA also handles order of magnitude constraints. Order of magnitude constraints can be used to simplify a circuit, when appropriate. Returning to the circuit shown in Figure 1, if the user tells the system that  $Z_C \gg Z_{R2}$ , the system responds that  $I_C \ll I_{R2}$ . This is interpreted by QPA in the appropriate way; the current through that branch is negligible, therefore, the whole branch can be omitted (open circuited). The resulting circuit is shown in Figure 4. In general, if after running propagation it is determined that the current through a branch in a parallel cluster is negligible, the element can be substituted by an open circuit. A similar simplification can be done for the case where the voltage through an element in a series cluster is

<sup>&</sup>lt;sup>4</sup>The tree in Figure 3 was formed using only operators <, =, and >. The system is general enough to accept any other set (e.g., the set of order of magnitude operators)

D

D

0

D

)

0

FIGURE 4. Structural Simplification by Order of Magnitude Reasoning

negligible; in that case, the element is substituted by a short circuit. Opening an element or cluster is equivalent to removing it from the circuit; short-circuiting is equivalent to removing that element or cluster and to collapsing its end-points into one. After these structural modifications, a new model of the circuit is rebuilt, and propagation on the given constraints must be recomputed.

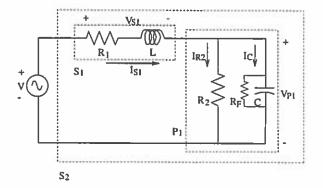

Now consider the process of measurement interpretation or diagnosis, based on a QPA representation. Suppose that the observed state of the circuit is shown in Figure 5. The observed state, measured by physical instruments, can be easily

FIGURE 5. Faulty Observed Behavior

translated to a set of constraints. For instance, we observe that  $V_{S_1} = (95 \angle 3.5)$ ,  $V_C = (7.5 \angle 309)$ ,  $I_C = (3.8 \angle 323)$ , etc. Those constraints can be verified against the circuit model by following the circuit's topology in a top down manner. If a contradiction is found, the circuit is considered faulty and a set of possible faults are

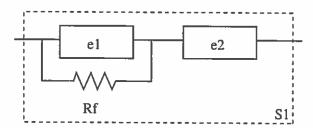

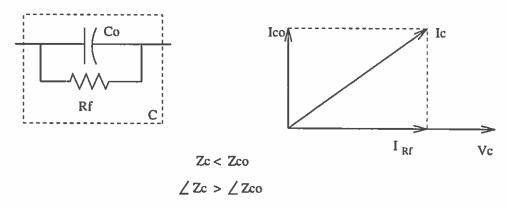

suggested to the user. In this example we start by checking the constraints for cluster  $S_2$ ; while no contradictions were found at this level, we need to continue verifying the rest of the circuit, traversing its structure. We continue checking  $S_1$ ,  $P_1$ , and inside them, until we find that the phase angle of the current and voltage in the capacitor does not correspond to the model of that element. By the characteristics of the observation, we conclude that "the capacitor is leaking". In other words, it is shorted by a small resistance  $R_F$  (see Figure 6).

FIGURE 6. Diagnosed Fault

Order of magnitude reasoning, as proposed above, should allow the system, for example, to prove that a short-circuit with resistance, for which the fault resistance is very small (negligible), is equivalent to a circuit with a perfect short (i.e., with zero resistance). First, QPA infers  $I_C \ll I_{Rf}$ , which leads it to eliminate C. Then, it infers that  $V_{S1} \gg V_{P1}$ , which eliminates the whole cluster  $P_1$ . The final circuit is equivalent to the situation where there is an ideal short circuit in C.

)

)

Another problem we are addressing is Control Design. Control design answers questions similar to those in FOR (e.g., "How can I get the phase angle of cluster

$S_1$  to decrease?"). In some cases, if one or more parameters are variable, we can solve those questions by FOR alone. In some other cases, even if there are some variable parameters, there is no setting of those parameters that would make us achieve the goal(s). Furthermore, we might want to further constrain the solution to those problems (e.g., "How can I get the phase angle of cluster  $S_1$  to decrease, without changing  $V_{S_1}$ ?"). The approach we take is similar to means-ends analysis, where the initial situation is represented by the working model, and the goal situation by the goals and the design constraints. The operators are circuit modifications, that, when applied to the circuit, change its conditions. We design by inserting one modification at a time until all goals are satisfied and no constraint is violated.

D

)

)

D

Given these basic reasoning capabilities, one domain of application suitable for using QPA is Power Systems Analysis and Control. Power Systems are modeled by linear circuits [20, 19], with lumped, constant parameters, and are normally operated under sinusoidal steady state; those are exactly the kinds of circuits QPA reasons about. By using QPA, we can solve basic problems in the area of power system analysis. Some of those problems are power factor correction and power distribution. Industrial loads are typically composed of resistive and inductive elements, therefore having a lagging power factor. Connecting a capacitor bank in parallel with the load corrects its power factor. The power distribution problem arises in situations where the transmitted power increases, and one of the lines is not capable of holding the resulting amount of current. Power redistribution can be accomplished by installing

capacitors, or tap changing or phase shifting transformers in series with the transmission lines. QPA can reason from first principles to determine such solutions to power system problems.

3

D

### Thesis Statement and Research Issues

Research in qualitative circuit analysis (and even in behavior prediction in the field of qualitative reasoning) to date focuses on analysis of transient response. Previous work cannot be applied to reasoning about the response of such systems in steady state, because it focuses only on magnitudes of scalar quantities. Quantities in electrical circuits in steady state are represented as a special kind of vector, called phasors, where not only magnitudes, but also angles play an important role. To develop a computational framework capable of reasoning about such systems, this dissertation investigates the following thesis statement:

By extending the circuit ontology to include phasors and by using a constraint-based model of the circuit, we can extend the range of problems that can be solved by qualitative reasoning about complex systems.

To explore the development of such a computational framework, this dissertation addresses the following research issues.

Can the circuit ontology be extended to adequately represent phasor and phase angle information? • Can we use this representation to reason effectively about electrical circuits in steady state?

0

)

- What modifications to normal constraint propagation procedures are needed to deal with constraints of different kinds?

- How can the structure of a circuit be simplified, based on order of magnitude information derived from constraint propagation?

- Can we, by using a single representation, reason about the circuit at several degrees of abstraction, from qualitative to quantitative information?

- Can we design solutions for the problems of operation, diagnosis, and control

of power transmission systems, based on first principles of phasor analysis?

# Implementation and Evaluation

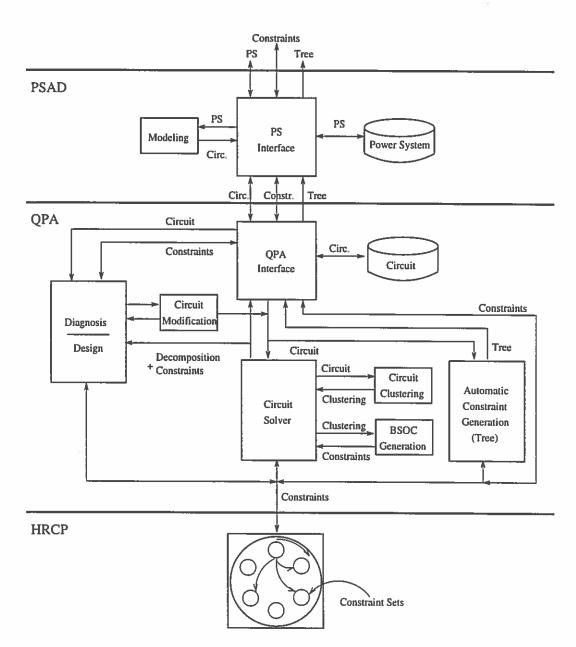

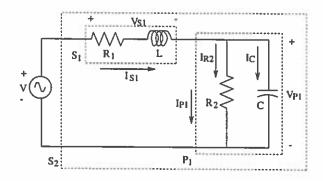

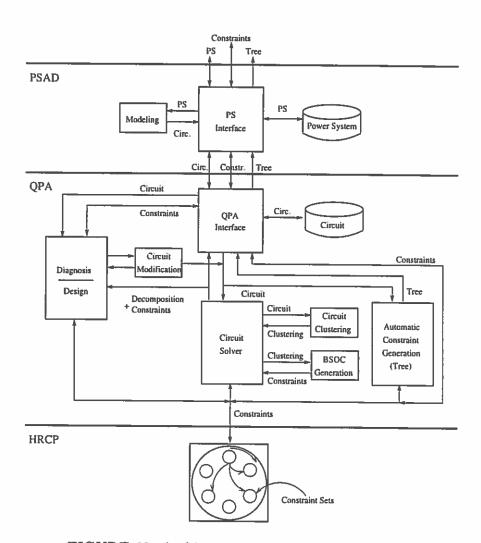

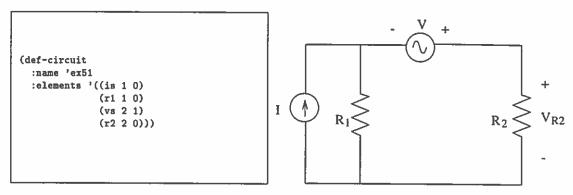

The system has been implemented in Allegro Common Lisp for Sun Workstations. The system consists of three layers: Power System Analysis and Design (PSAD), Qualitative Phasor Analysis (QPA), and Hybrid Representation Constraint Propagation (HRCP). Figure 7 shows the proposed architecture of the system.

The interface for this project is a textual symbolic description of the input and output. The input is the topological configuration of the circuit or power system, which includes the definition of each of the elements and their interconnections. The input constraints are of the form mentioned in the preceding section. The output

3

)

0

3

Ď.

)

0

)

0

FIGURE 7. QPA's Architecture

of the system is a set of constraints, representing the partially constrained model of the circuit or power system. Value propagation, which includes first-order reasoning, forms a trace of the propagation process, which can be used to provide explanations like the ones mentioned above. In the case of diagnosis or control design, the new topological configuration of the circuit will be returned to the user.

The performance of the system was evaluated by comparing its results with examples found in textbooks, and with the results of the application of standard techniques used in circuit analysis. The usability and applicability of the system has been evaluated by experts in the area of Electrical Engineering, Artificial Intelligence, and Power Systems. For that purpose, we contacted a power engineer from Bonneville Power Administration, a faculty member from the University of Colorado, and a faculty member from the School of Electrical Engineering of the University of Michoacán.

D

3

0

)

### Dissertation Organization

Chapter II presents an overview of the basic concepts in electrical engineering, phasors and our proposed representation, called *complex fans*. Chapter III focuses on the proposed modifications to constraint propagation to deal with constraints of different kinds, including order of magnitude relations, and confluences. Chapter IV addresses the reasoning tasks QPA (Qualitative Phasor Analysis) performs about linear circuits in sinusoidal steady state. Chapter V gives an introduction to QPA's

main field of application, Power Systems, as well as examples of how the techniques developed for QPA can be used to solve problems of importance to the field. Chapter VI concludes the dissertation by discussing its contributions and limitations, as well as directions for future research. Each chapter includes a brief survey of related research, as appropriate.

#### CHAPTER II

## ELECTRICAL CIRCUITS AND PHASORS

5

D

D

D

0

This chapter covers basic concepts in electric circuits, focusing on the solution of circuits under sinusoidal steady state. The main representational tool used in electrical engineering to perform circuit analysis in sinusoidal steady state is the phasor. We review the concept of phasor and its use in the solution of linear circuits, and present a proposed representation, called complex fans, that allows us to handle phasor information under uncertain conditions.

#### **Phasors**

The behavior of a linear circuit can be characterized by an ordinary differential equation (ODE) [4, 27, 49, 39]. If the forcing function is a sinusoid, the analytical solution of the equation, in the steady state regime, indicates that the response will also be a sinusoid. When performing circuit analysis, instead of using a real-valued driving function, we use a complex one, whose projection on the real axis (when rotating) produces the same sinusoidal. This complex quantity is called a *phasor*. By the use of phasors, the solution to a linear circuit in sinusoidal steady state can be obtained by relatively easy manipulation of complex numbers.

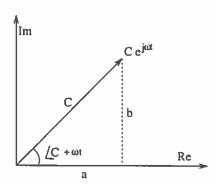

A phasor diagram is a graphical representation of complex exponentials, in the complex plane [27, chapter 5]. Consider the function  $Ce^{j\omega t_1}$ , whose characteristics are described in equation II.1 and represented graphically in Figure 8.

$$Ce^{j\omega t} = (a+jb)e^{j\omega t}$$

$$|Ce^{j\omega t}| = \sqrt{a^2 + b^2}$$

$$\angle Ce^{j\omega t} = \omega t + \angle C$$

$$\angle C = \arctan \frac{b}{a}$$

(II.1)

FIGURE 8. Graphical Representation of  $Ce^{j\omega t}$

In a circuit excited by a sinusoidal voltage source of frequency  $\omega$ , all variables (i.e. currents and voltages) are also sinusoids oscillating at the same frequency. If we represent each variable by a phasor, they will rotate at the same angular frequency, as if fastened together; what changes between each variable are its magnitude and phase angle. So a phasor diagram can be seen, at any given moment, as a snapshot

)

D

D

)

0

)

<sup>&</sup>lt;sup>1</sup>In electrical engineering, the complex operator  $j = \sqrt{-1}$  is used instead of the mathematical symbol i.  $\omega$  is the frequency of a sinusoidal wave, see equation II.2, and t is time.

of the set of rotating phasors that represent all quantities of the circuit.

9

0

0

)

9

)

Let us now consider a circuit with a pair of terminals, for which a voltage V and a current I can be defined

$$V(t) = Re(Ve^{j\omega t}) = |V|\cos(\omega t + \Delta V)$$

$$I(t) = Re(Ie^{j\omega t}) = |I|\cos(\omega t + \Delta I)$$

(II.2)

where V(t) and I(t) represent (real) functions of time, and V and I represent phasors in the frequency domain. The ratio between voltage and current will be called *impedance*, denoted by Z, and its inverse *admittance*, denoted by Y; i.e.,

$$Z(jw) = V/I$$

$$Y(jw) = I/V = 1/Z(jw)$$

(II.3)

The impedance and admittance for individual resistors, inductors, and capacitors are given in the Table 1.

| Element | Z(jw) | Y(jw) |       | $\angle V - \angle I$ |

|---------|-------|-------|-------|-----------------------|

| R       | R     | 1/R   | R     | 0                     |

| L       | jwL   | 1/jwL | wL    | +90                   |

| C       | 1/jwC | jwC   | 1/jwC | -90                   |

TABLE 1. Properties of Circuit Elements

For series elements, the current phasor is common and the voltage phasor is the sum of the element voltage phasors; so impedances in series add as in the case of resistors in series. The analogous case holds for elements in parallel

$$Z_{Ser}(jw) = \sum_{i} Z_{i}(jw)$$

$$Y_{Par}(jw) = \sum_{i} Y_{i}(jw)$$

(II.4)

Impedances and admittances can be used to perform circuit analysis using the same techniques as for networks with direct current sources, except that now all the quantities will be complex numbers; in the end, only the real parts will be considered as the result. This permits a graphical representation of Kirchoff's laws in terms of addition of phasors. This can be illustrated with the circuit in Figure 9, for which one phasor diagram (of the many possible) is shown in Figure 10.

FIGURE 9. An Electrical Circuit

FIGURE 10. A Possible Phasor Diagram for Circuit in Figure 9

D

μ

ř

)

.

0

## Power Factor and Phase Angle

An important concept that deserves consideration at this point is that of power factor. *Power* is defined as the rate of energy transfer; in terms of a circuit quantities, it is defined as the product of the instantaneous voltage and the instantaneous current that appears through an element.

$$p = VI \tag{II.5}$$

If the voltage and current of a circuit element are expressed by

$$V = V_{max} \cos(\omega t)$$

$$I = I_{max} \cos(\omega t - \theta)$$

(II.6)

the instantaneous power is

D

Ð

D

D

0

D

D

$$p = V_{max}I_{max}\cos(\omega t)\cos(\omega t - \theta)$$

(II.7)

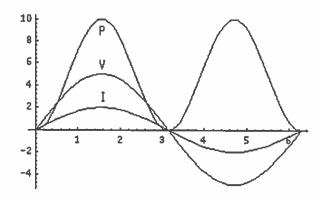

A positive value of P indicates power is being absorbed by the element. That is, the element is acting as a load or consumer of energy. This situation is encountered when the current has the same sign as the voltage drop in the element (i.e. current is flowing in the direction of voltage drop). In the other case, when voltage and current have different signs (i.e. current is flowing in the direction of voltage rise), energy is being transferred from the element to the system.

For a purely resistive element, voltage and current are in phase; current always

flows in the direction of voltage drop, therefore, it is always absorbing power. In a pure inductor or capacitor, the current is always 90 degrees out of phase with respect to the voltage. In that case, power alternates flowing to and from the element (i.e. acting as a load and a source, respectively).

9

0

D

D

By using trigonometric identities, the expression of equation II.7 is reduced to

$$p = \frac{V_{max}I_{max}}{2}\cos\theta(1+\cos2\omega t) + \frac{V_{max}I_{max}}{2}\sin\theta\sin2\omega t$$

(II.8)

The first term of equation II.8 is always positive, and is normally referred to as the real or active power. The second term alternates between positive and negative values; it is known as the reactive power and expresses the flow of energy alternately toward the load and toward the system. The cosine of the phase angle  $\theta$  between the voltage and current is called the power factor. An inductive circuit is said to have a lagging power factor, and a capacitive circuit is said to have a leading power factor. A resistive load has a unit power factor (i.e. voltage and current are in phase, so  $\theta$  is zero). Power, active power, and reactive power are very useful terms in describing the operation of a Power System (see section V).

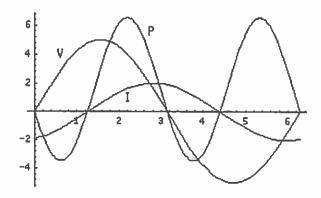

Figures 11 and 12 show the current, voltage, and power sine waves for circuits with unity and lagging power factors, respectively. Figure 11 represents a circuit with a net resistive effect. Power in a resistive circuit is always positive, that is, resistors have no means to store energy and are always dissipating it in form of heat. Figure 12 represents a circuit with net resistive and inductive effects, like the one in Figure 13.

FIGURE 11. Power in a Circuit with Unity Power Factor

FIGURE 12. Power in a Circuit with Lagging Power Factor

0

9

0

9

In that case, the inductor is storing energy (in the form of a magnetic field) when p becomes positive, and returning it to the system when p becomes negative. Notice that the average consumed power is the part dissipated by the resistor. Although the dissipated power depends only on the resistive part of the circuit, the magnitude of the current does increase with the reactive power. This increase in current will be reflected by an increase in losses and higher capacity and size are required in all transmission equipment.

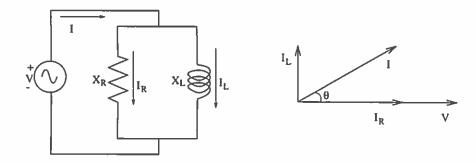

This problem can be corrected by inserting a capacitor in the circuit, as shown in Figure 14.

FIGURE 13. RL Circuit and Corresponding Phasor Diagram

FIGURE 14. RLC Circuit and Corresponding Phasor Diagram

In that case, (part of) the reactive power needed by the inductor is supplied by the capacitor. As a result, there is no reactive power traveling back and forth from the source to the load, and the magnitude of the resulting current is smaller. We can say that the power factor has been corrected.

D

0

0

## Complex Fans

An important feature of our reasoning engine is the ability to transition smoothly from qualitative to quantitative values in the process of reasoning. This can be accomplished by representing every value as an interval and performing all operations using interval algebra. Phasors are complex quantities, so we need two numbers to represent such a quantity. If we choose the rectangular representation, those two

numbers are the real and imaginary components of the complex number. In polar representation, a phasor is expressed by its magnitude and angle. Traditionally, in the field of Electrical Engineering, complex numbers are represented in rectangular form, because arithmetic operations are simpler in this representation. Our representation language talks about magnitudes and phase angles; for instance, given values for quantities  $V_1$  and  $V_2$ , the order relation  $V_1 > V_2$  can be used to limit the possible values of the magnitude of both quantities. If those quantities were represented in rectangular form, we can reduce the real, the imaginary, or both components to reduce the resulting magnitude. Similarly with angle values and angle ordering constraints. So, we decided to represent phasors in polar form.

D

D.

D

D

D

)

9

)

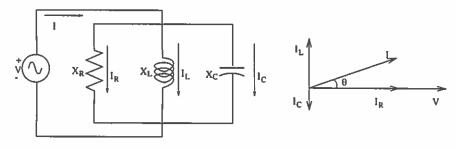

)

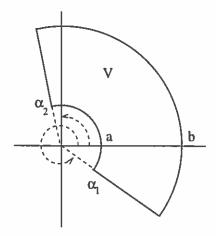

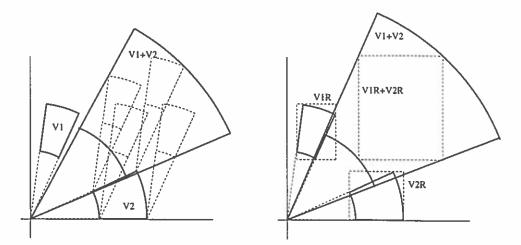

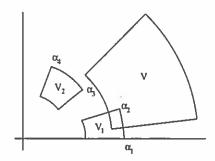

If we allow the magnitude and angle of a phasor to range over intervals, the resulting objects, instead of denoting a point in the complex domain, now span over circular segments. We call those circular segments complex fans. For example, fan V of Figure 15 is a phasor whose magnitude ranges from a to b, and whose angle ranges from  $\alpha_1$  to  $\alpha_2$ .

In this section, we develop the complex fan arithmetic that will be needed to perform value propagation on the domain of interval phasors, or complex fans. In developing the complex fan arithmetic, we pay special attention to providing minimality in the results. That is, the results of an operation is the smallest complex fan that encloses all possible results of that operation.

The basic arithmetic operations that need to be defined are +, -, \*, and  $\dot{}$ .

FIGURE 15. Example of a Complex Fan

Other operations can be defined in terms of the basic ones. The formulae for product, division, and negation (i.e. unary —), operate independently on magnitudes and angles. So the formulae for phasors can be used, performing standard interval operations, instead of real-valued ones. The formulae for addition (and subtraction, which is defined in terms of addition and negation) are more complicated, and we cannot just apply interval operators in a straightforward manner.

In this section, we develop an algorithm to evaluate complex fan addition, yielding the minimum complex fan that encloses all possible results. The derivation of the algorithm is justified by the mathematics for deriving the formulas presented here.

# Notation

The complex fan shown in Figure 15 can be represented as

)

$$V = Vm \angle V_{\alpha} \tag{II.9}$$

where  $V_m$  represents V's magnitude, and  $V_{\alpha}$  its angle.  $V_m$  ranges over the interval  $0 \le a \le V_m \le b$ , and  $V_{\alpha}$  ranges over the interval  $\alpha_1 \le V_{\alpha} \le \alpha_2$ . Then, the complex fan V can also be expressed as

$$V = [a, b] \angle [\alpha_1, \alpha_2] \tag{II.10}$$

Note that if a = b and  $\alpha_1 = \alpha_2$ , the complex fan reduces to a phasor (i.e. a point in the complex plane).

Throughout the rest of the chapter, when we deal with two fans, we assume

$$V_1 = V_{1m} \angle V_{1\alpha} = [a, b] \angle [\alpha_1, \alpha_2]$$

$$V_2 = V_{2m} \angle V_{1\alpha} = [c, d] \angle [\alpha_3, \alpha_4]$$

(II.11)

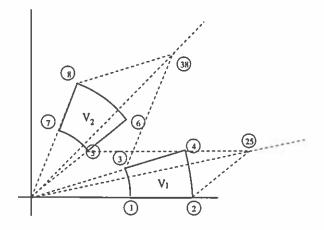

In the figures of section II.3, we (arbitrarily) number the corners of the fans as indicated in Figure 16. Also, the addition of two corners i and j will be indicated by point ij. For example, addition of points 2 and 5 yields point 25, as shown in the same figure.

### Product

As mentioned above, formulae for product, division, and negation of complex fans can be obtained by simply replacing real-valued operations by interval operations in the respective formulae for phasor arithmetic.

D.

)

Þ

0

)

)

FIGURE 16. Notation

The product of two phasors  $V = V_1 * V_2$  is given by the formula

D

3

D

D

0

0

$$V = ([a, b] * [c, d]) \angle ([\alpha_1, \alpha_2] + [\alpha_3, \alpha_4])$$

(II.12)

# Division

The quotient of two phasors  $V=V_1/V_2$  is analogous to the product

$$V = ([a, b]/[c, d]) \angle ([\alpha_1, \alpha_2] - [\alpha_3, \alpha_4])$$

(II.13)

# Negation

The negation of a complex fan is another complex fan, with the same magnitude, and whose angle is the complement of the angle of the original fan.

$$V = -V_1 = [a, b] \angle ([\alpha_1, \alpha_2] + [180, 180])$$

(II.14)

### Subtraction

Subtraction can be defined in terms of addition and negation as follows

$$V = V_1 - V_2 = V_1 + (-V_2)$$

(II.15)

# Addition

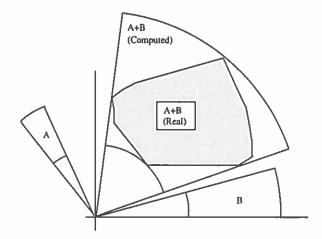

Addition presents a complication. There is no formula to add two phasors in polar form. In one approach, the addends (i.e. phasors) are converted to rectangular form, the addition is performed and then the result is transformed back into polar form. When we generalize the idea to intervals, the smallest rectangle that encloses a fan includes some points not present in the original fan. Then, when we convert the resulting rectangle to a fan, more points are included than are needed. This is illustrated in Figure 17

FIGURE 17. Imprecision Added by Representation Changes

)

D

D

þ

5

D

We will present an algorithm that computes the smallest possible fan that encloses the result of  $V_1 + V_2$ , where

)

D

b

>

)

Ò

>

)

$$V_1 + V_2 = \{v + w \mid (v, w) \in V_1 \times V_2\}$$

(II.16)

The result of the addition must be complete and minimal. To be complete, it must contain all possible results of the addition, as defined above. To be minimal, its boundaries (both, magnitude and phase angle) must be such that the intervals they represent cannot shrink without leaving possible results out. This implies that at least one result must fall on each of the boundaries of the resulting complex fan.

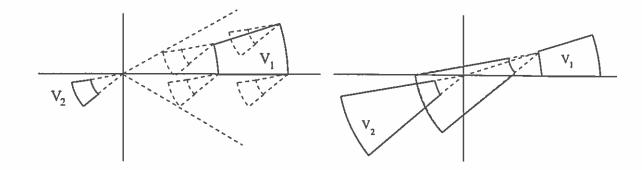

Clearly, one possible value can be obtained by adding the corners of the fans. Nevertheless, these extreme values do not necessarily produce the extreme values of the result. The only case when the corners produce the extreme results is when the fans span less than 90 degrees. So, we will decompose  $V_1$  and  $V_2$  into four fans, representing their intersection with each quadrant, taking as reference the smallest angle of the first fan (i.e.  $V_1$  always starts at zero). Ensuring this assumption might require a rotation, in which case, the final results will need to be corrected back to the original reference. For instance,  $V_1$  will be

$$V_1 = \bigcup_{i=1...4} V_{1i}$$

(II.17)

where

$$V_{1i} = (0, \infty) \angle [90(i-1), 90i] \cap V_1$$

(II.18)

Thus, addition can be expressed as

$$V = V_1 + V_2$$

$$= (V_{11} \cup V_{12} \cup V_{13} \cup V_{14}) + (V_{21} \cup V_{22} \cup V_{23} \cup V_{24})$$

$$= \{v + w \mid (v, w) \in (V_{11} \cup V_{12} \cup V_{13} \cup V_{14}) \times (V_{21} \cup V_{22} \cup V_{23} \cup V_{24})\}$$

(II.19)

and since Cartesian product distributes over union,

$$V = \{v + w \mid (v, w) \in (V_{11} + V_{21} \cup V_{11} + V_{22} \dots)\}$$

$$= \bigcup_{i,j=i\dots 4} V_{1i} + V_{2j}$$

(II.20)

Each partial addition is performed with fans that do not extend more than 90 degrees. We can categorize each partial addition into one of three cases: when the two addends are in the same, adjacent, or opposite quadrants. We analyze each case and determine a procedure to compute the partial results. The final result is the union of all the partial results. For each case considered, we will demonstrate that the minimality condition is met.

9

)

)

D

)

)

)

)

0

### Case 1: Same Quadrant

)

3

D

0

)

D

0

D

In this part, we consider the case when both fans are in the same quadrant. The analysis is made for the first quadrant; for other quadrants, we just apply a rotation, which will be corrected at the end of the process.

Consider the addition  $V = V_1 + V_2$ , where  $\alpha_1 = 0$ , since we take  $V_1$  as our reference. Vector algebra states that

$$V_{m} = \sqrt{V_{1m}^{2} + V_{2m}^{2} + 2V_{1m}V_{2m}\cos\theta}$$

$$V_{\alpha} = \tan^{-1}\left(\frac{V_{1m}\sin V_{1\alpha} + V_{2m}\sin V_{2\alpha}}{V_{1m}\cos V_{1\alpha} + V_{2m}\cos V_{2\alpha}}\right)$$

(II.21)

where  $\theta = V_{1\alpha} - V_{2\alpha}$ .

Since square root is a monotonic function,  $V_m$  reaches an extreme when  $V_m^2$  does. Since addition monotonically increases with its addends, and cosine is monotonically decreasing in  $\theta$ 's domain (i.e.  $0 \le \theta \le 90$ ), we have the following,

$$V_{m_{max}}^{2} = V_{1m_{max}}^{2} + V_{2m_{max}}^{2} + 2V_{1m_{max}}V_{2m_{max}}\cos\theta_{max}$$

$$= b^{2} + d^{2} + 2bd\cos\theta_{min}$$

$$V_{mmin}^{2} = V_{1mmin}^{2} + V_{2mmin}^{2} + 2V_{1mmin}V_{2mmin}\cos\theta_{min}$$

$$= a^{2} + c^{2} + 2ac\cos\theta_{max}$$

(II.22)

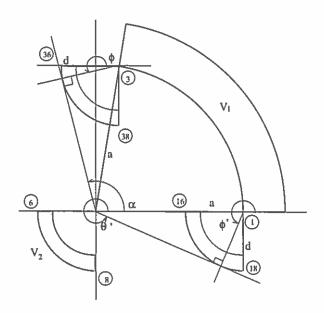

The final computation for the extremes of  $\theta$  and  $V_m$  (see Figure 18), can be expressed as follows

$$\theta_{max} = \max(\alpha_4 - \alpha_1, \alpha_2 - \alpha_3)$$

$$\theta_{min} = \begin{cases} 0 & V_{1\alpha} \cap V_{2\alpha} \neq \phi \ (\alpha_2 \ge \alpha_3) \\ \\ \alpha_3 - \alpha_2 & otherwise \end{cases}$$

$$V_{mmax} = \sqrt{V_{mmax}^2}$$

$$V_{mmin} = \sqrt{V_{mmin}^2}$$

(II.23)

FIGURE 18. Phasor Addition, Case 1

For the computation of  $V_{\alpha}$ ,  $\tan^{-1}$  is a monotonic function. To find the extremes of the function, all we need to do is find the extrema of its argument. A change of variables simplifies the expressions,

$$f(x, y, u, v) = \frac{x \sin u + y \sin v}{x \cos u + y \cos v}$$

(II.24)

The parallelogram rule for vector addition [46] suggests that the smallest pos-

D

0

.

D

0

D

D

sible angle occurs adding points 2 and 5, denoted by point 25 in Figure 19, and the largest angle occurs adding points 3 and 8, denoted by point 38 in the same figure.

)

0

D

D

)

FIGURE 19. Maximum and Minimum Angles in Phasor Addition

To prove our intuition, we first show that the minimum angle has to occur when adding some points in the boundaries of minimum angles. For a given  $x_0$  and  $y_0$  (i.e. fixing the magnitudes of both fans),

$$g_1(u,v) = \frac{x_0 \sin u + y_0 \sin v}{x_0 \cos u + y_0 \cos v}$$

(II.25)

The extremes are found where the gradient is zero,

$$\nabla g_1 = 0 (II.26)$$

$$\frac{\partial g_1}{\partial u} = \frac{x_0 \cos u (x_0 \cos u + y_0 \cos v) - (-x_0 \sin u) (x_0 \sin u + y_0 \sin v)}{(x_0 \cos u + y_0 \cos v)^2} = 0$$

$$\frac{\partial g_1}{\partial v} = \frac{y_0 \cos v (x_0 \cos u + y_0 \cos v) - (-y_0 \sin v) (x_0 \sin u + y_0 \sin v)}{(x_0 \cos u + y_0 \cos v)^2} = 0$$

$$x_0 + y_0 \cos(u - v) = 0$$

(II.27)

$x_0 = -y_0 \cos(u - v)$

Since  $x_0$ ,  $y_0$ , and  $\cos(u-v)$  are positive, there is no solution to equation II.27. Therefore, the function has no extremes in the given domain. So, we analyze how the function behaves on each variable. For a given  $u_0$  (i.e. fixing the angle of the second fan),

$$h_1(v) = g_1(u_0, v)$$

$$h'_1(v) = \frac{x_0^2 + x_0 y_0 \cos(u_0 - v)}{(x_0 \cos u_0 + y_0 \cos v)^2}$$

(II.28)

and for a given  $v_0$ ,

$$h_2(u) = g_1(u, v_0)$$

$$h_2'(u) = \frac{y_0^2 + x_0 y_0 \cos(u - v_0)}{(x_0 \cos u + y_0 \cos v_0)^2}$$

(II.29)

Since

9

Þ

D

D

0

D

$$-90 \le u_0 - v \le 90, \ 0 \le \cos(u_0 - v) \le 1 \tag{II.30}$$

therefore

$$h'_1(v) > 0$$

$h'_2(u) > 0$  (II.31)

This indicates that f (the angle of the result) grows with u and v (the angles of the addends), so it reaches its maximum (minimum) value in the domain, when u and v are maxima (minima).

We proceed to determine f's behavior with respect to x and y (the magnitudes of the addends).

$$g_2(x,y) = f(x, y, u_0, v_0)$$

$$= \frac{x \sin u_0 + y \sin v_0}{x \cos u_0 + y \cos v_0}$$

(II.32)

$$\nabla g_{2}(x,y) = 0$$

$$\frac{\partial g_{2}}{\partial x} = \frac{\sin u_{0}(x\cos u_{0} + y\cos v_{0}) - (\cos u_{0})(x\sin u_{0} + y\sin v_{0})}{(x\cos u_{0} + y\cos v_{0})^{2}}$$

$$\frac{\partial g_{2}}{\partial y} = \frac{\sin v_{0}(x\cos u_{0} + y\cos v_{0}) - (\cos v_{0})(x\sin u_{0} + y\sin v_{0})}{(x\cos u_{0} + y\cos v_{0})^{2}}$$

$$y \sin(u_0 - v_0) = 0$$

(II.33)

$x \sin(v_0 - u_0) = 0$

0

Ð.

)

)

D

D

D

D

D

Since x and y are both positive, solving equations II.33 reduces to solving  $\sin(u_0 - v_0) = 0$  and  $\sin(v_0 - u_0)$ . The solution to the first is found for  $u_0 - v_0 = k\pi$ ,  $k = 0, 1, 2 \dots$ , which is located outside the domain of the angle difference for the case we are analyzing. We analyze how the function behaves with respect to x and y (magnitudes). For a given  $y_0$  (i.e. fixing the magnitude of the second fan),

$$h_3(x) = g(x, y_0) = \frac{x \sin u_0 + y_0 \sin v_0}{x \cos u_0 + y_0 \cos v_0}$$

$$h'_3(x) = \frac{y_0 \sin(u_0 - v_0)}{(x \cos u_0 + y_0 \cos v_0)^2}$$

(II.34)

and for a given  $x_0$

)

)

)

9

)

)

)

)

$$h_4(y) = g(x_0, y) = \frac{x_0 \sin u_0 + y \sin v_0}{x_0 \cos u_0 + y \cos v_0}$$

$$h'_4(y) = \frac{x_0 \sin(v_0 - u_0)}{(x_0 \cos u_0 + y \cos v_0)^2}$$

(II.35)

From equations II.31, we see that to compute the maximum angle, we need to use  $\alpha_2$  and  $\alpha_4$ . Assuming  $u_0 = \alpha_2$  and  $v_0 = \alpha_4$ , we can distinguish three cases. When  $\alpha_2 > \alpha_4$ ,  $\sin(u_0 - v_0) > 0$ , which makes  $h'_3(x) > 0$  and  $h'_4(y) < 0$ , we compute the maximum angle using x = b (the maximum) and y = c (the minimum). When  $\alpha_2 < \alpha_4$ , which makes  $h'_3(x) < 0$  and  $h'_4(y) > 0$ . We compute the maximum angle using x = a and y = d. When  $\alpha_2 = \alpha_4$ , the maximum angle is equal to  $\alpha_2 = \alpha_4$ , i.e. it does not depend on the values of of x and y.

To compute the minimum angle, we assume  $u_0 = \alpha_1$  and  $v_0 = \alpha_3$ . Here, we

have only one case,  $\alpha_1 \leq \alpha_3$ , and the minimum angle is computed using x = b and y = c.

Figure 20 shows a summary of the partial computation of fan addition for case 1.

AddCasel(

$$V_1$$

,  $V_2$ )

if  $\alpha_2 \ge \alpha_3$

$\theta_{min} = 0$

else

$\theta_{min} = \alpha_2 - \alpha_3$

$\theta_{max} = \max(\alpha_4 - \alpha_1, \alpha_2 - \alpha_3)$

$$V_{mmin} = \sqrt{a^2 + c^2 + 2ac\cos\theta_{max}}$$

$$V_{mmax} = \sqrt{b^2 + d^2 + 2bd\cos\theta_{min}}$$

$$V_{\alpha min} = \tan^{-1}\left(\frac{b\sin\alpha_1 + c\sin\alpha_3}{b\cos\alpha_1 + c\cos\alpha_3}\right)$$

if  $\alpha_2 < \alpha_4$

$$V_{\alpha max} = \tan^{-1}\left(\frac{a\sin\alpha_2 + d\sin\alpha_4}{a\cos\alpha_2 + d\cos\alpha_4}\right)$$

else if  $\alpha_2 > \alpha_4$

$$V_{\alpha max} = \tan^{-1}\left(\frac{b\sin\alpha_2 + c\sin\alpha_4}{b\cos\alpha_2 + c\cos\alpha_4}\right)$$

else if  $\alpha_2 > \alpha_4$

$$V_{\alpha max} = \alpha_2$$

return( $[V_{mmin}, V_{mmax}], \angle[V_{\alpha min}, V_{\alpha max}]$ )

FIGURE 20. Pseudo-Code for Case 1

# Case 2: Adjacent Quadrants

)

1

0

5

)

0

0

We can assume that fan  $V_1$  will be in the first quadrant, and fan  $V_2$  will be in the second. If that is not the case, we can make a rotation, and the results will be

corrected at the end. So, we have the following conditions for case 2:

)

D.

0

D

D

0

D

$$0 \le \alpha_1 \le \alpha_2 \le 90$$

$$90 \le \alpha_3 \le \alpha_4 \le 180$$

$$and (\alpha_4 - \alpha_1) > 90$$

(II.36)

If the last condition  $(\alpha_4 - \alpha_1) > 90$  is not satisfied, the problem can be reduced to Case 1 by a simple rotation. From equations II.21, if we fix the magnitudes,  $V_m$  depends solely on  $\theta$ .

$$V_m = f_2(x, y, \theta) = x^2 + y^2 + 2xy \cos \theta$$

(II.37)

Since  $0 \le \theta \le 180$ , and cosine is monotonically decreasing with respect to  $\theta$ ,  $V_m$  reaches a maximum when  $\theta$  is at its minimum value. When  $\theta \le 90$ ,  $0 \le \cos \theta \le 1$ , and  $f_2$  reaches a maximum when x and y reach their maxima. When  $\theta > 90$ ,  $-1 \le \cos \theta < 0$ , we have a more complex situation. Analyzing how  $f_2$  changes with  $\theta$ ,

$$\frac{\partial f_2}{\partial \theta} = 2xy(-\sin \theta)$$

$$90 < \theta \le 180$$

$$\frac{\partial f_2}{\partial \theta} \le 0$$

(II.38)

we have a minimum where the derivative is zero (i.e.  $\theta = 180$ ). If that point does not

belong to  $\theta$ 's domain, we know that the function is monotonically decreasing with respect to  $\theta$ . That is,  $V_{mmax}$  occurs for  $\theta_{min}$ , and  $V_{mmin}$  occurs for  $\theta_{max}$ .

)

0

D

D

D

0

9

0

Þ

0

Now, let us see how  $V_m$  behaves with respect to x and y, for a given  $\theta$ .

$$V_m = f_3(x, y) = f(x, y, \theta_0)$$

$$\nabla f_3 = 0$$

$$\frac{\partial f_3}{\partial x} = 2x + 2y \cos \theta_0 = 0$$

$$\frac{\partial f_3}{\partial y} = 2y + 2x \cos \theta_0 = 0$$

(II.39)

$$x = -y\cos\theta_0$$

$$y = -x\cos\theta_0 \qquad (II.40)$$

To compute  $V_{mmax}$  we consider  $\theta_0 = \theta|_{min}$ . We distinguish three regions.

$$\theta_0 \begin{cases} < 90 \\ = 90 \\ > 90 \end{cases}$$

(II.41)

For the case when  $\theta_0 \leq 90$ ,  $\cos \theta_0 \geq 0$ , so we see that

$$\frac{\partial f_3}{\partial x} > 0$$

$$\frac{\partial f_3}{\partial y} > 0 \tag{II.42}$$

therefore,  $V_m$  reaches a maximum at  $x_{max}$ ,  $y_{max}$ . That is,

)

D

D

)

D

0

)

$$V_{mmax} = \sqrt{b^2 + d^2 + 2bd\cos\theta_{min}} \tag{II.43}$$

For the case when  $90 < \theta_0 < 180, -1 \le \cos \theta_0 < 0$ ,

$$\frac{\partial f_3}{\partial x} = 2x + 2y \cos \theta_0 = 0$$

$$x = -y \cos \theta_0 \tag{II.44}$$

We note that  $\frac{\partial^2 f_3}{\partial x^2} = 2$ , which implies the extrema above is a minimum. This in turn implies that the maximum of  $V_m$  has to be in one of the corners of  $V_{1m} \times V_{2m}$ , when the angle is minimum. That is (see Figure 21),

$$V_{mmax} = \max(p35_m, p36_m, p45_m, p46_m)$$

(II.45)

To compute  $f_{min}$  we consider  $\theta_0 = \theta_{max} = \alpha_4 - \alpha_1$ . We find only one case,  $90 < \theta_0 \le 180$  (see the case definition, equation II.36), and the minimum is not necessarily in one of the corners. From equation II.44, if x and y are reals, we find a minimum at  $x = -y \cos \theta_0$ . In general, x and y are real intervals, so if  $I_x = x \cap -y \cos \theta_0 \neq \emptyset$ , we

FIGURE 21. Fan Addition in the Second Case.

D

)

D

have a minimum at  $x_m = I_{xmin}$ . If they do not intersect, depending on whether x falls to the left or right of  $-y \cos \theta_{max}$ , we can use  $x_{max}$  or  $x_{min}$ , respectively (see Figure 22). The situation is symmetric for y, depending on whether y intersects, or falls to the left

FIGURE 22. Minimum Magnitude of Phasor Addition; x and y Are Intervals.

or right of  $-x\cos\theta_{max}$ , we can use  $y_m = I_{y_{min}}$ ,  $y_{max}$ , or  $y_{min}$ , respectively. Figure 23 shows the algorithm to compute the magnitude for fan addition, for Case 2.

We now proceed to derive the minimum and maximum values for the angle. From equation II.31, we have that  $h'_1(v) > 0$  and  $h'_2(u) > 0$ . This indicates that the maximum angle has to be computed using  $\alpha_2$  and  $\alpha_4$ .

From equation II.40, we have that  $x_0 = -y_0 \cos \theta$ , where  $0 \le \theta \le 180$ . For  $\theta =$

```

MagnitudeCase2(V_1, V_2)

\theta_{min} = \alpha_3 - \alpha_2

\theta_{max} = \alpha_4 - \alpha_1

if \theta_{min} \leq 90