# COMPILER-ASSISTED PROGRAM MODELING FOR PERFORMANCE TUNING OF SCIENTIFIC APPLICATIONS

by

KEWEN MENG

# A DISSERTATION

Presented to the Department of Computer and Information Science and the Division of Graduate Studies of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

September 2021

# DISSERTATION APPROVAL PAGE

Student: Kewen Meng

Title: Compiler-Assisted Program Modeling for Performance Tuning of Scientific Applications

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

| Boyana Norris | Chair                        |

|---------------|------------------------------|

| Allen Malony  | Core Member                  |

| Jee Choi      | Core Member                  |

| Sara Hodges   | Institutional Representative |

and

Andy Karduna

Interim Vice Provost for Graduate Studies

Original approval signatures are on file with the University of Oregon Division of Graduate Studies.

Degree awarded September 2021

$\bigodot$  2021 Kewen Meng

This work, including text and images of this document but not including supplemental files (for example, not including software code and data), is licensed under a Creative Commons

Attribution-NonCommercial-NoDerivatives 4.0 International License.

#### DISSERTATION ABSTRACT

Kewen Meng

Doctor of Philosophy

Department of Computer and Information Science

September 2021

Title: Compiler-Assisted Program Modeling for Performance Tuning of Scientific Applications

Application performance models are important for both software and hardware development. They can be used to understand and improve application performance, to determine what architectural features are important to a particular program component, or to guide the design of new architectures. Creating accurate performance models of most computations typically requires significant expertise, human effort, and computational resources. Moreover, even when performed by experts, it is necessarily limited in scope, accuracy, or both. This research considers a number of novel static program analysis techniques to create performancerelated program representations of high-performance computations. These program representations can be used to model performance or to support efficient and accurate matching of computational kernels. We develop two different tools for static analysis-based program representation and demonstrate how they can be used for the optimization of scientific applications.

This dissertation includes previously published and unpublished co-authored material.

# CURRICULUM VITAE

### NAME OF AUTHOR: Kewen Meng

# GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene, OR, USA Xidian University, Xi'an, Shaanxi, China

# DEGREES AWARDED:

Doctor of Philosophy, Computer and Information Science, 2021, University of Oregon

Master of Science, Computer and Information Science, 2015, University of Oregon

Master of Engineering, Computer Technology, 2013, Xidian University

## AREAS OF SPECIAL INTEREST:

High-Performance Computing Compiler Optimization Machine Learning

# PROFESSIONAL EXPERIENCE:

Graduate Research Fellow, University of Oregon, 2016-2020

SDE Intern, Facebook, Fall 2019

SDE Intern, Databricks, Summer 2019

Research Intern, Lawrence Livermore National Laboratory (LLNL), Summer 2018

Research Intern, Lawrence Livermore National Laboratory (LLNL), Summer 2017

Graduate Teaching Fellow, University of Oregon, 2013-2016

GRANTS, AWARDS AND HONORS:

Student Travel Grant, Supercomputing (SC), 2017 NSF Student Travel Grant, Cluster, 2017

#### **PUBLICATIONS:**

- Meng, K. & Norris, B. (2021) From CPU to GPU A Unified Framework for CPU/GPU Performance Optimization. [In preparation]

- Meng, K. & Norris, B. (2020). Guiding Code Optimizations with Deep Learning-Based Code Matching. The 33rd International Workshop on Languages and Compilers for Parallel Computing (LCPC)

- Meng, K. & Lim, R. & Norris, B. & Malony, A. (2018). Performance Modeling through Hybrid Static/Dynamic Analysis. Workshop on Modeling and Simulation of Systems and Applications (ModSim). [Poster]

- Meng, K. & Norris, B. (2017). Mira: A framework for static performance analysis. *IEEE International Conference on Cluster Computing* (CLUSTER), 100, 103-113.

#### ACKNOWLEDGMENTS

I know that when I start to write this section, this means that my Ph.D. study is about to end. Many times, I tried to imagine what I would say at this moment, but I never thought I would be speechless with emotions. People say that completing a Ph.D. is not an easy task, and I am not an exception. The Ph.D. journey was full of joy, disappointment, excitement, and frustration. Day after day, we kept practicing and training to bravely face the challenges in research and in life.

I owe many thanks to Dr. Boyana Norris. I am so blessed to have her as my Ph.D. advisor. She provided me with tremendous research freedom and always encouraged me to explore various areas and try anything that I am interested in. Boyana patiently taught me how to conduct research, what to do in solving a problem and how to write a paper. Her advising is always on the point, and the editing is elegant. Besides, her positive attitude towards the challenges influences me all the time, especially during the dark time of the pandemic. With her brilliance, integrity, diligence, and caring, Boyana shows what a good scholar and advisor should be. Without her support, I would not have made it this far.

I am fortunate to have Dr. Allen Malony, Dr. Jee Choi, and Dr. Sara Hodges on my committee. Thanks for the significant amount of time they spent and the valuable feedback during my DAC meetings and oral defense. I also would like to thank all the members of HPCL for their generous help. I always enjoy the conversations with Samuel Pollard and Brian Gravelle. I thank Cheri Smith, our graduate program coordinator, for helping us out with all the tedious paperwork

vii

and teaching me a lot of interesting things about the culture. I am grateful for having so many good friends here at the University of Oregon.

I take this opportunity to thank the Carnes family. I still clearly remember the day I met with Carl and Karl on the plane, which is the first day I arrived in the U.S. They treated me like one of the family, and we had great times at Thanksgiving and Christmas. It is so hard for me to forget the delicious food they made. Thanks for having me and making Eugene my second hometown.

Thanks to my parents for their unconditional love and support for me to pursue my dream. They encourage me, inspire me, and are being with me to climb over the steep mountain and walk through the stormy sea. Thanks, YW, for the encouragement and being there with me at the beginning of this journey.

Last but not least, I am thankful that my research was supported by the Scientific Discovery through Advanced Computing (SciDAC) program of the U.S. Department of Energy through the RAPIDS Institute. I dedicate this dissertation to my grandmother.

# TABLE OF CONTENTS

| Chapter Pa                                                                                                        | ge |

|-------------------------------------------------------------------------------------------------------------------|----|

| I. INTRODUCTION                                                                                                   | 1  |

| 1.1. Motivation $\ldots$         | 1  |

| 1.2. Research Questions $\ldots$ | 2  |

| 1.3. Research Approach                                                                                            | 3  |

| 1.4. Dissertation Outline                                                                                         | 4  |

| 1.5. Co-Authored Material                                                                                         | 5  |

| II. BACKGROUND                                                                                                    | 7  |

| 2.1. Introduction                                                                                                 | 7  |

| 2.2. Analytical Modeling Approaches                                                                               | 7  |

| 2.2.1. Manual Analytical Modeling                                                                                 | 12 |

| 2.2.2. Automatic Analytical Modeling                                                                              | 14 |

| 2.2.3. Advantages and Disadvantages                                                                               | 17 |

| 2.3. Empirical Modeling Approaches                                                                                | 19 |

| 2.3.1. Performance Data Collection                                                                                | 19 |

| 2.3.2. Model Generation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                            | 23 |

| 2.3.3. Advantages and Disadvantages                                                                               | 28 |

| 2.4. Simulation-based Modeling Approaches                                                                         | 30 |

| 2.4.1. Data Representation for Simulation                                                                         | 30 |

| 2.4.2. Performance Data Collection                                                                                | 35 |

| 2.4.3. Advantages and Disadvantages                                                                               | 41 |

| 2.5. Summary                                                                                                      | 43 |

| Chapter Page                                                                                          |

|-------------------------------------------------------------------------------------------------------|

| III.MIRA                                                                                              |

| 3.1. Motivation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 47            |

| 3.2. Background                                                                                       |

| 3.3. Approach                                                                                         |

| 3.3.1. Processing Input Files                                                                         |

| 3.3.2. Generating Metrics $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 54$                |

| 3.3.3. Generating Models $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 55$          |

| 3.4. Evaluation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $69$ |

| 3.4.1. Experiment Environment                                                                         |

| 3.4.2. Benchmarks $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ 70               |

| 3.4.3. Mini Application                                                                               |

| 3.4.4. Results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$                              |

| 3.5. Summary                                                                                          |

| IV.MELIORA                                                                                            |

| 4.1. Motivation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$           |

| 4.2. Background                                                                                       |

| 4.3. Approach                                                                                         |

| 4.3.1. The Hybrid Control Flow Graph                                                                  |

| 4.3.2. hCFG Metrics                                                                                   |

| 4.3.3. Metric Extraction                                                                              |

| 4.3.4. Graph Representation Learning                                                                  |

| 4.3.5. Using the Model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$                       |

| 4.4. Evaluation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$   |

| 4.4.1. Experiment Environment                                                                         |

| 4.4.2. Dataset Generation                                                                             |

| Chapter                                                                                                   | Page  |

|-----------------------------------------------------------------------------------------------------------|-------|

| 4.4.3. Results                                                                                            | . 99  |

| 4.5. Related Work                                                                                         | . 109 |

| 4.6. Summary                                                                                              | . 111 |

| V. MELIORA-BASED OPTIMIZATION OF CUDA<br>COMPUTATIONS                                                     | . 112 |

| 5.1. Motivation $\ldots$ | . 112 |

| 5.2. Approach                                                                                             | . 113 |

| 5.2.1. Data Dependency Metrics                                                                            | . 115 |

| 5.2.2. Delivering Loop-to-Loop Matching                                                                   | . 116 |

| 5.2.3. Static Analysis for GPUs                                                                           | . 118 |

| 5.2.4. Unifying the Workflow for CPU/GPU Code Optimization                                                | n 121 |

| 5.3. Evaluation $\ldots$ | . 122 |

| 5.3.1. Experiment Methodology                                                                             | . 122 |

| 5.3.2. Results                                                                                            | . 123 |

| 5.4. Summary                                                                                              | . 127 |

| VI.CONCLUSIONS AND FUTURE WORK                                                                            | . 128 |

| 6.1. Conclusions                                                                                          | . 128 |

| 6.2. Future Work                                                                                          | . 129 |

| REFERENCES CITED                                                                                          | . 130 |

# LIST OF FIGURES

# Figure

# Page

| 1.  | The LogP model. From $[34]$                                                  | 9  |

|-----|------------------------------------------------------------------------------|----|

| 2.  | Program annotation used in Palm framework [126]                              | 15 |

| 3.  | Workflow of the COMPASS framework. From [79]                                 | 16 |

| 4.  | A fully connected feed-forward ANN. From [65]                                | 22 |

| 5.  | The workflow for parallelism mapping. From $[137]$                           | 24 |

| 6.  | The Performance modeling and prediction framework. From $[27]$               | 32 |

| 7.  | Workflow for performance data collection. From $[26]$                        | 35 |

| 8.  | The architecture of BigSim. From $[145]$                                     | 39 |

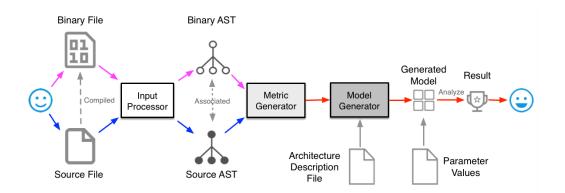

| 9.  | Workflow of Mira for generation of performance model and analysis            | 47 |

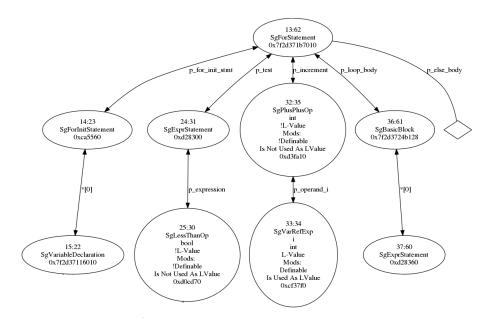

| 10. | Loop structure from a C++ source code AST fragment<br>(ROSE-generated graph) | 52 |

| 11. | Partial binary AST (ROSE-generated graph).                                   | 53 |

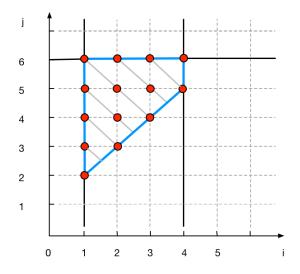

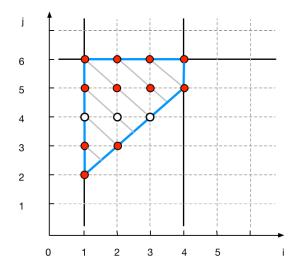

| 12. | Polyhedral representation of a nested loop.                                  | 56 |

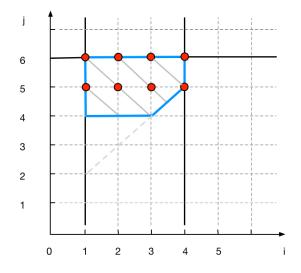

| 13. | Polyhedral representation with the $if$ constraint                           | 57 |

| 14. | The <i>if</i> constraint causing holes in the polytope                       | 57 |

| 15. | Exceptions in polyhedral modeling                                            | 58 |

| 16. | Original source code.                                                        | 66 |

| 17. | Python model code excerpt for the <i>foo</i> function                        | 66 |

| 18. | Python model code for the main program                                       | 67 |

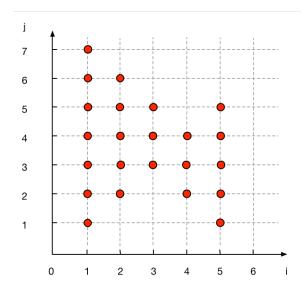

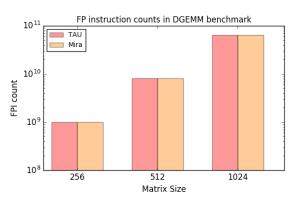

| 19. | Instruction distribution of function $cg_solve.$                             | 68 |

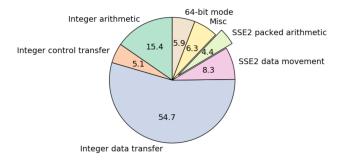

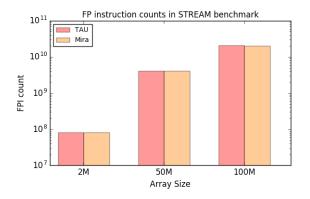

| 20. | Validation of floating-point instruction counts.                             | 71 |

| Figu | Page                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

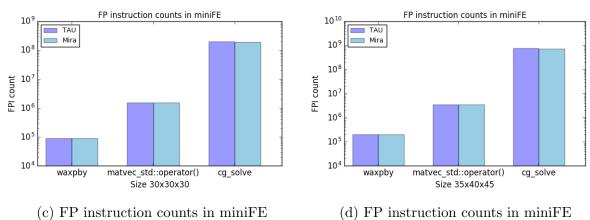

| 21.  | Meliora's workflow for code representation-based model<br>generation and optimization                                                                                                                                                                                                                                                                                                                                    |

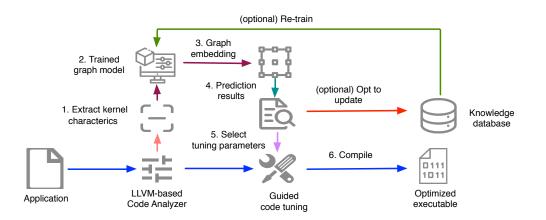

| 22.  | hCFG for the code fragment in List 4.1 (Meliora-generated graph) $84$                                                                                                                                                                                                                                                                                                                                                    |

| 23.  | Model self-validation at loop-level granularity. BiCG@1<br>indicates the first loop extracted from BiCG kernel in a<br>top-down manner                                                                                                                                                                                                                                                                                   |

| 24.  | Similarity between test kernels and training dataset loops computed as the cosine distance between their hCFG embeddings 103                                                                                                                                                                                                                                                                                             |

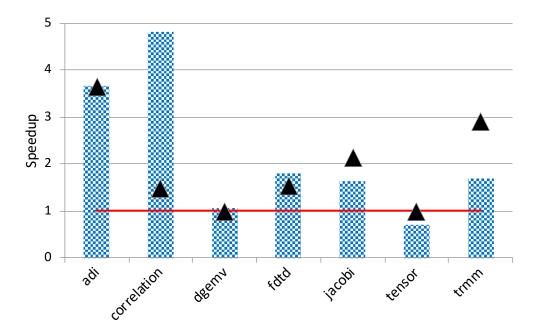

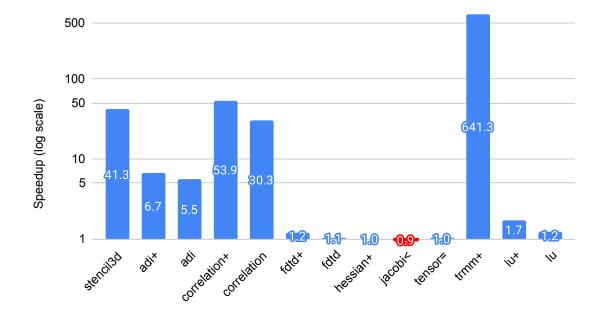

| 25.  | Speedup over the unoptimized (base) versions: bars for<br>Meliora-matched optimizations, black triangles for empirical<br>autotuning results, and a red line for the baseline performance 106                                                                                                                                                                                                                            |

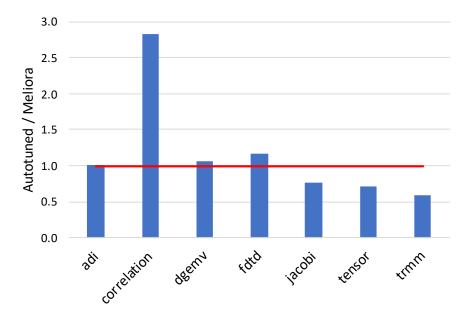

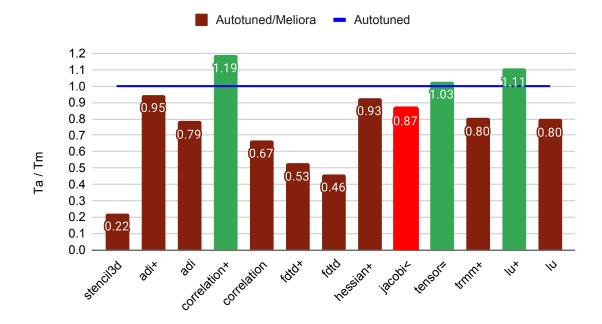

| 26.  | Comparison with empirically tuned performance. Values<br>greater than one indicate that Meliora-based optimizations<br>outperformed the empirical autotuner                                                                                                                                                                                                                                                              |

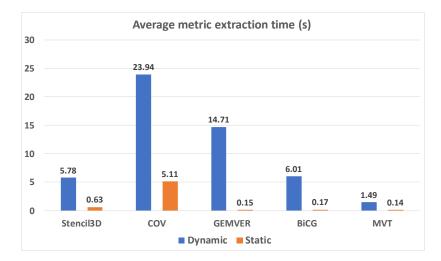

| 27.  | Comparison between the static and dynamic strategies<br>for metric extraction. The X-axis lists the kernels and the<br>Y-axis is the time in seconds.                                                                                                                                                                                                                                                                    |

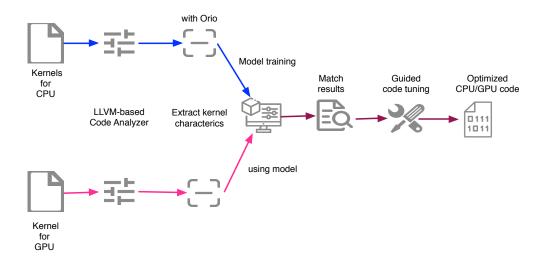

| 28.  | Unified workflow for CPU/GPU code optimization                                                                                                                                                                                                                                                                                                                                                                           |

| 29.  | Speedup of Meliora-matched optimizations w.r.t. a<br>baseline version using default parameters and compiler<br>optimizations. In all cases except for jacobi, the Meliora<br>versions were at least as fast as the base version, which uses<br>the default optimization parameters in Table 10                                                                                                                           |

| 30.  | Ratio of autotuning execution time (Ta) to Meliora-based<br>execution time (Tm) of the SPAPT benchmarks. The<br>green bars (values above 1.0) indicate that Meliora-based<br>versions outperformed the traditionally autotuned versions.<br>Values smaller than 1.0 indicate that autotuning can yield<br>additional benefits. In all cases except for jacobi, the<br>Meliora versions were faster than the base version |

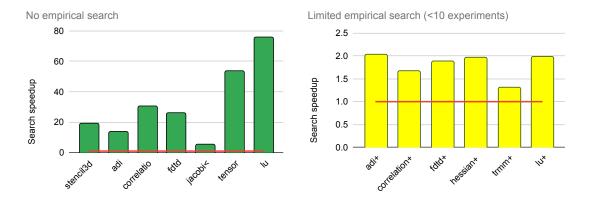

Figure

| 31. | Comparison with empirically tuned performance. Left:          |

|-----|---------------------------------------------------------------|

|     | Meliora-guided optimizations applied without empirical        |

|     | search (technically the speedup is infinity, but here we show |

|     | the overall time of evaluating the code version). Right:      |

|     | Restricted empirical autotuning, limiting the search around   |

|     | the Meliora-identified parameters                             |

Page

# LIST OF TABLES

# Table

# Page

| Loop coverage in high-performance applications                                                                                                                                   | •                                                                                         | •                                                                                         | •                                                                                         | •                                                   | •                                                   | •                                                   | •                                                   | 59                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Categorized instruction counts of function ${\tt cg\_solve}.$                                                                                                                    | •                                                                                         | •                                                                                         |                                                                                           |                                                     | •                                                   | •                                                   | •                                                   | 68                                                                                                                                                                                                                                                     |

| FPI counts in the STREAM benchmark                                                                                                                                               | •                                                                                         | •                                                                                         |                                                                                           | •                                                   | •                                                   | •                                                   | •                                                   | 69                                                                                                                                                                                                                                                     |

| FPI counts in DGEMM benchmark                                                                                                                                                    | •                                                                                         | •                                                                                         |                                                                                           |                                                     | •                                                   | •                                                   | •                                                   | 69                                                                                                                                                                                                                                                     |

| FPI Counts in miniFE                                                                                                                                                             | •                                                                                         | •                                                                                         |                                                                                           | •                                                   | •                                                   | •                                                   | •                                                   | 70                                                                                                                                                                                                                                                     |

| Graph attributes in hCFG                                                                                                                                                         |                                                                                           | •                                                                                         |                                                                                           |                                                     | •                                                   | •                                                   | •                                                   | 85                                                                                                                                                                                                                                                     |

| Selected kernels for dataset generation                                                                                                                                          |                                                                                           | •                                                                                         |                                                                                           |                                                     |                                                     | •                                                   | •                                                   | 98                                                                                                                                                                                                                                                     |

| Meliora's matches for a set of new codes' loops. The<br>adi@132 notation indicates the loop starting at line 132<br>of the adi code.                                             |                                                                                           |                                                                                           |                                                                                           |                                                     |                                                     |                                                     |                                                     | 102                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                  |                                                                                           |                                                                                           |                                                                                           |                                                     |                                                     |                                                     |                                                     |                                                                                                                                                                                                                                                        |

| The default parameters in the Orio-generated CUDA implementations of the test SPAPT kernels and their autotuning (AT) ranges in the tuning specifications (using Python syntax). |                                                                                           |                                                                                           |                                                                                           |                                                     |                                                     |                                                     |                                                     | 124                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                  | Categorized instruction counts of function cg_solve<br>FPI counts in the STREAM benchmark | Categorized instruction counts of function cg_solve<br>FPI counts in the STREAM benchmark | Categorized instruction counts of function cg_solve<br>FPI counts in the STREAM benchmark | Categorized instruction counts of function cg_solve | adi@132 notation indicates the loop starting at line 132         of the adi code.         Search speedup for the unseen kernels.         The default parameters in the Orio-generated CUDA         implementations of the test SPAPT kernels and their |

#### CHAPTER I

#### INTRODUCTION

Performance models are a type of reduced representation of the behavior of programs. They can be used to describe and predict the behavior of an application to provide software developers and researchers with insightful information about the execution status to help them identify the potential bottlenecks to further optimize the performance. Performance modeling techniques fall into three categories by the method of generation and data collection: analytical, empirical, and simulation-based approaches. Analytical modeling involves creating parameterized expressions by abstracting static or dynamic characterizations of an application. Empirical modeling methods rely on performance data obtained during the actual execution of programs on the target architecture. Simulationbased approaches provide a software environment that mimics a computer, on which the program can be "executed". Software performance models obtained by any combination of these approaches are an essential tool for designing and using current and future architectures.

#### 1.1 Motivation

As the development of new architectures accelerates, the computing capability of high-performance computing (HPC) systems continues to increase dramatically. However, many applications cannot fully use the available computing potential, wasting a considerable amount of resources and human effort spent on non-portable optimization. Missed opportunities are partially due to the inability to fully utilize available computing resources or take advantage of specific capabilities of architectures during application development that mainly

relies on high-level languages and compiler optimizations. Hence, modeling program behavior at a fine granularity is an essential component of understanding performance bottlenecks and potential of implementations.

Performance models are helpful not only during the implementation of the program but also for the entire software life-cycle. For example, a performance model is able to provide guidance to the application developers in choosing the most suitable algorithm to reach some performance goal. In the phase of application testing, it offers direct feedback of the performance and resource consumption of an application by adjusting parameters. In addition to software development, performance modeling also plays an important role in system design and tuning. Specifically, performance models are capable of describing non-existent hardware, which helps researches to explore the hypotheses when designing new systems. For example, models can help select the best network topology to connect nodes in order to be more efficient for a large-scale parallel system. A performance model can be used to indicate the expected design performance of a platform with a given configuration, which, when compared with the measurement performance by benchmarking, would reveal tuning opportunities. However, performance models are still difficult to create and maintain as software evolves. Hence, automating the generation of performance models would increase their use in practice and can have significant impact on both software and hardware development.

#### **1.2 Research Questions**

In this thesis, our goal is to address the following high-level research question through the three sub-questions that focus on specific approach strategies.

What program representations enable the static performance modeling and accurate matching of key computational kernels to support manual or compiler optimizations?

- **RQ1** Can we use static binary analysis to construct representations of programs for performance modeling?

- **RQ2** Can we use compiler-generated intermediate representations to create program embeddings that allow accurate matching of loop-based computations?

- **RQ3** Can we optimize GPU computations based on language and architectureindependent program representation matching?

#### 1.3 Research Approach

In this work, we present novel program representations and performance modeling methods to aid in the optimization of scientific applications. In existing performance modeling tools, a considerable amount of research focuses on dynamic approaches, which rely on runtime information to optimize the target applications, whereas static performance modeling receives significantly less attention. Although performance models based on runtime data are potentially more accurate, descriptive, and easier to generate compared to static methods, their high runtime cost and inability to capture all possible program behavior are significant limitations. In contrast, static performance modeling is preferable when a complete (covering all execution paths) model is needed quickly, or when wishing to model performance on non-existent architectures.

In this thesis, we introduce new program representations and develop methodologies for the generation of performance models and program optimization suggestions through primarily static code analysis. As the input to our analysis, we consider both binaries and compiler-generated intermediate program representations. The novelty of our approach is that in the performance tuning cycle we focus on kernel identification and reuse of existing optimal tuning parameters. Thus the static code analysis in our approach plays a critical role. It extracts metrics and generates reasonable representation to accurately describe the target kernel. Moreover, we leverage machine learning technique on code identification to further reduce the computation costs.

#### **1.4** Dissertation Outline

This remainder of this dissertation is organized as follows.

- Chapter II Background. We categorize the existing modeling approaches into three groups: analytical, empirical, and simulation-based modeling methods based on the performance data collection techniques and the approach for model generation. This chapter provides insightful details about each category and the comparisons among the different approaches. By understanding the development of performance modeling approaches and the advantages and disadvantages of each category, we find the space where we can improve in this area.

- Chapter III Mira. We present Mira [91] framework as our efforts to solve the first research question. In this work, we leverage the static analysis on the combination of the source and the binary code to overcome the problems caused by solely relying on one type of code. The parameterized model

achieves the good accuracy compared to the results from dynamic analysis in its estimates of floating-point operations.

- Chapter IV Meliora. We propose the Meliora [92] framework for solving the second research question. Meliora can accurately match loop-based computations based on the graph representation derived from a compilergenerated intermediate representation. By using the matching results, we are able to guide the CPU optimization while greatly reducing the cost of the process for empirically searching the performance tuning space.

- Chapter V Meliora-based Optimization of CUDA Computations. In this chapter we apply the approach described in Chapter IV to improving the efficiency and performance of GPU optimization. We show that the set of program features and control-flow-based graph representation can also capture parallelism-relevant characteristics. We demonstrate significant improvement in autotuning performance for CUDA versions of the SPAPT autotuning benchmark.

- Chapter VI Conclusions and Future Work. We summarize our contributions of this dissertation in the context of our research questions and discuss future research directions.

### 1.5 Co-Authored Material

This dissertation includes work from previously published co-authored material. This section lists the chapters with the publications and their authors.

Chapter III is based on the collaboration research [91] between Boyana Norris (UO) and myself.

- Chapter IV is based on the collaboration research [92] between Boyana Norris (UO) and myself.

- Chapter V is based on the unpublished research between Boyana Norris (UO) and myself.

#### CHAPTER II

## BACKGROUND

## 2.1 Introduction

Performance models are structural representations of program behavior which are descriptive and predictive. Models can. provide software developers with useful information about potential bottlenecks and help them identify optimization opportunities.

Although performance models may emphasize different performance metrics according to specific requirements, they aim to answer several questions in general: What is the estimated execution time of an application? What is the best execution time that an application can achieve? What is the expected execution time if one (or more) application parameter changes, for instance the number of processors? How much memory is required to run the program and achieve the best runtime?

In this chapter, we categorize the performance modeling approaches into three groups, analytical, empirical and simulation-based. We accomplish this by considering the method of collecting performance metrics, the data representation, and the techniques used to process the data in model generation.

#### 2.2 Analytical Modeling Approaches

Analytical modeling seeks to abstract both static and dynamic characterizations of applications by parameterized expressions. It has been widely used in the high-performance computing area to predict system and application performance, provide guidelines for optimization and automatic tuning performance. Importantly, researchers can take advantage of analytical modeling to explore future directions and verify new ideas as it is able to describe theoretical systems or architectures which do not yet exist. Moreover, developers also benefit from applying analytical modeling in each phase of the software development process. Specifically, analytical modeling offers trade-off decisions, such as the CPU computing power, memory bandwidth, and network topology for setting a super-computing system during the requirement analysis, which help with system tuning for target applications in the testing period, and provide valuable feedback for maintenance. In this section, we describe several analytical modeling approaches aimed at improving application performance. In the following paragraphs, we describe manual and automatic analytical modeling, respectively.

Manual analytical modeling is a technique which does not require performance data obtained from the execution of applications. It is built by the analysis of intrinsic characteristics of the target programs, such as the problem size, the algorithm and communication pattern. In addition, the features of the platform which include architectural metrics such as latency, size of cache line, FLOPS rate, and network bandwidth for running the programs are taken into consideration. Then, the analytical model is built by analyzing the relations among all the potential factors which could impact performance.

Analytical models can be constructed through source code analysis. The understanding of the code and experience of the modeler may determine the representativeness and the accuracy of the model.

Clement and Quinn [33] introduced an analytical model for predicting the performance as speedup of parallel scientific applications running on multiple nodes. The goal of this analytical model is to provide performance information for the compiler to assist the program optimization. This modeling method started

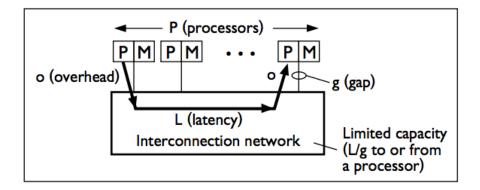

Figure 1. The LogP model. From [34]

from analysis of the previous analytical model [45, 100] for estimating the execution time of parallel applications, which uses the following expression to describe the execution time of an parallel application in general:

$$\tau(p) = T_s + \frac{T_p}{p} + \sigma(p, topology)$$

The term  $T_s + \frac{T_p}{p}$  is the ideal execution time of a parallel application. In addition to the ideal execution time, a function of processes and topology is used to represent the communication overhead related to the specific topology of the system. Clement and Quinn focused on startup cost as the major performance impact in the communication overhead, since previous research [57, 39] demonstrated that startup cost is the predominant factor in the overall cost of communication. Therefore, the cost of communication can be expressed as the number of communication times the startup cost:  $N_{comm} * C_{startup}$ . For instance, the overall communication overhead is:  $\sigma(p, topology) = N_{comm} * C_{startup} * (1 + log(p))$ for broadcasting a message on a hypercube topology. Moreover, this model also introduced memory parameter  $N_m$  and  $C_m$  for representing the number of uncached memory access and the number of necessary cycles for finishing the access operations to the uncached memory. Thus the model is able to estimate the waiting time for uncached memory accessing.

LogP [34] and the extensive work LogGP [2] are two analytical models created for describing an abstract machine configuration revealing the behavior of a shared-memory multiprocessor system. They focus on the characteristics of the interconnection network which is responsible for transmitting point-to-point messages for the communication among all the processors. Figure 1 shows the four parameters used for building the model:

- 1. *L*(*latency*): The upper bound of the communication latency/delay which happens during the message delivery from the source processor to the target processor.

- o(overhead): The overhead represents the time that a processor spends for sending or receiving the message. During this time, the processor is not able to process any other task.

- 3. g(gap): The gap indicates the minimum interval in time between two consecutive message sending or receiving for the processor.

- P(processor): The number of processor/memory modules communicating with each other by messages.

The LogP model is designed for modeling the interconnection communication by the fixed-sized short messages, and it demonstrated its capability of accurately predicting the performance of an algorithm running on the particular architecture. However, with the fast development of the hardware, many architectures (IBM SP2, Paragon, Meiko CS-2) at that time had much higher bandwidth and started supporting long messages in order to further increase the performance. In such

scenario, researchers proposed LogGP as the extension of LogP with a linear model specialized for long messages. As a consequence of adding the new component, LogGP introduced a new parameter for the model G(gap per byte), which quantifies the time each gap consumes per byte for long messages. The reciprocal of Gindicates the communication bandwidth for the long message. To validate the LogGP model, authors implemented three long-message scatter algorithms (Simple Long-Message, Binomial Tree, and optimal), and demonstrated good results, comparing prediction with measurement. With appropriate inputs, the logGP model can be used for predicting the performance of parallel algorithms and helping hardware developers explore the impact of the hardware-related parameters on the programs running on a particular architecture. The prediction result can be used to aid the optimization of the existing architecture and design future hardware.

Kerybyson et al. [69] presented an analytical model based method to guide performance and scalability analysis. The goal of this work is to create a predictive analytical model to analyze the performance and scaling behavior of an ASCI [62] application SAGE (SAIC's Adaptive Grid Eulerian Hydrocode). SAGE is a multidimensional (1D, 2D, 3D) hydrodynamics code with adaptive mesh refinement using second order accurate numerical methods. The authors created the model by studying four different aspects of SAGE: The parallel spatial decomposition, the scaling of sub-grid, the common operations in a code cycle, and adaptive mesh refinement. The authors proposed equations to represent each aspect in detail and refined the equations when more factors come into play to ensure that the model is able to reflect the behavior of the application running on the particular architecture. To build the parameterized expressions of the application, two types of data are required. The data indicates the basic metric of the machine, such as

latency, MFLOPS rate, and characteristics of the application. The analytical model showed good accuracy for the validation on large-scale architectures: IBM SP3 and SGI Origin 2000, even for future architecture with appropriate machine and application metrics as input.

# 2.2.1 Manual Analytical Modeling

Manual analytical model parameters described the hardware of a target architecture for running programs and the intrinsic features of applications, which has non-negligible impact on performance. Such parameters are frequently obtained by measurement or from system specification.

In [33], the parameterized model used to estimate application speedup  $(S(p) = T_s/T_p)$  can be expressed as:

$$T_s = (C_{compile} * (N_s + N_p) + C_m * N_m) * T_{fp}$$

$$T_p = C_{compile} * N_s + \frac{(C_{compile} * N_p + C_m * N_m) * T_{fp})}{p} + \sigma'(p, topology) * T_{fp} + C_{compile} * N_o * T_{fp}$$

The compiler factor  $C_{compiler}$  is the metric for the number of instructions generated after compiler optimization, which indicates the quality of the compiler.  $C_{compiler}$  is treated as a constant per compiler, which can be determined by benchmarking the compiler. Similarly,  $C_{startup}$  can also be treated as a machinedependent constant obtained from sampling a program.  $C_m$ , which indicates the number of cycles to access an uncached memory location, is obtained from the system specification. The rest of the parameters in the expression are all static parameters which account for the features of the application. The values of those parameters are available for the compiler by parsing the abstract syntax tree of the target program. Researchers can utilize this modeling method during compile-time for prediction-based optimization.

Kerybyson et al. [69] derived the mathematical model by understanding the four components mentioned previously and their underlying relations. Therefore, the performance-related parameters are derived from code analysis about the algorithm, the data structure, communication pattern and operations. On the other hand, the architectural hardware metrics of the machine used in the model, such as the number of the CPU cores can be obtained from the manufacture manual. The complete performance model for the SAGE code can be created by combination of the parameters from software and hardware.

In LogP [34] and LogGP [2], the authors studied the major components in distributed processing, the characteristics of messages transmission, and the nature of interconnection network as the carrier for delivering messages among processors in order to understand the roles of each part and their correlations. LogP and LogGP models simplified the message passing procedures into the parameterized expressions with only four or five machine-dependent parameters. As the author mentioned, the parameters are not equally important in all situations. Therefore, it is possible to ignore one or more parameters depending on the situation. For instance, when the overhead dominates the gap in particular machines, it is reasonable to eliminate the parameter g to simplify the model. All of the parameters used in the model can be obtained by measurement. Thus, it must re-measure the parameters in order to apply the model to evaluate different architectures.

In Tudor and Teo's paper [131, 132], they discussed their work on leveraging analytical modeling technique for analyzing the speedup of shared-memory programs running on multi-core architecture. To understand the behavior of shared-memory, authors divided the entire life span of a running program into useful work and overhead, and mainly focused on modeling issues that caused the speedup loss. The speedup model abstracts the performance loss into two parts: speedup loss due to data dependency and memory contention. Data dependency represents the number of inactive threads due to synchronizations, imbalanced workload, or lack of work to utilize all threads. To evaluate the data dependency model, the parameters are inferred by a baseline run in which it executes the program with larger number of threads than processors cores. The outnumbered threads would cause the extra threads to queue in the run-queue. By sampling the number of active threads (executing ones and those in the run-queue) in a constant time interval and the service time of the threads, the time weighted average is obtained. The memory contention model focuses on the growth of stall cycles due to memory contention considering UMA (unified memory access) and NUMA (nonunified memory access) policies respectively. The key parameter in the memory contention model, C(n) the number of cycles, is obtained by measurement. The limits in the memory model is that it only predicts the contention for the memory nodes local to active CPU nodes.

#### 2.2.2 Automatic Analytical Modeling

Manual analytical modeling requires analysis of the application and the interaction with hardware, resulting in a heavy burden of time and human efforts.

1 ! def n\_px =  $\{npe_i\}$ 2 | and  $n_pointx =$   $n_pointx_gbl / n_px$ 3 **!\$pal** def n\_py, n\_pointy... 4 ! def sweep3d\_mdl(g, p, s) = n\_solve \* (sweep3d(g, p) + s) 5 ! def sweep3d(g, p) = p\_fill(g, p) + n\_octant \* p\_octant(g, p) + p\_drain(g, p) 6 ! def p\_octant $(g, p) = (n_sweep - 1) * p_stage(g, p)$ 7 ! def p\_stage(q, p) = (q + (4 \* p)) 8 **!\$pal** def p\_fill(g, p) = (n\_px + n\_py - 1) \* (g + 2 \* p) 9 !\$pal def p\_drain(g, p) = (2 \* n\_px + 4 \* n\_py - 2) \* (g + 2 \* p) 10  $|\text{pal loop } n_{solve} = \dots |$  hide actual  $n_{solve} |$  loop 11 !**\$pal model** sweep =  $p_fill(@{grind}, @{post1}) + @{sweep} + \$  $p_drain(@{grind}, @{post1})$ 1213 call sweep(...) ! sweep() is the right column 14 **!\$pal** endmodel 15 **!\$pal** endloop

*Figure 2.* Program annotation used in Palm framework [126].

To alleviate the burden, several researchers made efforts to automate the modeling procedure through static program analysis.

Narayanan et al. proposed PBound [102], a framework for automatically estimating best case performance bounds of C/C++ applications through static compiler analysis. PBound collects information and generates parameterized expressions for memory and floating-point operations combined with user-provided architectural information to compute machine-specific performance estimates. PBound solely relies on source code analysis, and ignores the effects of compiler transformation, frequently resulting in bound estimates that are not realistically achievable.

Kerncraft, created by Hammer et al., is a static performance modeling tool with the concentration on memory hierarchy. Kerncraft characterizes performance and scaling loop behavior based on Roofline [139] or Execution-Cache-Memory (ECM) [61] model. It uses Intel Architecture Code Analyzer (IACA) [63] to operate on binaries in order to gather loop-relevant information. However, the reliance

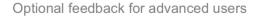

Figure 3. Workflow of the COMPASS framework. From [79]

on IACA limits the applicability of the tool. As a result, the binary analysis is restricted by Intel architecture and compiler.

ExaSAT [30, 133] automates the procedure of performance model generation by employing static code analysis. ExaSAT is built on top of ROSE compiler framework [112] to generate AST (abstract syntax tree) which is consumed by the compiler analysis component to produce loop attributes, and analyze data access. The compiler analysis outputs an XML format intermediate representation which enables the framework to model the hypothetical code by the given XML-IR. However, ExaSAT uses an ideal model to simplify the memory hierarchy and the analysis only works for specific source code pattern (loop type).

To reduce the difficulty of analytical performance modeling, Palm [126] leverages static code analysis to build performance models in Ruby automatically. The resulting model can be evaluated by providing various values. However, it is not a fully automatic framework since it requires users to annotate in order to describe the application (Figure 2). The source code annotation can be a timeconsuming task and demands the users to understand the code. Moreover, the model parameters are obtained by measurement from running the instrumented code on specific architectures. Figure 3 presents the COMPASS [79] framework, which shares the similar design ideas of performing the static code analysis to generate performance model. OpenARC [80] is used to examine the source code, including interpretation of the OpenMP and OpenACC directives to identify parallelism. The Aspen IR processor accepts the output of OpenARC to generate the Aspen performance model [122]. Comparing to Palm, COMPASS achieves better automation by using light-weight annotation and the static data enables it to be able to apply to considerably arbitrary code.

#### 2.2.3 Advantages and Disadvantages

Analytical modeling techniques do not rely on performance data from execution to generate models. It summarizes the features of the applications, such as data structure, data distribution, data dependence, and considers static performance-related metrics of hardware such as the cost for message passing, memory access, initialization overhead, CPU cycle. In addition, it abstracts the behavior of the software and the interaction between the software and hardware. The software/hardware metrics are combined, which generates parameterized expressions for performance prediction or diagnosis.

Since analytical modeling requires no performance data from the multiple runs of the target program, it avoids the time-consuming work of designing the inputs, configuring the experiment environment and waiting for performance data, which could take a long time. The properties of analytical modeling enables integration in a compiler as a plugin for guiding optimization. If an analytical model consists of the parameters which compiler is able to obtain statically, then

the parameters can be used by the compiler during the compilation of a program to predict the performance and provide feedback to compiler so it can decide the optimization type and targets while maintaining a reasonable compilation time. In addition to the time efficiency, analytical modeling is applicable in every phase of software/hardware development because it is data-independent. Analytical models can help make decisions in design, implementation, and testing. Moreover, comparing with other modeling methods, analytical modeling is more resilient to the changes of the application. Researchers can adjust the parameters and the logical relations regarding the changes in a timely manner, which improves the efficiency of performance evaluation and optimization significantly.

However, to model an application and its underlying communication behavior with the lower-level hardware, one needs expertise in order to obtain a deeper understanding about algorithms used in the application, as well as the technical details of the target architecture. For example, in order to model an application using message passing for communicating among the distributedmemory, it is required to understand the mechanism of message passing, the involved hardware, data organization and partition at a higher-level. The user needs to identify which factors may affect the performance and in what manner, so that they can be correctly placed in the parameterized expression. Furthermore, building the analytical model also involves making trade-off between the model accuracy and the number of model parameters. A great number of parameters indicate that the model considers more factors that will impact the performance, leading to a more accurate result. On the other hand, a model containing fewer parameters at a higher abstract level provides less comprehensive results yet is easier to build. Therefore, the analytical model should be designed carefully to

make the balance between complexity of model construction and accuracy of the results. In general, the simple analytical model is suitable for the fast study of an algorithm while a more sophisticated model satisfies the need of deep optimization and tuning of an application.

Although static code analysis based methods automate the analytical modeling to some extent, it may still require human efforts for manually processing the worst case entire source code. This constraint worsens the cost of modeling for complex and large-scale applications.

### 2.3 Empirical Modeling Approaches

Empirical modeling methods rely on the performance data from actual execution of programs on the target architecture. Therefore, the procedure of empirical modeling can be divided into two phases. First, the program is executed on the target platform to generate performance metrics. The data for characterizing the dynamic behavior of the program is then processed. In this section, we will discuss the empirical modeling approaches according to the two phases: data collection and model generation.

## 2.3.1 Performance Data Collection

To study the performance of an application, the first step in empirical methods is to run the target program on a particular platform and obtain the data so that we can learn what is happening at runtime. Performance data collection is defined as the methods used to extract necessary performance information. If we consider an execution of the program as a series of various types of events occurring at certain point of time, the goal is to obtain the insight about such events, such

as time, duration, and interactions. In the following section, we describe two major techniques for data collection.

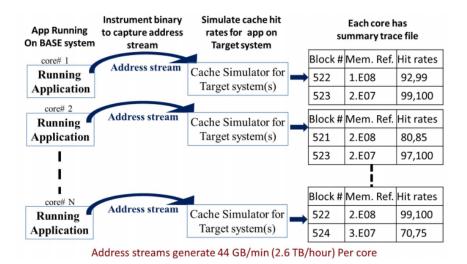

1) Code instrumentation. The target executable used for generating data is expected to provide more information for each run given the fact that it could be costly, especially on supercomputers. Most importantly, the unmodified program is only able to provide coarse-grained information such as the execution time or results. Extracting lower-level data about the underlying hardware, such as instruction count, to study the performance is necessary to understand application behavior. Code instrumentation provides an opportunity to probe the application during runtime. Instrumentation modifies the source code by inserting annotations at interesting spots such as the entry/exit point of a function, inside a loop, or around branch statement. When the modified program is executed at the annotation points, the additional function calls are triggered to record the events and related metrics, such as how many time this block has been visited and how long a loop takes to complete.

However, considering the scenario that source code may not be accessible, one can perform runtime instrumentation on the binary executable to modify the binary using dynamic instrumentation tools [121, 85, 20, 103] or performance analysis tools [117, 1] which includes a binary component. Importantly binary instrumentation separates the target program from the platform, offering an opportunity for understanding the code in an architecture-independent manner. Information in the DWARF section helps map binary code back to the source so that users could locate the blocks or the particular functions. However, the compiler optimization would complicate binary instrumentation and makes the implementation of that more challenging.

In addition, there are several tools [101, 134, 46] provided runtime librarylevel instrumentation other than application-level. Such tools are implemented as libraries between the application and the runtime library. They employ the standard profiling interfaces (PMPI, OMPI) to intercept and record the events and forwards them to the runtime library. Applications are required only to re-link with the instrumentation library.

2) Performance hardware counter sampling. Code instrumentation is able to provide detailed dynamic information about an application. Yet code instrumentation is intrusive and time-consuming. Sampling tools, for example [19], offer an alternative for collecting the performance data without modification of the code. They rely on hardware performance counters which are a part of modern processor performance monitoring units. The performance counters work as a set of registers to record the occurrences of specific signals. When a given interval is reached or the counters overflow, the sampling tool interrupts the running application in order to collect the addresses of the events. It is able to provide information at a fine level of detail, such as operation count, cache misses, pipeline stall. Sampling provides the users with flexibility to make trade-offs between overhead and resolution of the events. By reducing the length of the observation interval, more details about an event can be inferred yet with higher overhead. On the contrary, sampling at a low rate by increasing the number of observation intervals may lead to overlook infrequent events.

Before applying the performance analysis tool, the collected instrumented and sampled data need to be processed to generate either a profile or event trace [96] for data analysis. In a profile, measured events are aggregated together which represents a mapping from events to source code at the statement, loop,

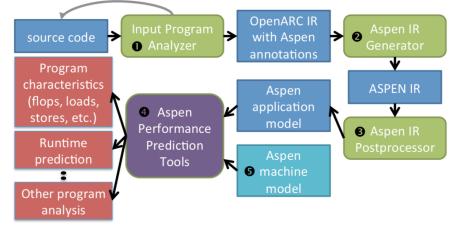

Figure 4. A fully connected feed-forward ANN. From [65]

or function-level. A callpath profile [52], which contains information about the costs and function calling context, is frequently used in performance analysis tools [117, 1, 71]. Traces comprise time-stamped events, which is able to provide more detailed information about the application behavior and suitable for examination of timing-related issues in the program. A profile can be reconstructed from a trace, however constructing a trace from a profile is difficult since sampling may miss events occurring outside of samples. However, the size of tracing data increases with the runtime. Thus, tracing-based analysis may take a large amount of storage.

#### 2.3.2 Model Generation

Once performance data is obtained, the correlations between the input parameters need to be understood. In the follow paragraphs we will cover the approaches for building models.

1) Artificial neural networks. An artificial neural network (ANN) is a machine-learning technique for discovering the correlations between input parameters and results. An ANN comprises a set of nodes and weighted edges connecting the nodes. A node representing a neuron is called a unit in ANN that communicates with other connected nodes by receiving and passing values. There are three types of units in an ANN architecture located in distinct layers along the information flow. Input units are responsible for accepting the input and passing the weights to according units pointed by the outgoing edges. The output unit receives the value and presents the prediction results. Among all the units, the hidden units are of great importance as they carry all the computation tasks, which receive input from incoming edges to process the new output and then passes to either hidden units or output unit. Specifically, after a new training sample is accepted and distributed by the input layer, every hidden unit takes the sum of all values from the previous layer and the weights on the incoming edges, and computes the new sum by the activation function as its output is passed to next layer. Figure 4 demonstrates a fully connected feed-forward neutral network with only one hidden layer in which each unit is connected by every unit in the previous layer. The data flows from the bottom to the top.

In [65] authors employ fully connected feed-forward neural network to build the model in order to predict the program performance. In the feed-forward ANN (as shown in figure 4) the *sigmoid* function is used as the activation function to

Figure 5. The workflow for parallelism mapping. From [137]

calculate the new output on each hidden unit. By monopolistic executions to reduce the noise in the generate performance data and the applying the appropriate sampling technique and learning mechanism to minimize the percentage error during training, the neural network achieved 5%-7% error on performance prediction of SMG2000 [43].

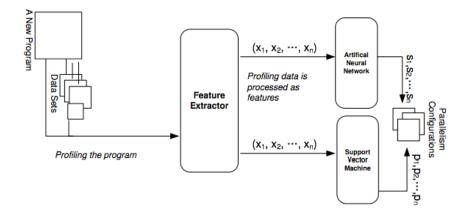

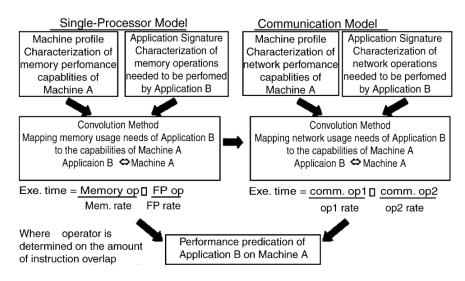

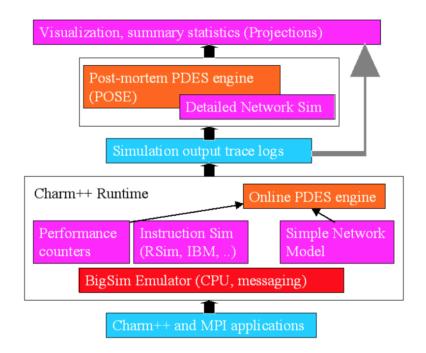

Li et al. [81] proposed ASpR framework for predicting the performance of runtime parallelization and task scheduling. The Stuttgart Neural Network Simulator [144] is used to build the neural network and make predictions. As an on-line system, ASpR continuously collects runtime information to generate training data including function name, parameter sizes, and measured execution time. In the implementation, authors used a two-hidden-unit (single hidden layer) neural network with sigmoid function as the activation function and update the edge weights by back-propagation algorithm. In addition, to adapt the continuous new available data points, it limits the training data in a sliding window range with reasonable size. And ASpR incrementally retrains the ANN with data from the growing sliding window to improve the prediction accuracy. Figure 5 presents Wang and O'Boyle's research [137] in which they adopt ANN to build model for predicting the performance of a mapping of program parallelism to multi-core processors to guide the selection of the best thread number for a parallel program. In the proposed approach, the authors profile the instrumented serial version of the program and compiler-parallelized version respectively to obtain code features and runtime feature. Code features covers the characteristics of the target program including cycles per instruction, the number of branches, load and store operations, while the runtime feature mainly refers to the parallel execution time. An ANN with 2 hidden layers (each has 3 hidden units) using Bayesian regularization back-propagation as the training algorithm is constructed to predict the speedup. Moreover, authors use a multi-class support vector machine (SVM) to predict the best scheduling policy with different number of threads. The combined results can reveal the correlation between program scalability and the number of threads.

2) Regression. In [67], Joseph et al. proposed a method for processor performance analysis based on the linear regression model. The goal of the research is to model the relationship between processor performance and architectural parameters. In the development of their model, they assumed no prior knowledge and understanding about the architecture and the workflow of the processor. Their modeling technique quantifies the significance of architecture-related parameters and the interaction among them. To identify the performance impact of the parameters, they adjusted the value of a parameter, then monitored the performance changes in the simulation results. For example, the measured average instruction issued per cycle can demonstrate the changes in out-of-order issue would cause more performance loss than an in-order issue in terms of performance effect

on the L1 data cache. The authors used 26 key micro-architectural parameters, such as pipeline depth, issue queue size, L2 cache size and issue order, to construct the model. To obtain the best model, the authors performed an iterative procedure to refine the initial model, which starts from a small set of execution results, and then apply the model to guide further data until it reaches the designed error bounds. The model is constructed by following Akaike's Information Criteria [116] to fit the data while maintaining a minimum number of parameters. However Harrell [54] stated in his research that such stepwise regression has several significant biases, which motivates researchers to apply other regression methods statistical modeling.

Lee et al. [78] presented several methods for exploring the parameter domain of larger applications and building predictive models. In this research, the authors demonstrated the effectiveness of applying statistical methods for studying the relationship between the parameters and the performance impact. Hierarchical clustering provides information about the correlations of the parameters. Clustering also filters the redundant predictors for regression model by selecting the most representative predictor that could reflect the cluster's impact on the result if multiple predictors are correlated and clustered into the same group. Association analysis and correlation analysis are used for investigating and quantifying the association between the predictors and the response. It provides the researchers a high-level perspective to understand the parameter domain. The authors compared the prediction between a piece-wise polynomial regression model and the artificial neutral network, and offered suggestions for the selection of the two method. The performance data for building the model is obtained by sampling the performance measurement. To reduce the high costs of exhaustive measurement,

authors applied several sampling technique to data collecting. Sampling Uniform at Random (UAR) approach has a full range of parameter values and could ensure the sampled data unbiased and representative for the parameter domain. Stratification minimizes the divergence in relative error for the small performance value with large relative but small absolute errors. It mitigates the bias of the sample data caused by the optimization to reduce the sum of square errors in regression and neutral networks. Regional sampling combined with regression generates per-query regression model according to the similarity (Euclidean distance) of the points to the query.

In Lee's other researches [76, 77], they utilized the same data analysis techniques for the exploration of the correlations among parameters in a larger design space of one billion points for performing the polynomial regression modeling accurately and efficiently for predicting the performance and power. Turandot [98], a parametric, out-of-order, super-scalar processor simulation framework is used to obtain power estimates. Turandot is able to accurately estimates the power consumption by the circuit-level power analysis and resource utilization statistics [18]. Similarly, they applied sampling uniformly at random to collect the number of data points needed for constructing the model in order to reduce the expensive experiment runs.

Barnes et al. [7] described a regression-based modeling method for performance prediction. The modeling technique [7] predicts the execution time of an application on p processors by the execution time collected for the same application running on the architecture with a smaller number (q) of processors, where  $q \in \{2, ..., p_0\}$  and  $p_0 < p$ . Instrumentation is used for collecting the execution time of an application. Specifically, it varies the configuration of the inputs and

then applies them to the instrumented code to obtain the data for multiple runs. With the performance data, the method then performs a regression to fit the data into a linear prediction model. Three techniques are demonstrated in their work for prediction. The most straightforward one is to simply fit the data from execution by regression and then extrapolate to a larger problem size. It results in a reasonable prediction with a second-order polynomial function for fitting. The second technique separates the regressions of computation and communication by selecting the most representative pair from the per-processor data. The third method constrains the communication time to include no blocking using the global critical path.

Both neural network and regression can provide reasonable accuracy. Regression-based methods offer a statistical perspective on the parameter space. In the above research, authors statistically analyze parameters to explore the correlation among them and such analyses also help to identify the significance of the parameters that contributing majorly to the performance. On the contrary, the neural network presented in previous paragraph did not demonstrate the feature selection of the input data, which may result redundancy in the generated model. However, neural network based approaches achieve better automation than the regression based ones. Users could choose depending on their requirement.

# 2.3.3 Advantages and Disadvantages