## LA-UR-22-22497

## Approved for public release; distribution is unlimited.

Title: Empirical Performance Analysis of HPC Applications with Portable

Hardware Counter Metrics

Author(s): Gravelle, Brian Joseph

**Intended for:** Dissertation for University of Oregon

**Issued:** 2022-05-13 (rev.4)

Los Alamos National Laboratory, an affirmative action/equal opportunity employer, is operated by Triad National Security, LLC for the National Nuclear Security Administration of U.S. Department of Energy under contract 89233218CNA000001. By approving this article, the publisher recognizes that the U.S. Government retains nonexclusive, royalty-free license to publish or reproduce the published form of this contribution, or to allow others to do so, for U.S. Government purposes. Los Alamos National Laboratory requests that the publisher dientify this article as work performed under the auspices of the U.S. Department of Energy. Los Alamos National Laboratory strongly supports academic freedom and a researcher's right to publish; as an institution, however, the Laboratory does not endorse the viewpoint of a publication or guarantee its technical correctness.

# EMPIRICAL PERFORMANCE ANALYSIS OF HPC APPLICATIONS WITH PORTABLE HARDWARE COUNTER METRICS

by

#### BRIAN J GRAVELLE

#### A DISSERTATION

Presented to the Department of Computer and Information Sciences and the Division of Graduate Studies of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

May 2022

#### DISSERTATION APPROVAL PAGE

Student: Brian J Gravelle

Title: Empirical Performance Analysis of HPC Applications with Portable

Hardware Counter Metrics

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Sciences by:

Boyana Norris Chair

Allen Malony Core Member Hank Childs Core Member

Diego Melgar Institutional Representative

and

Krista Chronister Interim Vice Provost for Graduate Studies

Original approval signatures are on file with the University of Oregon Division of Graduate Studies.

Degree awarded May 2022

© 2022 Brian J Gravelle All rights reserved.

#### DISSERTATION ABSTRACT

Brian J Gravelle

Doctor of Philosophy

Department of Computer and Information Sciences

May 2022

Title: Empirical Performance Analysis of HPC Applications with Portable Hardware Counter Metrics

In this dissertation, we demonstrate that it is possible to develop methods of empirical hardware-counter-based performance analysis for scientific applications running on diverse types of CPUs. Although hardware counters have been used in performance analysis for at least 30 years, the methods used are still limited to particular CPU vendors or even particular generations of CPUs from the same vendor. Our motivating hypothesis is that hardware counter-based measurements could be developed to provide consistent performance information on diverse CPU types. This dissertation proves the hypothesis was correct by demonstrating one such set of metrics.

We begin with an introduction motivating empirical performance analysis on CPUs, followed by a background on empirical performance analysis. This background includes the Roofline Performance Model which is widely used to visualize the performance of scientific applications relative to the potential performance of the system in use. The Roofline Model uses metrics that are easily portable to different CPU architectures, so it is a useful starting point for our efforts to develop portable hardware counter metrics. We contribute to existing roofline literature by presenting a method using hardware counters to measure the

required application data on two different CPUs and by presenting two benchmarks to produce the Roofline Model of the CPU. These contributions are complementary since the benchmarks can also be used to validate the hardware counters used to measure the application data.

Building on this work, we present a set of additional performance metrics derived from Hardware Performance Monitors that we have been able to replicate on CPUs from two separate vendors. We developed these metrics to focus on information that can inform developers about the performance of the algorithms and data structures in their applications. This method contrasts with other hardware counter methods which are aimed at particular microarchitectural features. These metrics allow the users to understand the performance of the application from the same perspective on multiple CPUs.

We use a series of case studies to explore the usefulness of our new metrics and to validate that the measured values provide the expected information about the application on both of our test systems. The first set of case studies examines a series of benchmarks and mini-applications. These computational kernels have a variety of performance features which we explore using the new hardware counter metrics. Finally, we study the performance of several versions of a scientific application using a combination of the Roofline model and the new metrics. These case studies show that our performance metrics are able to provide useful performance information on two different CPU types, proving our hypothesis by example.

This dissertation includes material that has been published previously with coauthors.

#### CURRICULUM VITAE

NAME OF AUTHOR: Brian J Gravelle

#### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene, OR, USA Gonzaga University, Spokane, WA, USA

#### **DEGREES AWARDED:**

Doctor of Philosophy, Computer Science, 2022, University of Oregon Bachelor of Science, Computer Engineering, 2015, Gonzaga University

#### AREAS OF SPECIAL INTEREST:

High Performance Computing Performance Analysis Computer Architecture

#### PROFESSIONAL EXPERIENCE:

Graduate Employee (Research), Dept. of Computer and Information Science, University of Oregon, 2017-2022 Graduate Employee (Instructor of Record for Computer Architecture), Dept. of Computer and Information Science, University of Oregon, Spring 2021 Graduate Employee (Teaching Assistant for undergraduate courses), Dept. of Computer and Information Science, University of Oregon, 2015-2017

Graduate Research Assistant, Los Alamos National Laboratory, 2018-2022

Undergraduate Research Assistant, Gonzaga University, 2013-2015

#### GRANTS, AWARDS AND HONORS:

Moursund Graduate Teaching Award, University of Oregon, 2021

#### PUBLICATIONS:

- Gravelle, B. J., & Nystrom, W. D., Yokelson, D., & Norris, B. (2021). Enabling cache-aware roofline analysis with portable hardware counter metrics. *International Workshop on Performance Modeling, Benchmarking and Simulation of High Performance Computer Systems*. Springer.

- Graziano, V., & Nystrom, W. D., & Pritchard, H., & Smith, B., & Gravelle, B. J. (2021). Optimizing a 3d multi-physics continuum mechanics code for the hpe apollo 80 system. *Cray User Group (CUG)*.

- Gravelle, B. J., & Norris, B. (2019). Performance Analysis of Compressed Batch Matrix Operations on Small Matrices. The 6th Special Session on High Performance Computing Benchmarking and Optimization.

- Gravelle, B. (2019). "Understanding the Performance of HPC Applications." Technical Report for Departmental Area Exam.

- Gravelle, B. (2017). "Performance and Power Impacts of Autotuning of Kalman Filters for Disparate Environments." Technical Report for Departmental Directed Research Project.

#### ACKNOWLEDGEMENTS

I would like to begin by thanking those organizations that financially supported the research presented in this dissertation. This work was supported by the U.S. Department of Energy through the Los Alamos National Laboratory (LANL). Los Alamos National Laboratory is operated by Triad National Security, LLC, for the National Nuclear Security Administration of U.S. Department of Energy (Contract No. 89233218CNA000001). The work would have been impossible without the Darwin testbed at LANL which is funded by the Computational Systems and Software Environments subprogram of LANL's Advanced Simulation and Computing program (NNSA/DOE). Additional support came from the U.S. National Science Foundation, under grants PHY1520969, PHY1521042, PHY1520942 and PHY1624356, and under Cooperative Agreement OAC1836650, and by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research, Scientific Discovery through Advanced Computing (SciDAC) program.

While completing this research I worked primarily in Los Alamos, New Mexico and Eugene, Oregon. The following statements from LANL and the University of Oregon, respectively, recognize the importance of the land to the indigenous populations.

LANL and the communities of Los Alamos and White Rock are located on Indigenous lands, ancestral to the Tanoan and Keresan speaking peoples of northern New Mexico. This landscape, being located in an area of migration and trade along the Rio Grande and Jemez Mountains, also retains ancestral significance to Athabaskan speaking peoples – including the Dinétah and Apache

– the Zuni and the Hopi. We value, respect and honor the traditional peoples and landscapes which comprise the Laboratory, and recognize the multi-generational support that Native American peoples and communities have provided to LANL and the Department of Energy complex across the United States. Our directive is to be responsible stewards of this landscape; to practice environmental responsibility to meet the legal and ethical requirements needed for long-term preservation of these indigenous lands.

The University of Oregon is located on Kalapuya Ilihi, the traditional indigenous homeland of the Kalapuya people. Following treaties between 1851 and 1855, Kalapuya people were dispossessed of their indigenous homeland by the United States government and forcibly removed to the Coast Reservation in Western Oregon. Today, descendants are citizens of the Confederated Tribes of Grand Ronde Community of Oregon and the Confederated Tribes of Siletz Indians of Oregon, and continue to make important contributions in their communities, at UO, and across the land we now refer to as Oregon.

Throughout my time as a graduate student, Boyana Norris has advised, guided, and occasionally cajoled me into completing my research. Her technical and personal advice helped me through the more difficult periods, while her persistent joy and curiosity have been a source of inspiration. I have no doubt that the successes of this dissertation are primarily due to her guiding hand and its limitations due to my obstinacy.

Similarly, Dave Nystrom and been an invaluable mentor in matters of my career and in my research. I have attempted to follow his example of dedication and patience, and I hope that eventually I can pass some of his wisdom to other interns.

At both UO and LANL, I had many colleagues who supported this work. Sam Pollard, Ph.D., Kewen Meng, Ph.D., and Curtis Dlouhy, Ph.D. were colleague and friends throughout my time in Oregon. Cindy Martin, Andrew Montoya, Julie Wiens, Howard Pritchard, and numerous others made my time at LANL enjoyable and productive.

Finally I would like to thank my family for their love and support. They are a constant source of inspiration and encouragement.

Dedicated to Denise and Delia in gratitude for their utmost patience....

## TABLE OF CONTENTS

| Cl  | napter | Pag                                                  | e, |

|-----|--------|------------------------------------------------------|----|

| I.  | INTI   | RODUCTION                                            | 1  |

| II. | BAC    | KGROUND                                              | 6  |

|     | 2.1.   | Performance Measurement and Analysis of Applications | 8  |

|     | 2.2.   | Arithmetic Intensity and the Roofline Model          | 0  |

|     |        | 2.2.1. Arithmetic Intensity and Data Movement        | 1  |

|     |        | 2.2.2. Roofline variations                           | 4  |

|     | 2.3.   | Wrapping up the background                           | 6  |

| III | І.МЕТ  | HODOLOGY                                             | 7  |

|     | 3.1.   | Systems                                              | 7  |

|     | 3.2.   | Tools                                                | 8  |

|     | 3.3.   | Benchmarks                                           | 9  |

|     |        | 3.3.1. STREAM                                        | 9  |

|     |        | 3.3.2. FP Crunch                                     | 0  |

|     |        | 3.3.3. Cache Conflict Measurement                    | 1  |

|     |        | 3.3.4. Matrix Multiplication                         | 2  |

|     |        | 3.3.5. N-Body Simulation                             | 6  |

|     | 3.4.   | Summary                                              | 8  |

|     |        | IRICAL ROOFLINES WITH HARDWARE                       |    |

|     | COU    | NTERS                                                | 9  |

|     | 4.1.   | Architectural Rooflines                              | 0  |

|     |        | 4.1.1. STREAM Modification                           | 1  |

|     |        | 4.1.2. FP Crunch                                     | 8  |

|     | 4.2.   | Application Points                                   | 0  |

| Chapter | r             |                                                                      | Page |

|---------|---------------|----------------------------------------------------------------------|------|

|         | 4.2.1.        | Measuring Time                                                       | . 41 |

|         | 4.2.2.        | Measuring Data Movement                                              | . 41 |

|         | 4.2.3.        | Measuring Floating Point Operations                                  | . 45 |

| 4.3.    | Exam          | ples                                                                 | . 48 |

|         | 4.3.1.        | N Body Example                                                       | . 48 |

|         | 4.3.2.        | Matrix Multiplication Example                                        | . 50 |

| 4.4.    | Summ          | nary                                                                 | . 52 |

|         | ROPOS<br>RICS | SED SET OF HARDWARE COUNTER                                          | . 54 |

| 5.1.    | Defini        | ng Metrics                                                           | . 55 |

| 5.2.    | Measu         | uring the Metrics                                                    | . 55 |

|         | 5.2.1.        | Counter Collection and Analysis for Data<br>Movement Metircs         | . 57 |

|         | 5.2.2.        | Counter Collection and Analysis for Computation Metrics .            | . 60 |

|         | 5.2.3.        | Counter Collection and Analysis for Computation<br>Data Rate Metrics | . 63 |

| 5.3.    | Detail        | ed Metric Discussion                                                 | . 63 |

|         | 5.3.1.        | Overall Performance                                                  | . 63 |

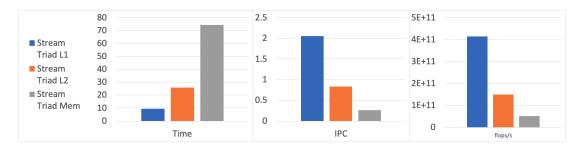

|         |               | 5.3.1.1. Demonstration with STREAM                                   | . 64 |

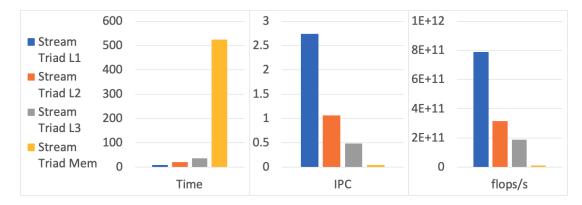

|         |               | 5.3.1.2. Demonstration with Matrix Multiplication                    | . 66 |

|         | 5.3.2.        | Data Movement                                                        | . 67 |

|         |               | 5.3.2.1. Demonstration with STREAM data                              | . 69 |

|         |               | 5.3.2.2. Demonstration with Loop Blocking                            | . 70 |

|         |               | 5.3.2.3. Demonstration with Cache Conflicts                          | . 73 |

|         | 5.3.3.        | Cache Efficiency                                                     | . 75 |

|         |               | 5.3.3.1. Demonstration with Cache Conflicts                          | . 77 |

| Chapter     | •      |           |              |          |       |       |       |      |      |   |   |   |   | F | Page |

|-------------|--------|-----------|--------------|----------|-------|-------|-------|------|------|---|---|---|---|---|------|

|             |        | 5.3.3.2.  | Demonstrat   | ion with | ı Loo | p Blo | ockin | g    |      |   |   |   |   |   | 79   |

|             | 5.3.4. | Computa   | ation        |          |       |       |       |      |      |   |   | • |   |   | 84   |

|             |        | 5.3.4.1.  | Demonstrat   | ion with | ı STI | REAI  | М.    | •    |      |   |   |   |   |   | 86   |

|             |        | 5.3.4.2.  | Demonstrat   | ion with | n Mat | rix l | Aulti | plic | atic | n |   |   |   |   | 86   |

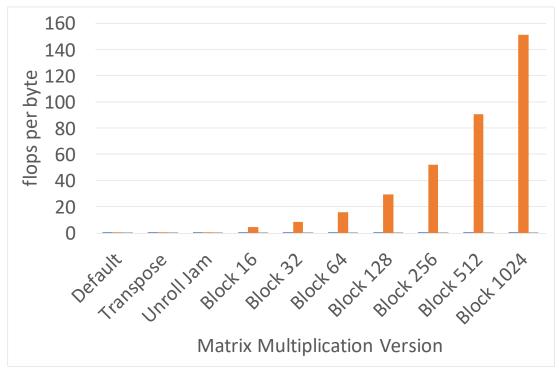

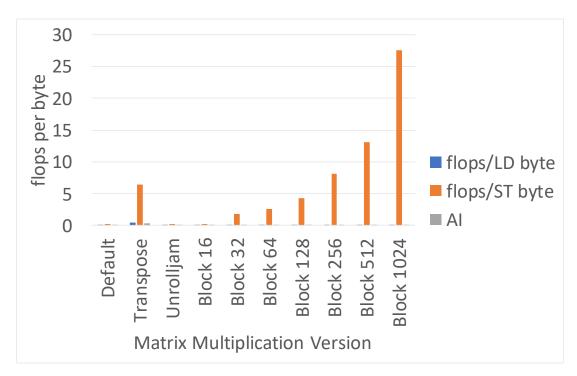

|             | 5.3.5. | Computa   | ation Data R | lates .  |       |       |       | •    |      |   |   |   |   |   | 90   |

|             |        | 5.3.5.1.  | Demonstrat   | ion with | n STF | REAI  | М.    |      |      |   |   |   |   |   | 92   |

|             |        | 5.3.5.2.  | Demonstrat   | ion with | n Mat | rix l | Aulti | plic | atic | n |   |   |   |   | 92   |

| 5.4.        | Summa  | ary       |              |          |       |       |       |      |      |   |   | • |   |   | 96   |

|             |        |           | MINI-APPL    | -        |       | ~~T   |       |      |      |   |   |   |   |   |      |

| PERI<br>MET |        |           | ING THE H    |          |       |       |       |      |      |   |   |   |   |   | 102  |

| 6.1.        | Kernel | Example   | s            |          |       |       |       |      |      |   |   |   |   |   | 102  |

|             | 6.1.1. | N-Body    | Simulation   |          |       |       |       |      |      |   |   |   |   |   | 102  |

|             | 6.1.2. | XSBench   | 1            |          |       |       |       |      |      |   |   |   |   |   | 106  |

|             | 6.1.3. | Cloverlea | af           |          |       |       |       |      |      |   |   |   |   |   | 109  |

|             | 6.1.4. | PENNA     | NT           |          |       |       |       |      |      |   |   |   |   |   | 112  |

|             | 6.1.5. | VPIC .    |              |          |       |       |       |      |      | • | • |   |   |   | 114  |

| 6.2.        | Summa  | ary       |              |          |       |       |       |      |      |   |   |   |   |   | 118  |

| VIIA CA     | ASE ST |           | THE PAGE     |          |       |       |       |      |      |   |   |   |   |   |      |

|             | LICATI |           |              |          |       |       |       |      |      |   |   |   |   |   |      |

|             |        |           | ion          |          |       |       |       |      |      |   |   |   |   |   |      |

| 7.2.        |        |           |              |          |       |       |       |      |      |   |   |   |   |   |      |

|             | 7.2.1. | Versions  |              |          |       |       |       |      |      | • | • |   | • |   | 121  |

|             |        |           |              |          |       |       |       |      |      |   |   |   |   |   |      |

|             | 7.2.3. | Takeawa   | ys           |          |       |       |       | •    |      | • |   | • | • |   | 128  |

| 7.3.        | Streng | th 1 and  | Strength 2   |          |       |       |       |      |      |   |   |   |   |   | 131  |

| Chapter | •      |          |     |   |      |  |   |  |  |  |  |  |  |  | j | age |

|---------|--------|----------|-----|---|------|--|---|--|--|--|--|--|--|--|---|-----|

|         | 7.3.1. | Versions |     |   | <br> |  |   |  |  |  |  |  |  |  |   | 131 |

|         | 7.3.2. | Results  |     |   | <br> |  |   |  |  |  |  |  |  |  |   | 132 |

|         | 7.3.3. | Take Aw  | ays | • | <br> |  | • |  |  |  |  |  |  |  |   | 138 |

| 7.4.    | Summ   | ary      |     | • | <br> |  | • |  |  |  |  |  |  |  |   | 143 |

| VIICON  | ICLUSI | ON       |     |   |      |  | • |  |  |  |  |  |  |  |   | 144 |

| REFER   | ENCES  | SCITED   |     |   |      |  |   |  |  |  |  |  |  |  |   | 148 |

## LIST OF FIGURES

| Figu | ure                                                                                                                  | Page |

|------|----------------------------------------------------------------------------------------------------------------------|------|

| 1.   | Comparison between the basic Von Neumann architecture and a more modern model with multiple levels of memory caching | 11   |

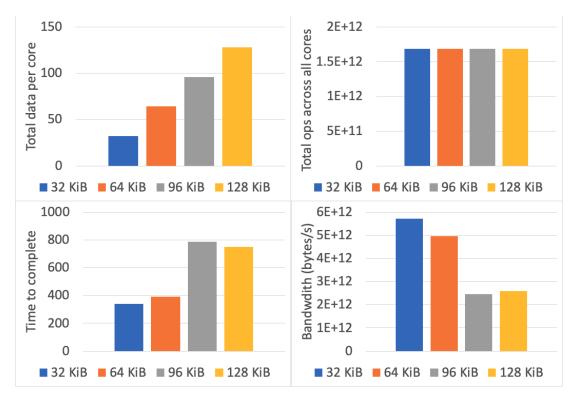

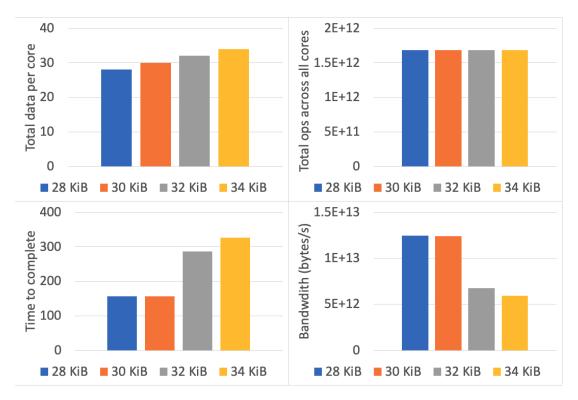

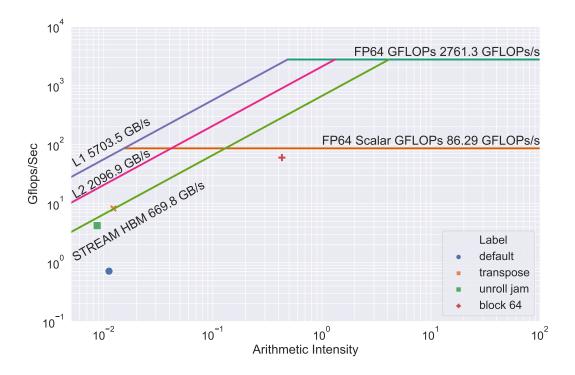

| 2.   | Results running the modified STREAM benchmark on the A64FX $$                                                        | 33   |

| 3.   | Results running the modified STREAM benchmark on the Cascade Lake                                                    | 35   |

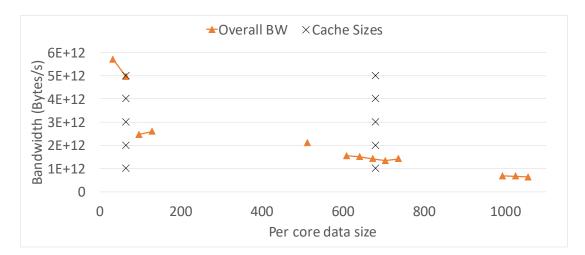

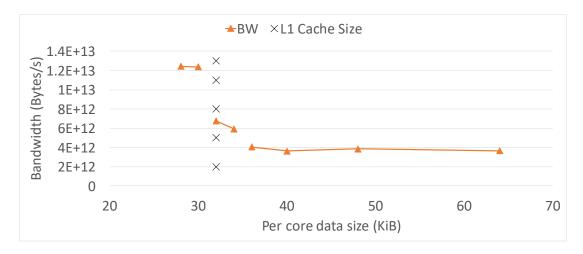

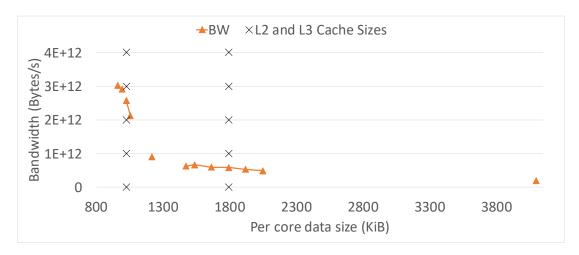

| 4.   | STREAM Bandwidth relative to per core data size on the A64FX $$                                                      | 36   |

| 5.   | STREAM bandwidth relative to per core data size on the Cascade Lake                                                  | 36   |

| 6.   | STREAM Bandwidth relative to per core data size on the Cascade Lake                                                  | 37   |

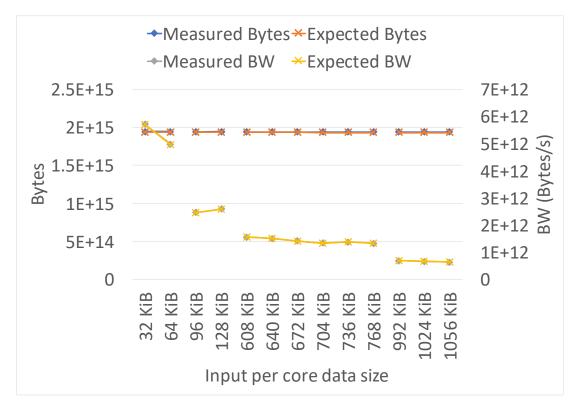

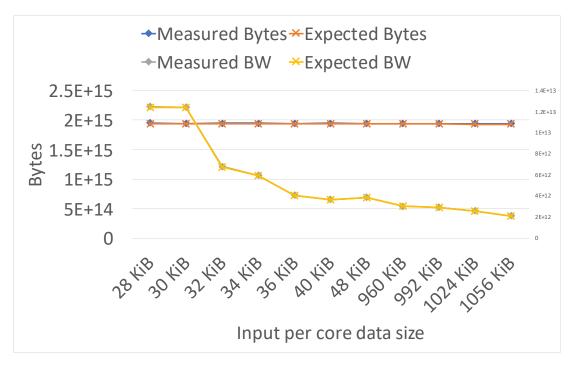

| 7.   | Comparison of the bytes moved and bandwidth on the A64FX                                                             | 45   |

| 8.   | Comparison of the bytes moved and bandwidth on the Cascade Lake                                                      | 46   |

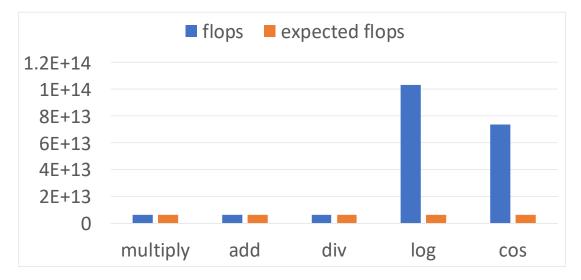

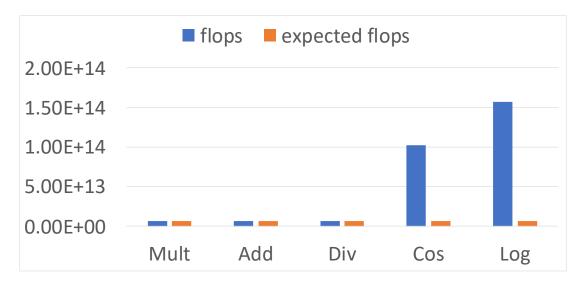

| 9.   | Comparison of expected and measured <b>flops</b> on A64FX                                                            | 48   |

| 10.  | Comparison of expected and measured <b>flops</b> on Cascade Lake                                                     | 49   |

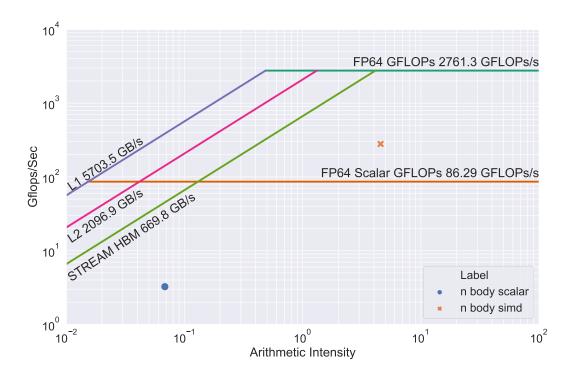

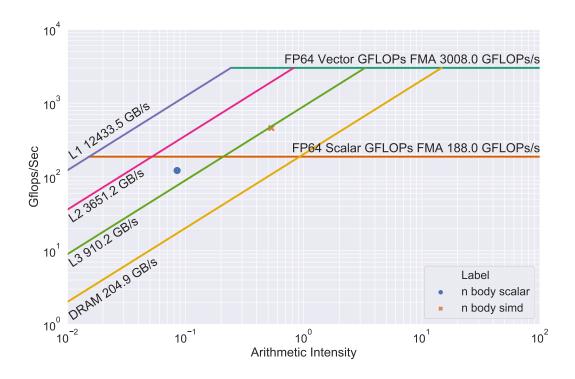

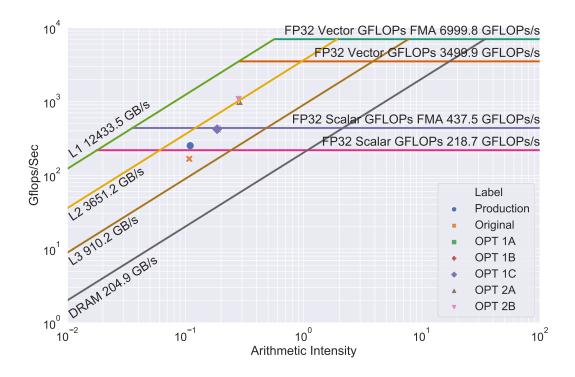

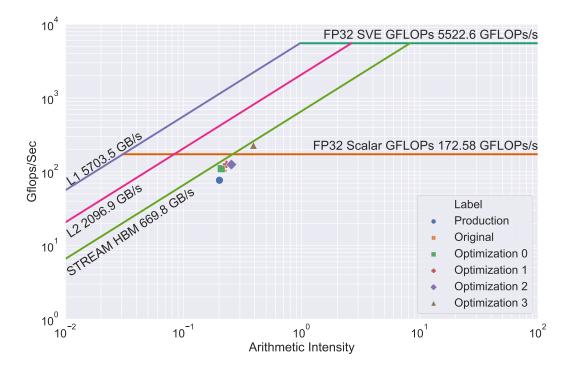

| 11.  | Roofline plot for N Body on the A64FX                                                                                | 50   |

| 12.  | Roofline plots for N Body on the Cascade Lake                                                                        | 51   |

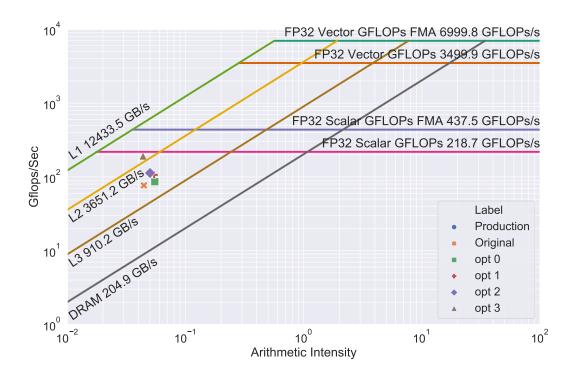

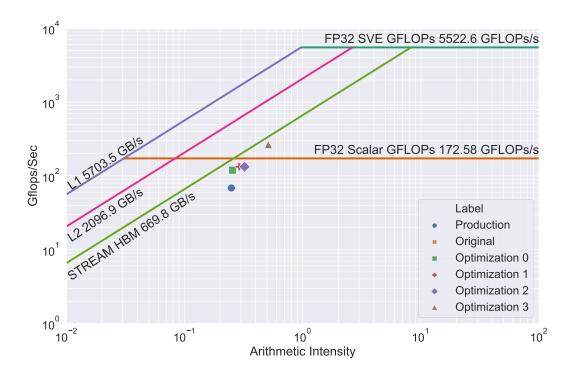

| 13.  | Roofline plots for matrix multiplication on the A64FX                                                                | 52   |

| 14.  | Roofline plots for matrix multiplication on the Cascade Lake                                                         | 53   |

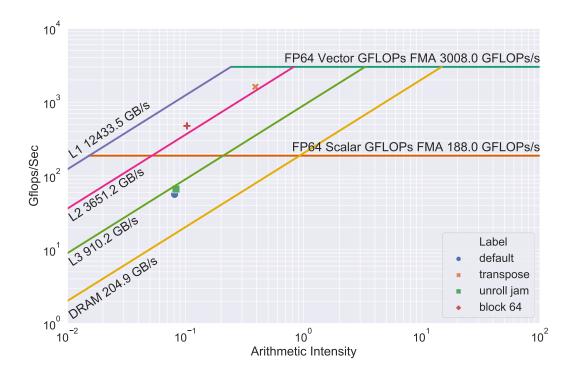

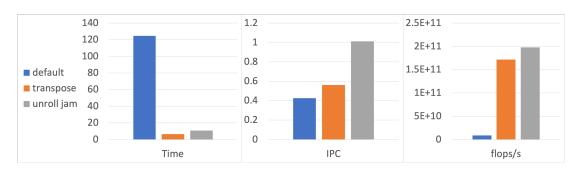

| 15.  | Overall metrics for the STREAM benchmark run at each level of cache on the A64FX                                     | 65   |

| 16.  | Overall metrics for the STREAM benchmark run at each level of cache on the Cascade Lake                              | 65   |

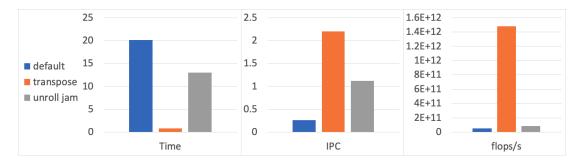

| 17.  | Overall metrics for three versions of the Matrix Multiplication run on the A64FX                                     | 66   |

| Figu | ure                                                                                                   | Page |

|------|-------------------------------------------------------------------------------------------------------|------|

| 18.  | Overall metrics for three. versions of the Matrix<br>Multiplication benchmark run on the Cascade Lake | . 67 |

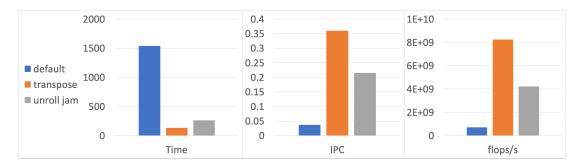

| 19.  | Overall metrics for three versions of the Matrix Multiplication run on the A64FX                      | . 68 |

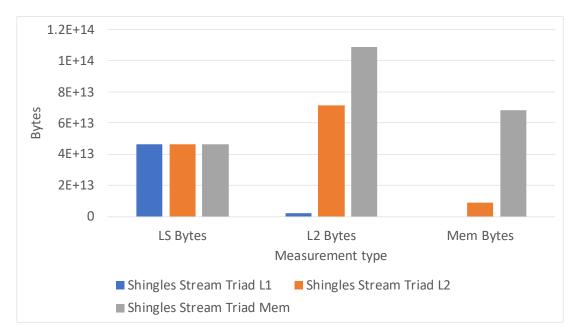

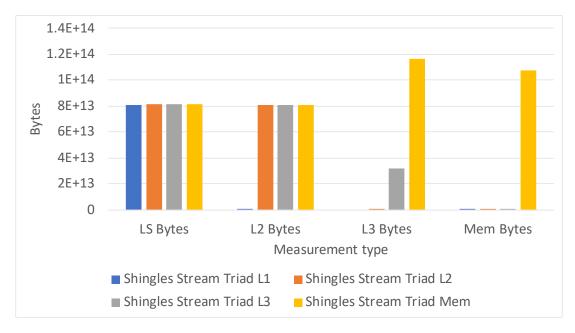

| 20.  | A64 bytes at each cache level for each STREAM size                                                    | . 70 |

| 21.  | Cascade Lake bytes at each cache level for each STREAM size                                           | . 71 |

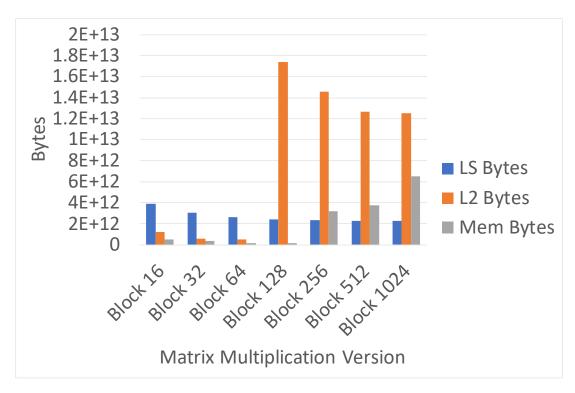

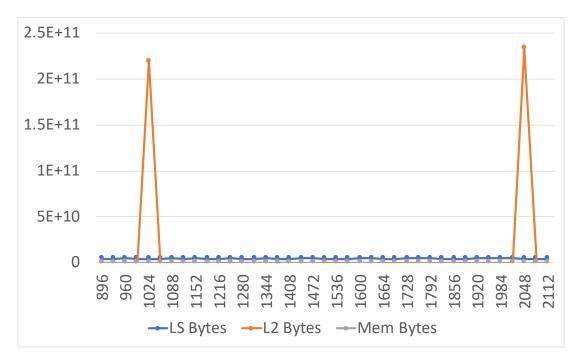

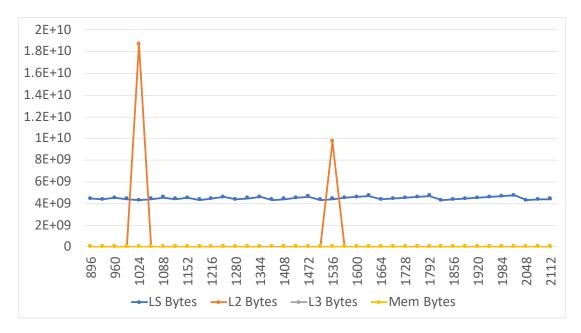

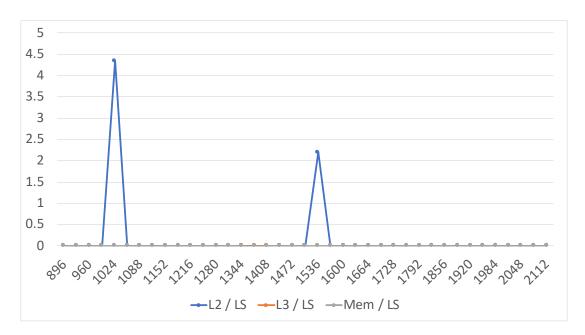

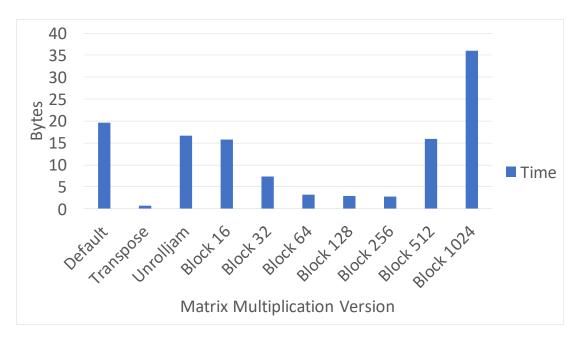

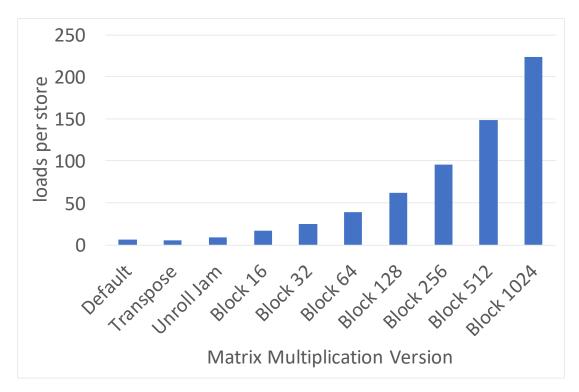

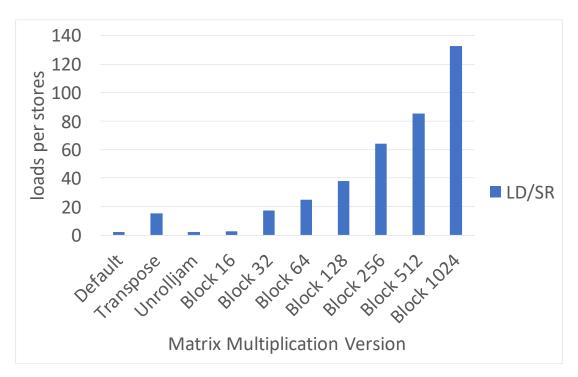

| 22.  | Data movement relative to block size for the matrix multiplication kernel on the A64FX                | . 72 |

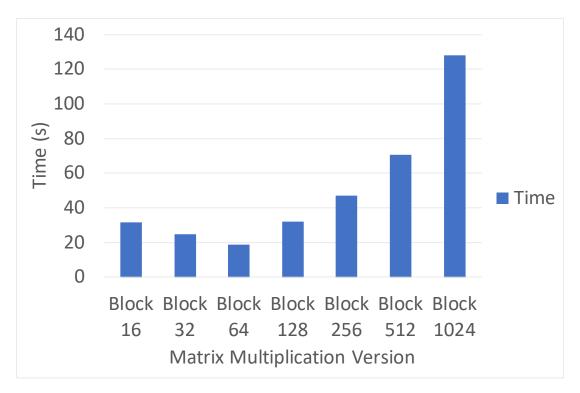

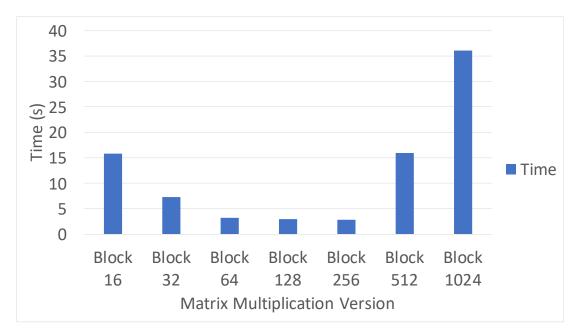

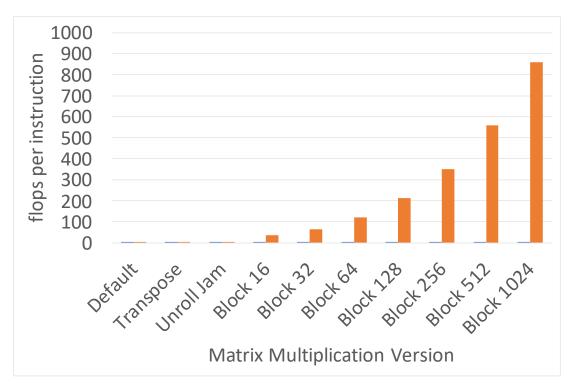

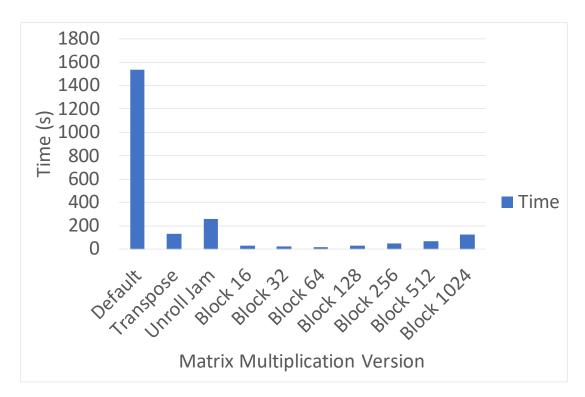

| 23.  | Execution time relative to block size for the matrix multiplication kernel on the A64FX               | . 73 |

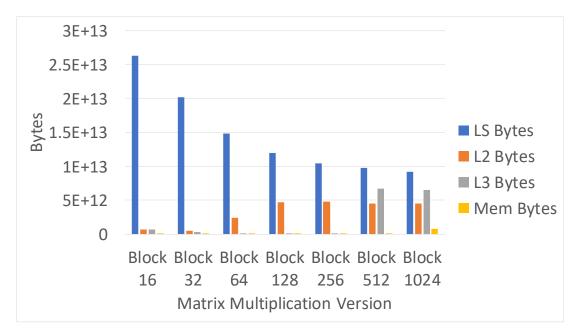

| 24.  | Cascade Lake bytes relative to block size for the matrix multiplication kernel                        | . 74 |

| 25.  | Cascade Lake time relative to block size for the matrix multiplication kernel                         | . 75 |

| 26.  | A64FX bytes relative to the offset in our associativity example                                       | . 76 |

| 27.  | Cascade Lake bytes relative to the offset in our associativity example                                | . 77 |

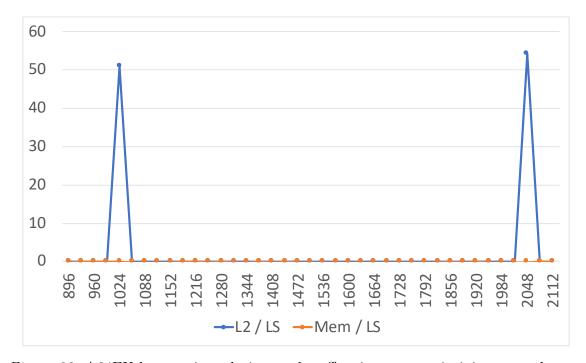

| 28.  | ${ m A64FX}$ byte ratios relative to the offset in our associativity example                          | . 78 |

| 29.  | Cascade Lake byte ratios relative to the offset in our associativity example                          | . 79 |

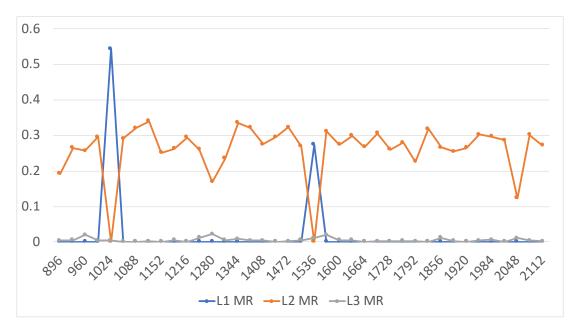

| 30.  | A64FX miss rates relative to the offset in our associativity example                                  | . 80 |

| 31.  | Cascade Lake miss rates relative to the offset in our associativity example                           | . 81 |

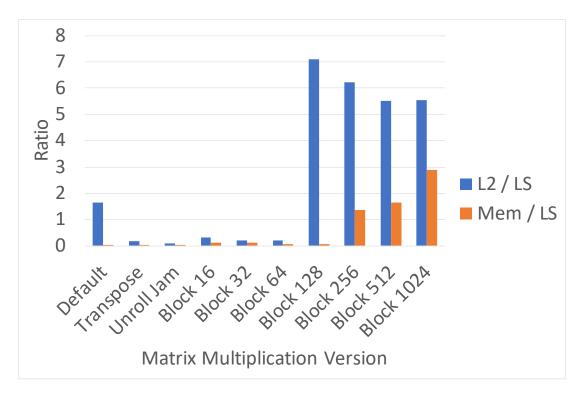

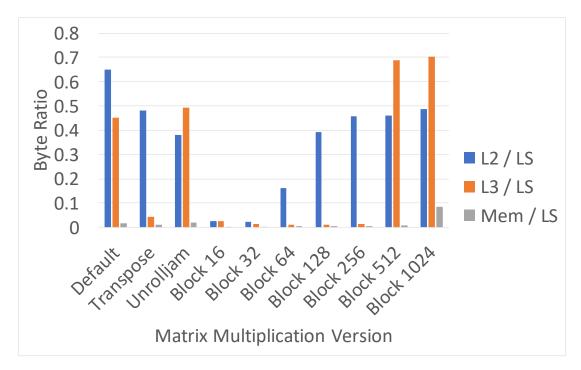

| 32.  | A64FX byte ratios for the matrix multiplication variations                                            | . 82 |

| 33.  | Cascade Lake byte ratios for the matrix multiplication variations                                     | . 83 |

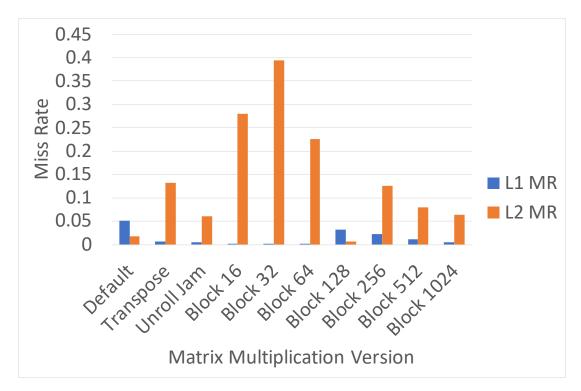

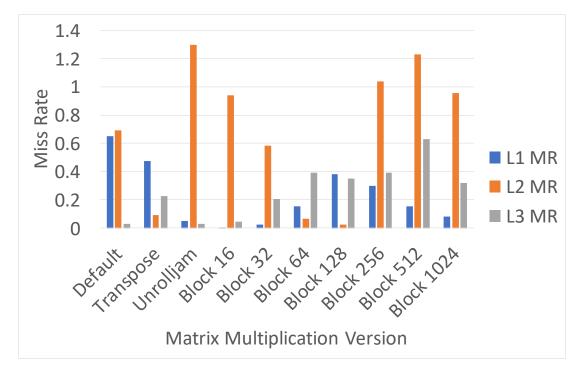

| 34.  | A64FX miss rates for the matrix multiplication variations                                             | . 84 |

| 35.  | Cascade Lake miss rates for the matrix multiplication variations                                      | . 85 |

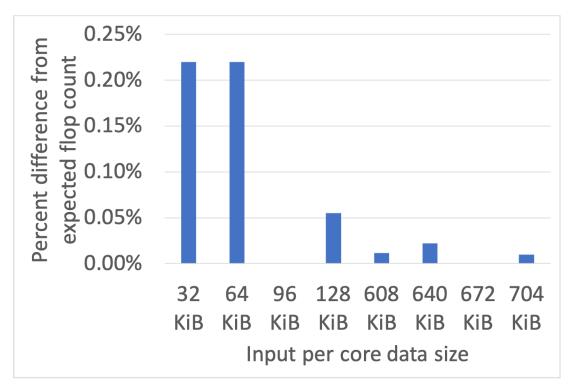

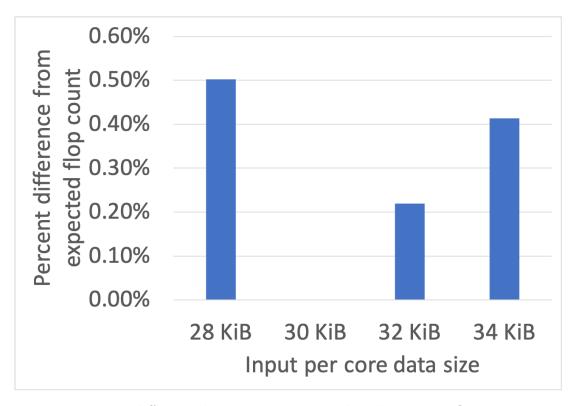

| 36.  | Percent difference between the expected and measured <b>flops</b> for STREAM run on the A64FX         | . 87 |

| Figu | ıre                                                                                                  | Page  |

|------|------------------------------------------------------------------------------------------------------|-------|

| 37.  | Percent difference between the expected and measured <b>flops</b> for STREAM run on the Cascade Lake | . 88  |

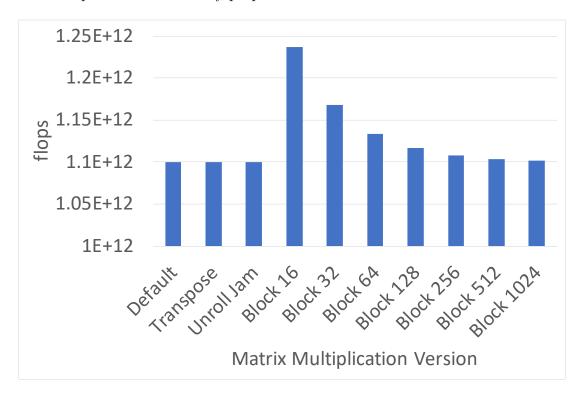

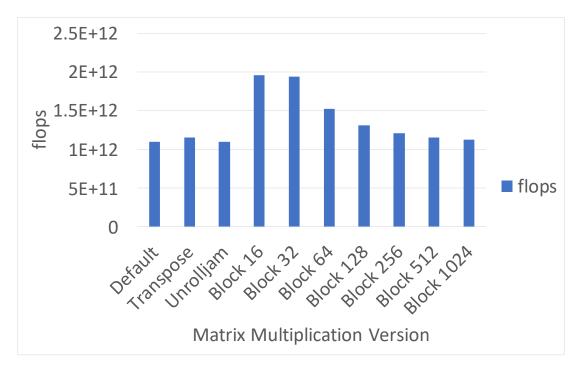

| 38.  | A64FX flops for the matrix multiplication variations                                                 | . 89  |

| 39.  | Cascade Lake <b>flops</b> for the matrix multiplication variations                                   | . 90  |

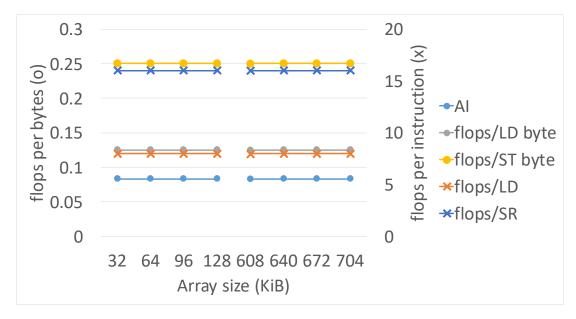

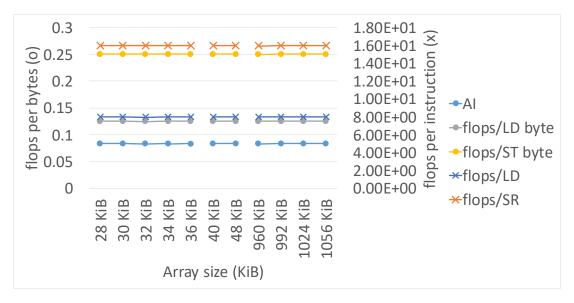

| 40.  | A64FX computation data rates for STREAM with several data sizes                                      | . 93  |

| 41.  | Cascade Lake computation data rates for STREAM with several data sizes                               | . 94  |

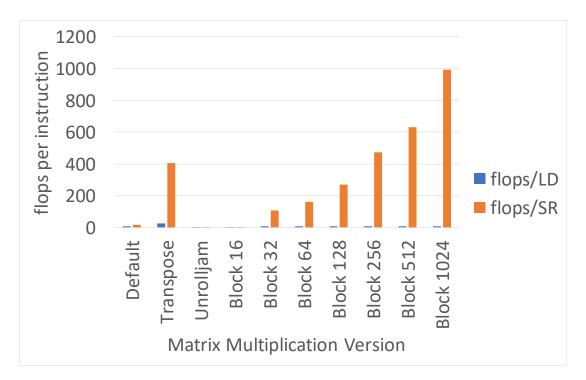

| 42.  | A64FX flops / LD and flops / ST for the matrix multiplication variations                             | . 95  |

| 43.  | Cascade Lake flops / LD and flops / ST for the matrix multiplication variations                      | . 96  |

| 44.  | A64FX <b>Time</b> for the matrix multiplication variations                                           | . 97  |

| 45.  | Cascade Lake <b>Time</b> for the matrix multiplication variations                                    | . 98  |

| 46.  | A64FX LD ins/ST ins for the matrix multiplication variations                                         | . 98  |

| 47.  | Cascade Lake LD ins/ST ins for the matrix multiplication variations.                                 | . 99  |

| 48.  | A64FX AI flops / LD bytes and flops / ST bytes for the matrix multiplication variations              | . 99  |

| 49.  | Cascade Lake AI flops / LD bytes and flops / ST bytes for the matrix multiplication variations       | . 100 |

| 50.  | A64FX AI and flops / LD bytes for the matrix multiplication variations                               | . 100 |

| 51.  | Cascade Lake <b>AI</b> and <b>flops / LD bytes</b> for the matrix multiplication variations          | . 101 |

| 52.  | Hotspots of Pagosa                                                                                   | . 120 |

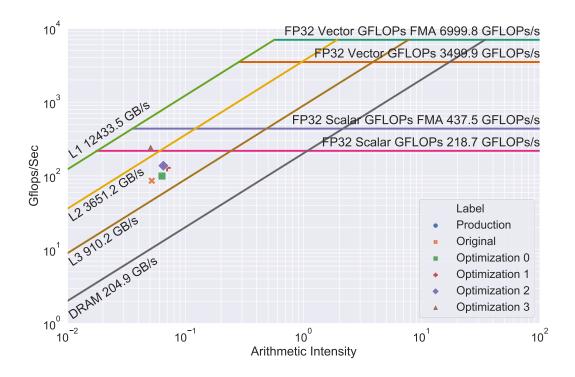

| 53.  | A roofline with application points for the Vofid kernel on the A64FX                                 | . 125 |

| 54.  | A roofline with application points for the Vofid kernel on the Cascade Lake                          | . 127 |

| Figu | re                                                                           | Page  |

|------|------------------------------------------------------------------------------|-------|

| 55.  | A roofline with application points for the Strength 1 kernel on A64FX        | . 133 |

| 56.  | A roofline with application points for the Strength 1 kernel on Cascade Lake | . 134 |

| 57.  | A roofline with application points for the Strength 2 kernel on A64FX        | . 135 |

| 58.  | A roofline with application points for the Strength 2 kernel on Cascade Lake | . 136 |

## LIST OF TABLES

| Tab | ole                                                                        | Page |

|-----|----------------------------------------------------------------------------|------|

| 1.  | Architecture details for the systems used in this dissertation             | 17   |

| 2.  | Cache details of the two systems                                           | 32   |

|     |                                                                            |      |

| 3.  | Results from the FP Crunch benchmark on A64FX                              | 40   |

| 4.  | Results from the FP Crunch benchmark on Cascade Lake                       | 40   |

| 5.  | Counters used to calculate the Bytes on A64FX                              | 42   |

| 6.  | Counters used to calculate the flops and bytes on Cascade Lake             | 43   |

| 7.  | Counters used to calculate the FLOPs on the A64FX                          | 47   |

| 8.  | Roofline application point data for N Body on two systems                  | 50   |

| 9.  | The Proposed set of existing and new metrics                               | 56   |

| 10. | PAPI [1] Counter names used to calculate the data movement on Cascade Lake | 58   |

| 11. | Counters used to calculate data movement on A64FX                          | 58   |

| 12. | PAPI [1] Counter names used to calculate the data movement on Cascade Lake | 61   |

| 13. | Counters used to calculate the <b>flops</b> and IPC on A64FX               | 61   |

| 14. | flops / fp ins for each version of matrix multiplication                   | 91   |

| 15. | Compilers and options for the N-Body application                           | 103  |

| 16. | N-Body data from unoptimized and optimized versions                        | 104  |

| 17. | XSBench event kernel data                                                  | 107  |

| 18. | Cloverleaf PdV kernel data                                                 | 110  |

| 19. | PENNANT doCycle kernel data with different OpenMP chuck sizes              | 113  |

| 20. | VPIC Data for the $center_p$ kernel                                        | 116  |

| Tab | le                                                           |  |  |  | I | Page |

|-----|--------------------------------------------------------------|--|--|--|---|------|

| 21. | Versions of the Vofid kernel                                 |  |  |  | • | 123  |

| 22. | Counter results for the Vofid kernel on A64FX $$             |  |  |  |   | 129  |

| 23. | Counter results for the Vofid kernel on Cascade Lake $$      |  |  |  |   | 130  |

| 24. | Versions of the Strength functions                           |  |  |  |   | 133  |

| 25. | Counter results for the Strength 1 kernel on A64FX $$ . $$ . |  |  |  |   | 139  |

| 26. | Strength 1 counter results on Cascade Lake                   |  |  |  |   | 140  |

| 27. | Strength 2 counter results on A64FX                          |  |  |  |   | 141  |

| 28. | Counter results for the Strength 2 kernel on Cascade Lake    |  |  |  |   | 142  |

#### CHAPTER I

#### INTRODUCTION

The research presented in this dissertation explores the potential of using Hardware Performance Monitors to analyze application performance consistently across multiple types of CPUs. Hardware Performance Monitors (also called hardware counters) have been used for many years to study the performance of software and systems. The counters offer a close look at how software uses the microarchitecture of a processing unit, which enables users to gain detailed insight into the performance of an application running on a particular system. Unfortunately, the methods based on hardware counters often restrict users to specific systems and only provide limited information about the algorithm targeted by the analysis. This dissertation explores the hypothesis that hardware counter metrics can provide actionable performance information to users on a diverse set of CPU types. We prove the accuracy of our hypothesis by developing a set of such hardware counter metrics, validating those measurements, and applying them to a series of example applications on two CPU types.

This hypothesis is transformed into our central research question: Can hardware counters on different CPU types produce the same set of performance metrics that help the user understand the performance of scientific applications?

We answer this question in four stages

- Can an existing CPU-agnostic performance analysis technique be used in conjunction with hardware counter metrics derived from diverse CPU types?

- Can additional metrics be collected to add further information to the performance analysis?

- Does this provide useful info in a variety of performance cases?

- Does this scale to a full application?

For this research, we restrict the scope of hardware and software. Any area of computing can make use of performance analysis to get the most use out of its systems, but we focus on scientific computing which has a long history of using some of the largest Supercomputers available. In general, these applications rely on floating-point arithmetic and have a computational rate defined as the number of floating-point operations executed per second. We limit ourselves to these applications because of the consistency of this definition of performance and the long history of performance analysis in the scientific computing community. Each year a larger portion of scientific computing moves to processing on Graphics Processing Units (GPUs) instead of the more generalizable Central Processing Units (CPUs). We limit the scope of the work to CPUs because there is a sufficient variety of microarchitectures to impede the portability of metrics, justifying the need for application-oriented metrics. In future work, we can extend the scope to GPUs and other accelerators which would add variety to the microarchitectures.

We describe the current state of related research in Chapter II. This chapter discusses historical and modern methods of using hardware counters for performance analysis, with particular focus on the limitations of these methods that our research aims to resolve. In addition, we discuss the Roofline Method of modeling processors and performance. We use hardware counters to gather the metrics required for this method and to validate the benchmarks necessary to produce the architectural models. Our research builds on the work discussed in this chapter.

Throughout the dissertation, we use a consistent set of tools, systems, and benchmarks. These pieces of our methodology are described in Chapter III. In this chapter, we describe the set of tools we use for collecting and processing hardware counter data although users may have other methods that they prefer. Additionally, we describe the two CPU types we use throughout this work and the other aspects of the systems including compilers and operating systems. Finally, we describe several benchmarks that we use to evaluate and then showcase hardware counter metrics. The infrastructure discussed in Chapter III is used repeatedly throughout the dissertation, but additional tools and applications are introduced as needed in later chapters.

After establishing this context for the research, we present our contributions. The central aim of the contributions is to assess the feasibility of using consistent hardware counter metrics across different microarchitectures to provide users with empirical application-oriented performance information. We demonstrate our methods of performance analysis by first introducing a novel method of using hardware counters to conduct Roofline-based performance analysis. Then we develop a larger range of empirical hardware counter metrics that are applicable across different microarchitectures along with a series of analyses that showcase the use of the metrics. Finally, we apply the combined methods to a scientific application, to gain insight into the change in performance over several versions.

In Chapter IV, our contributions begin by building on performance analysis using the Roofline Model. We chose this starting point because the roofline provides a simple model of a generic CPU that is applicable across all modern CPU types. It connects this model to target applications by plotting the application point on the model. This combination provides context for the performance of the

application and indicates potential limiting hardware features. We introduce a set of benchmarks that are useful for building empirical Roofline Models. Additionally, we use these benchmarks to validate a set of hardware counter metrics which can be used to plot the application point on the Roofline Model. The result is a new method to empirically use Roofline Modelling to understand the performance of an application on different CPU types.

Starting with roofline measurements, we take a similar approach to defining a set of performance metrics in Chapter V. The Roofline Model uses two metrics that apply to any CPU, and we decided to search for other microarchitecture-agnostic metrics that hardware counters could measure. We sought to define metrics that provided information 1) about common hardware features, 2) related to the algorithm or data structures, and 3) can be measured with hardware counters on our two target systems. Our efforts resulted in a set of metrics that users can apply to their application without detailed knowledge of the microarchitecture. Some of these metrics are novel and some have been used by other researchers. The focus of the metrics is on how data is moved in the system and how computation is performed.

Based on this set of metrics, we conduct several analyses of benchmarks and mini-applications in Chapter VI. Each of the benchmarks and mini-applications we consider is related to one or scientific applications, so the performance features will be relevant to real-world users. We collect data on the two systems discussed in Chapter III and for multiple versions of each target mini-application. This process allows us to demonstrate the applicability of the metrics to a range of performance situations.

Finally, in Chapter VII, we present a case study of analysis of Pagosa, a fluid dynamics application that is in widespread use. We use both the Roofline Model analysis and the hardware counter metrics presented in previous chapters to study the performance of a series of optimizations to key computational kernels in the application. This study addresses why certain optimization efforts worked for the kernels, demonstrating the usefulness in aiding developers' evaluation and optimization of application performance.

The methods presented in this dissertation show that hardware counters can be used to conduct performance analysis focused on the application's features rather than the specifics of a microarchitecture. We relate our method to the commonly used performance analysis method based on the Roofline Model (Chapter IV) and extend it to new areas with the introduction of portable hardware counter metrics (Chapter V). Through a series of case studies we show that the method is scalable to small kernels (Chapter VI) and full applications (Chapter VII). In total, this research demonstrates that a set of hardware counterbased metrics can provide actionable information to the user across a set of CPUs with different ISAs, microarchitectures, and hardware counter interfaces.

#### CHAPTER II

#### BACKGROUND

The research presented in this dissertation builds on the long history of node-level performance analysis of scientific applications. Scientific applications are a vital part of research for scientists in many fields who rely on simulation or data processing to conduct their research [2] [3]. Performance analysis and optimization of these applications is a necessary part of the process since time on computing clusters can be expensive or a bottleneck to other research. Of the many aspects of performance in a scientific application, we chose to focus on the performance of computational kernels running on CPUs. At this level, performance analysis considers the use of the processor pipeline, arithmetic units, caches, main memory, and other "node-level" aspects of the system.

There is a great deal of background information available to those interested in High Performance Computing (HPC) in general. We recommend Eijkhout's open-source textbook [4] for an introduction to many of the intersecting fields that an HPC user may encounter. Robey and Zamora [5] is an up-to-date text that covers the systems and software that are found in modern HPC systems. Jeffers and Reinders [6] bring together a set of parallel computing examples with many details and implementations to help readers understand parallel computation. For those interested in the architectural aspects of HPC, Hennessy and Patterson have written six editions of textbooks guiding readers through computer architecture [7]. Also, Dean et al. [8] provides insight on recent trends in computer architecture and the future of the field. Similarly, Jalby et al. give their thoughts on the future of HPC as we enter the Exascale era [9]. There are doubtless many more authors

whose work readers may find useful, but we hope these will provide a starting point for the interested reader.

We do not expect that the reader will understand the full scope of HPC research (the author certainly falls short of this goal), but the reader may find a review of performance analysis useful. Performance analysis can be based on data from empirical studies, information gathered statically through the examination of algorithms and hardware, or the results of simulation. Empirical analysis is much like other sciences; measurements are taken and results are examined leading to new hypotheses and experiments. Static analysis or simulation provides information that may be difficult to measure empirically, but these methods are also limited in the amount of detail they can consider. Application developers use the information gathered from any of these methods to understand the performance of the application.

We focus on empirical performance analysis because our background research led us to the conclusion that hardware counter information was not used to its full potential. This conclusion encouraged us to explore our primary hypothesis that hardware counter metrics can provide actionable performance information to users on a diverse set of CPU types.

Performance analysts who use empirical analysis can use a range of metrics from simple timers to tools that record and trace each memory address that an application uses. The methods we use in the following chapters use hardware counters to collect data on events that occur in the CPU or memory subsystem while an application is running. We provide background on this method of analysis in Section 2.1. The Roofline Model is a model of a CPU that can be used in conjunction with measurement or static program analysis to provide the user with

an understanding of their application. In Section 2.2, we describe the model and the measurements that are necessary to build and use the model.

#### 2.1 Performance Measurement and Analysis of Applications

Measuring the performance of an application can be as simple as using a clock to check how long an application takes to run or involve complex toolchains to gather detailed information on the hardware. Any measurement of an application running on the target system is empirical analysis.

Modern programming languages offer interfaces to the operating system timers which can be placed at key points in an application. By measuring key points throughout the application, the user can identify which areas are most important. Amdahl's Law [10] tells us that we need to focus our optimization efforts on the most time-consuming portions of the application, so this "hotspots" analysis is a good first step.

The metrics we introduce in this research are all based on hardware counters. Physically, these are registers built into CPUs and GPUs that record events that occur in the processor. Conveniently, libraries such as PAPI [1] and perf [11] provide human-readable names and high-level language interfaces for the counters. The PAPI authors regularly update these interfaces for new CPUs.

The data collection can occur in one of two ways. Sampling is one option, which periodically interrupts the program to record the counter values. This method is less intrusive to the application but also less accurate. It is used by TAU [12, 13] and HPCTookit [14, 15]. Alternatively, the measurements can be inserted into an application at key points. This instrumentation can be done manually as in Caliper [16] and Likwid [17], or a tool can perform automatic instrumentation which is another option in TAU [12, 13]. We find that sampling

provides a good overview of the program which can be used to choose particular areas of focus for the instrumentation.

In addition to the open-source tools, many vendors provide tools for users to measure the performance on their systems. Intel offers VTune, ARM has Forge, and HPE provides Craypat. These tools are professionally maintained with nice graphic user interfaces but can limit the user to particular products.

Hardware counters provide unique information about the inner workings of the processor, but the uniqueness causes challenges for validation. Since there is no way to check many of the values measured by counters, validation is a challenge. Carefully made benchmarks [18, 19, 20, 21] are the best way to validate the values provided by counters.

At first hardware, counters were primarily used to characterize the workload of systems. In [22], the authors use counters to identify which instruction types have the largest impact on the performance of a mainframe system. Williams et al. [23] compare two identical systems with different workloads to help guide future system design. Finally, Cvetanovic and Bhandarkar [24] compare technical and commercial workloads to gain insight into the similarities and differences between the two workload types.

In [25], Zagha et al. conduct analysis and optimization of computational kernels based on the results of hardware counter data. The authors describe the implementation of the hardware required for the counters along with the software that enables the application developer to make use of them. Additionally, the authors use several cache metrics similar to our own to identify performance bottlenecks in their target kernels.

When studying the performance of a particular kernel, the most common method of hardware counter analysis is to identify a base measurement of time or work and then count events that fill up the base value to establish what hardware features are most important to the performance of an application. Eyerman et al. [26, 27] use cycles per instruction (CPI). The authors effectively visualize where the potential CPI is lost which makes the method useful to developers. Similarly, Nowak et al. present the HCA [28], which uses a tree structure to visualize the allocation of CPU cycles guiding users to performance bottlenecks. Yasin introduces the Top-Down Method of Analysis in [29], which uses slots (available spots for instructions to retire in each cycle) as the base metric. The TMA has been extended several times [30, 31] and is widely used on Intel systems, and may soon be used on ARM [32] and AMD [33], as well. These methods are thorough, but require the user to have detailed knowledge of the CPU architecture to be useful. Developing this knowledge is an added burden for many scientific software developers who need to focus their attention on their discipline.

Several authors have worked on identifying particular metrics for performance analysis [34, 35]. Their methods have inspired some of ours, in particular identifying ways to consistently validate counters across systems. We build on this work by adding new metrics beyond Bandwidth and data movement.

#### 2.2 Arithmetic Intensity and the Roofline Model

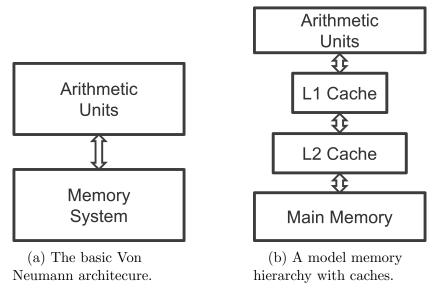

One of the simplest models of computing is the Von Neumann architecture (Figure 1a). This model presents a computer as having two primary functions; data movement and arithmetic. The model is simple but holds true even for modern computers.

Figure 1. Comparison between the basic Von Neumann architecture and a more modern model with multiple levels of memory caching.

This model can be used to understand the performance of a computer system by looking at the throughput of operations for arithmetic and data movement parts of the hardware. If the data movement is not operating quickly enough then the arithmetic functions are delayed waiting for the necessary data and vis a versa. The point at which arithmetic and movement match is known as "machine balance" [36].

2.2.1 Arithmetic Intensity and Data Movement. In Callahan's work [36], the data movement is simply defined as the amount of data moved between the main memory and the processor. However, in the intervening years, there have been many layers of cache added between the processor and the main memory (see Figure 1b). The amount of data varies at each level, forcing users to question which is most useful. Additionally, there are several techniques for measuring or estimating the data movement each of which has its advantages and disadvantages.

Modern processors usually have 2 or 3 levels of cache and data movement between any of these levels can be used for AI. We refer to the movement between the level 1 cache (closest to the processor) and the processor as  $Data_{L1}$ . Similarly, movement between the level 2 and level 1 cache is referred to as  $Data_{L2}$ .

When referring to data movement to or from a particular level of cache, this is subtly different from the hardware-defined bandwidth of the cache. Most existing caches have a single set of ports that moved data from the layer below and layer below, but we only refer to the data moved to or from the next level closest to the CPU. We think of this metric as the "apparent bandwidth" i.e. what the CPU can access when the data is residing in the cache level in question. While there are situations in which the user will want to understand the utilization of the physical bandwidth at a particular cache level, the apparent bandwidth method is easier to relate to an application kernel and therefore more useful for improving the performance.

In the original Roofline [37], data movement was defined as that moved between the main memory and the last level of cache ( $AI_{mainmem}$ ). The main memory bandwidth is often a significant limiting factor to the performance of applications so there is significant motivation to focus on this level. Additionally, users tend to understand the bottleneck posed by the main memory and there are many optimizations (i.e. cache block and data layout optimizations) that aim to alleviate the bandwidth and apply to many scientific kernels.

Unfortunately,  $AI_{mainmem}$  has significant disadvantages. In particular, the volume of data moved can be inconsistent for different data sets and many algorithmic changes. For example, a kernel that repeatedly iterates through a data set that is significantly larger than the caches will have more data movement than

a kernel operating on a data set that is close to the size of the last level cache. As a result, the  $AI_{mainmem}$  will be volatile relative to the data st size. Similarly, if a cache blocking optimization is applied so that the kernel uses the cache's temporal locality, then the  $AI_{mainmem}$  will change with the reduced main memory data movement. In the most extreme case, data will fit entirely in a cache level and the  $AI_{mainmem}$  will become non-sensical. Such variations in the  $AI_{mainmem}$  can be confusing and difficult to connect back to changes in the algorithm.

At the other extreme is the  $AI_{L1}$ , which uses the data moved between the first level of cache and the processor. This method was popularized by the Cache Aware Roofline Method [38]which produced Rooflines for each of the cache levels all based on the  $AI_{L1}$ . This method provides a consistent understanding of the data moved relative to the amount of computation even with changes to the data size or optimizations designed to better use cache.  $AI_{L1}$  is designed to be more closely tied to the algorithm under consideration enabling the user to more easily compare optimizations and predict what changes will best improve application performance. Additionally, it allows bandwidth lines to be plotted fr all the cache levels, so the user can understand which level is having the most impact on performance. The main downside is that new users of the Roofline are often not informed of the differences between  $AI_{L1}$  and  $AI_{mainmem}$  leading to significant confusion.

For users looking for additional detail, they can combine the AI versions into a single Roofline. This method, the Integrated Roofline, plots each cache line based on its own AI and then plots one application point for each AI. The resulting plots can be quite confusing but offer more information on how the different cache levels are used.

The versions discussed so far are all defined relative to the hardware in use. One final option is a theoretical AI ( $AI_{theory}$ ). In this case, data movement and floating-point operations can be computed by algorithm analysis and plotted accordingly. This method is most closely related to the formulation of the algorithm in question but can neglect important factors such as compiler optimizations. If these changes aren't understood, then the user may mischaracterize the kernel that is actually run on the system.

While the author's personal preference is the  $AI_{L1}$ , there are good reasons for the other options. What is most important is that the user understands which method is in use and takes that into consideration when reasoning about the performance of the application.

2.2.2 Roofline variations. The Roofline model [37] of performance recognizes the computation and data movement as the primary limiting functions of a given processor. The model then compares the floating point operations per second (flops/s) to the AI to model the performance potential of the processor. Users can use the AI and flops/s of their application to compare to the potential performance. The position of the application point to the ceilings that represent the performance potential of different hardware features can help the user identify areas for improvement. Roofline Modeling is a useful tool, so researchers have developed many versions.

The peak potential of the processor generally includes all possible hardware optimizations available on the system including, SIMD operations, FMA instructions, threads, and any others. The user can then add roofs where each of those features is removed to measure the reduced potential ceiling. For the data

movement part of the Roofline, cache level are often used, but features such as prefetching, unit stride access patterns, and NUMA domains are also possible.

The original version defined the arithmetic intensity in terms of the data moved between main memory and the last level of cache, but as discussed above, this has some drawbacks. In particular, there are no ceilings for the different cache levels. The Integrated Roofline model [39] adjusts the arithmetic intensity to each level of cache. This innovation allows the user to have ceilings of bandwidth for each cache level, but complicates the plotting of application points since there are multiple AI measurements to choose from. The Cache Aware Roofline resolves these issues by using the  $AI_{L1}$  as we discussed previously. We choose the Cache Aware version for our work in Chapter IV because of the ease of use.

Many other variations of the Roofline model exist, often targeting particular types of CPU hardware and software. Denoyelle et al. [40] target nodes with heterogeneous memory hierarchies. The authors of [41] modify the Roofline for asynchronous runtimes. Cardwell and Song [42] extend the model for distributed memory systems. Choi et al. modified the model to a greater extent to create a Roofline Model of Energy in [43].

Two separate groups, Marques et al. [44] and Cabezas and Püschel [45], extend the roofline to consider the instruction mixes of the application being studied. This allows the user to have more realistic expectations of the potential and a better understanding of which ceilings are limiting performance.

In addition to many versions of the Roofline, there are several papers about focused on applying the Roofline model in different situations. Lo et al. [46] present a tool to create the architectural model, and Doerfler et al. [47] apply the model to

performance analysis of an application on an Intel XEON Phi processor. Norris et al. [48] present a visualization tool for Rooflines.

Most similar to our work, Ofenbeck et al. [49] develop a detailed method of measuring data for application points for the original Roofline. This work is limited to Intel CPUs and single-threaded validation.

# 2.3 Wrapping up the background

In this chapter, we have provided an overview of empirical performance analysis of scientific applications with particular focus on the use of hardware counters to collect data. Additionally, we discussed the Roofline model of performance and the different ways that a user may measure arithmetic intensity. Lacking in the existing literature are hardware counter metrics that provide actionable performance information to users on a diverse set of CPU types. The remainder of this dissertation shows that such metrics are possible for at least two CPUs with different sets of hardware counters.

### CHAPTER III

### **METHODOLOGY**

Throughout this dissertation, we use a consistent set of systems, tools, and benchmarks to develop and demonstrate our analysis methods. The systems we use have several major differences, especially in what types of data are measured in the hardware counters. The tools and benchmarks we try to keep consistent for the whole dissertation. We present the details of our systems, tools, and benchmarks in this Chapter.

### 3.1 Systems

We use two CPU types to design and test our methods. The first is an Intel Cascade Lake Gold, and the second is the Fujitsu A64FX. While both have 48 cores and 512-bit SIMD Instructions, the most important differences between the two appear in the memory subsystems. Cascade Lake's main memory is DDR with a peak Bandwidth (BW) of approximately 200 GB/s, while A64FX has High Bandwidth Memory (HBM) that measures 800 GB/s. Additionally, the Cascade Lake has three levels of cache while the A64FX has only two levels. Table 1 shows detailed specifications comparing the CPUs and memory subsystems.

Table 1. Architecture details for the systems used in this dissertation.

|                  | A64FX          | Cascade Lake Platinum 8260 |

|------------------|----------------|----------------------------|

| ISA              | ARM with SVE   | x86 with AVX512            |

| Sockets          | 4              | 2                          |

| Cores per socket | 12             | 24                         |

| Threads per core | 1              | 2                          |

| L1 Cache         | 64KiB per core | 32KiB per core             |

| L2 Cache         | 32 MiB Total   | 1 MiB/core (48MiB Total)   |

| L3 Cache         | None           | 35.75 MiB                  |

| Main Memory      | 31 GB HBM      | 188 GB DRAM                |

| Cache Line size  | 256 Bytes      | 64 Bytes                   |

On the Cascade Lake system we compile the applications with the Intel compiler version 19. and OpenMPI 3.1.6 when MPI is used.

On the A64FX we use three different compilers depending on the needs.

### 3.2 Tools

Measuring hardware counters requires the users to record the counter values and program data then process that data. We discuss some of the tools for empirical measurement of hardware counters in Chapter II Section 2.1. This section covers the methods we use.

PAPI [1] and lilbpfm [11] interface directly with the hardware and provide a consistent interface for accessing hardware counters on a variety of CPU architectures. The developers regularly update the libraries to keep pace with new CPUs. We use these libraries together which allows us to access the counters through the human-readable interface. Counter names used later in the dissertation will use the PAPI names.

We also use the Caliper [16] library to connect the PAPI interface to applications. Although PAPI can be directly called from applications, we use the Caliper library because it handles the interface with PAPI alongside the metadata necessary for understanding OpenMP and MPI results. We configure Caliper to write the results to a set of JSON files, which provide consistent format for processing the results.

As we discuss in Chapters IV and V, we need to collect around 50 counters to compute all the metrics presented. This process takes some time because there are more events counted by hardware counters than there are registers to count them. As a result, we automate the process of repeatedly running the application to collect all of the necessary counters.

Once the data is collected, we use python scripts to automatically compute our metrics.

### 3.3 Benchmarks

We use a set of benchmarks (small, carefully crafted applications) to help us understand how the CPUs are operating and exactly what the hardware counters are measuring. These benchmarks can serve multiple purposes, including validating hardware counter metrics and developing a deeper understanding of the CPU. We use the benchmarks in this section for both purposes and refer to them throughout the dissertation.

3.3.1 STREAM. STREAM [50] is a widely used benchmark for measuring peak memory bandwidth by element-wise additions and multiplications of large arrays. Conventionally, STREAM includes four kernels: Copy, Add, Scale, and Triad. The data size can be adjusted to fit in each cache to measure the bandwidth at each level of cache. We use the benchmark to measure the bandwidths of the memory subsystem and to validate various hardware counter metrics.

Note that this bandwidth is not that of the physical cache interface; rather, it is the bandwidth between a set of data residing primarily in a particular cache and the CPU. This distinction is subtle, but STREAM cannot be used to measure the physical bandwidth of a cache interface because the timing is performed on the CPU. It is perfect for measuring what we think of as the "apparent bandwidth" for an application with data residing in some layer of cache. Our research is focused on understanding the performance of applications, not hardware, so we see this distinction as a useful feature of STREAM.

We adjust the STREAM benchmark so that the number of memory and arithmetic operations remain constant as the data size changes. We achieve this consistency by adding an additional repetitions loop and providing an automated tool for computing the sizes and iterations required for each system<sup>1</sup>. It is unlikely that we are the first to use STREAM in this way; however, we are not aware of any similar publications or publically available benchmarks.

We show our modified STREAM Triad in Algorithm 1. N is the number of elements in each array; this value determines the number of load and store operations performed by the benchmark. Originally, N was intended to be larger than the last level of cache to force the benchmark to repeatedly read from the main memory. We adjust N to measure how the apparent bandwidth changes as the data size changes. The first repetition loop ( $NT_{-1}$  in Algorithm 1) is part of the original STREAM benchmark designed to run the kernel multiple times for improved accuracy. We add a second iterations loop ( $NT_{-2}$ ) which can be adjusted to hold the number of operations constant while N is varied. Keeping the product of N and  $NT_{-2}$  constant ensures that the CPU performs the same amount of work on different sizes of data. This consistency allows the user to adjust the benchmark to measure the bandwidth of each layer of cache or validate the results of hardware counters.

3.3.2 FP Crunch. We designed the FP Crunch benchmark to complement STREAM by measuring the peak rate of floating-point computation on a system. Algorithm 2 shows the FP Crunch benchmark. At first glance, it appears similar to STREAM, but the trials and the iterations loops are reversed. This change allows the CPU to run the arithmetic operations rapidly without

$<sup>{}^{1}</sup>https://github.com/HPCL/benchmarks/tree/shingles/kernels/shingles/STREAM$

## Algorithm 1 STREAM Triad

```

N \leftarrow \text{Data size}

NT_{-1} \leftarrow \text{Number of repetitions}

NT_{-2} \leftarrow \text{Number of repetitions to match operation count}

a \leftarrow [N]

b \leftarrow [N]

c \leftarrow [N]

scalar \leftarrow \text{some scalar floating point}

for k \text{ in NT}_{-1}

for k \text{ in NT}_{-2}

for each i \text{ loop nest } N

a[i] = b[i] + scalar * c[i]

```

waiting on memory operations. Additionally, manual scalar replacement of the array access prevents the compiler from adding unnecessary write operations to the kernel. Finally, the kernel can be easily modified (see Chapter V) to measure different types of arithmetic operations.

### Algorithm 2 FP Crunch

```

N \leftarrow \text{Data size}

NT \leftarrow \text{Number of trials}

a \leftarrow [N]

b \leftarrow [N]

c \leftarrow [N]

for i in N

for <math>kk in kk in kk

```

3.3.3 Cache Conflict Measurement. We use a cache conflict benchmark as our last example of the data movement metrics. Similar to STREAM, this benchmark iterates over the elements in an array that is larger than the L1 cache; however the iteration steps by an offset of o. An outer loop is used to ensure the same number of load and store operations occur for all values

of o. Algorithm 3 shows the benchmark. When the offset is a multiple of the number and size of cache blocks, then cache conflicts will occur. Our array size and operation count are large enough that only a fully associative cache could handle the number of conflicts.

# Algorithm 3 Cache Conflict Benchmark

```

N \leftarrow \text{Data size}

o \leftarrow \text{offset}; \text{ number of elements between accesses}

P \leftarrow \text{Number of operations}

L \leftarrow \text{Number of trials to run: } P * \frac{o}{N}

a \leftarrow [N]

scalar \leftarrow \text{some scalar floating point}

\text{for } k \text{ in L}

\text{for } i \text{ in } 0, \dots, i + o, \dots, N

a[i] = scalar * a[i]

\Rightarrow \text{ repetitions to keep operations constant}

\Rightarrow \text{ iterate from } 0 \text{ to } N \text{ by } o

```

Compared to the other benchmarks in this chapter, the cache conflict kernel is more specialized. We designed this kernel to identify a particular performance issue that can be difficult to identify in applications. In Chapter V, we use the benchmark to validate some of our hardware counter metrics for caches.

To our knowledge, this kernel is the first benchmark developed and publicly released which can reproduce the problem of cache conflicts on modern CPUs. In future work, it may be possible to use this benchmark along with other data to develop an exact method of diagnosing cache conflicts in real-world applications.

3.3.4 Matrix Multiplication. Matrix Multiplication is a vital part of many applications and an excellent benchmark kernel for performance analysis.

The computation is well studied which allows performance analysts to try new techniques on a familiar subject and easily reproduce a variety of variations to compare.

Our Default version of matrix multiplication (Algorithm 4) is a triple nested loop that loops over the three matrices. While we will not review the process of matrix multiplication here, we will draw the reader's attention to two points. The entire B matrix is reused once for each row of the C matrix and each row of the A matrix is reused once for each column of the C matrix. This repetition provides an opportunity for the kernel to make use of CPU caches for improved data access. Secondly, if we assume column-major ordering, the kernel will skip over entire rows of the B matrix with each iteration preventing the CPU from using all of the data in the cache lines.

## Algorithm 4 Default matrix multiplication

```

Let A be an n \times m matrix

Let B be an m \times o matrix

Let C be an n \times o matrix

for i \in \{0, \dots, n-1\}

for j \in \{0, \dots, m-1\}

for k \in \{0, \dots, o-1\}

C[i, j] + = A[i, k] \times B[k, j]

```

The first optimization of matrix multiplication is to transpose the B matrix which is shown in Algorithm 5. We make this adjustment intending to improve the use of data loaded into cache in cache lines. If this optimization were included in an actual application, rather than a benchmark, the users would need to assess the overhead required to transpose B. For our studies, we ignore that overhead since our goal is to use this benchmark to compare measurements of cache efficiency. Measuring the transposition along with the matrix multiplication would only obfuscate the results.

Next, we manually unroll the j loop and jam the resulting loops back together (Algorithm 6). Known as Unrolljam, this optimization can improve the

## Algorithm 5 Transpose Matrix Multiplication

```

1: Let A be an n \times m matrix

2: Let B be an m \times o matrix

3: Let C be an n \times o matrix

4: Let BT be the Transposition of the B matrix

5: for i \in \{0, \dots, n-1\}

6: for j \in \{0, \dots, m-1\}

7: for k \in \{0, \dots, o-1\}

8: C[i,j]+=A[i,k] \times BT[j,k]

```

use of SIMD operations and the pipeline efficiency of the kernel. We apply this optimization on top of the Modern compilers can also unroll loops automatically, but we apply the optimization manually for another opportunity to study the results of our metrics.

# Algorithm 6 Unroll-jam matrix multiplication

```

1: Let A be an n \times m matrix

2: Let B be an m \times o matrix

3: Let C be an n \times o matrix

4: Let BT be the Transposition of the B matrix

5: for i \in \{0, \dots, n-1\}

for j \in \{0, 8, 16, \dots, m-8\}

6:

for k \in \{0, \dots, o-1\}

7:

C[i,j] + = A[i,k] \times B[j,k]

8:

C[i, j+1] + = A[i, k] \times B[j+1, k]

9:

10:

C[i, j + 7] + = A[i, k] \times B[j + 7, k]

11:

for j \in \{j, ..., m-1\}

12:

for k \in \{0, \dots, o-1\}

13:

C[i, j] + = A[i, k] \times B[j, k]

14:

```

Our final optimization, shown in Algorithm 7, is to block the loops so that operations that reuse matrix elements occur shortly after each other. This optimization is applied after transposing B but without the unrolling. Unrolling and Blocking can be combined, but this results in much more complex code without a significant change in performance. The combination does not add to our understanding of performance analysis, so we do not present it here.

Blocking is a common optimization for matrix codes since it can significantly improve the cache efficiency of some applications. We collect data on a range of block sizes for our study. Finding the best block size is a tedious process that can be performed using autotuners such as [51] and [52]. We explore a range of block sizes with our metrics in Chapter V which allows us to develop a better understanding of the measurements we make and the impacts of blocking on the kernels.

## Algorithm 7 Blocked matrix multiplication

```

1: Let A be an n \times m matrix

2: Let B be an m \times o matrix

3: Let C be an n \times o matrix

4: Let BT be the Transposition of the B matrix

5: for ii \in \{0, ..., BlockSize, ..., n-1\}

for jj \in \{0, \dots, BlockSize, \dots, m-1\}

6:

7:

for kk \in \{0, \dots, BlockSize, \dots, o-1\}

for i \in \{ii, \dots, ii + BlockSize - 1\}

8:

for j \in \{jj, \dots, jj + BlockSize - 1\}

9:

for k \in \{kk, \dots, kk + BlockSize - 1\}

10:

C[i, j] += A[i, k] \times B[j, k]

11:

```

These four variations of matrix multiplication provide a useful tool for our study of performance measurement. The computation is familiar to readers in many areas of computational science, so it is a useful example for reaching a wide audience. Similarly, the code needed to run a matrix multiplication is smaller, but the size of the data can be scaled to fill large caches or even multiple nodes of a cluster. Despite the simplicity of the kernel, we have four variations with different performance features, allowing us to examine and then showcase many hardware counter metrics in Chapter V.

3.3.5 N-Body Simulation. N-Body problems arise in science when a set of objects each interact continuously with each other object in the set. These systems can be modeled by computing the pairwise interactions for all the objects in each timestep. For example, this method can model the gravitational interactions of celestial bodies. Each body in the 3-dimensional space has a position, velocity, and mass. The position and velocities are represented by 3 element vectors in a Cartesian space. The equation to calculate the force applied by two objects on each other is:

$$\mathbf{f}_{ij} = G * \frac{m_i * m_j * \mathbf{r}_{ij}}{||\mathbf{r}_{ij}||^3} \tag{3.1}$$

Our N Body benchmark computes this force between each pair of bodies and then uses it to update the positions at each timestep. In the above equation the force  $(\mathbf{f}_{ij})$ , and distance between objects  $(\mathbf{r}_{ij})$  are each 3D vectors. The mass of the two objects  $(m_i \text{ and } m_j)$  are scalars. The algorithm used to simulate the system of celestial bodies is shown in Algorithm 8.

N-Body is similar to matrix multiplication in the sense that it is a simple kernel that is particularly useful for the study of performance analysis. The problem is widely known and implementations do not require a significant coding effort, but there are numerous optimization options available for those interested in applying them. For example, the data structures are based on one-dimensional arrays which can be organized as arrays of structures or structures of arrays. Some of the optimizations are not useful in the matrix multiplication algorithm, so the two kernels complement each other in that way.

# **Algorithm 8** N Body Problem

```

1: Let T be the number of timesteps to complete

2: Let dt be the change in time with each timestep

3: Let N be the number of particles

4: Let M be an array of size N with the mass of each particle

5: Let PX be an array of size N with the x position of each particle

6: Let VX be an array of size N with the x velocity of each particle

7: Let PY be an array of size N with the y position of each particle

8: Let VY be an array of size N with the y velocity of each particle

9: Let PZ be an array of size N with the z position of each particle

10: Let VZ be an array of size N with the z velocity of each particle

11: for t \in \{0, \dots, T-1\}

for j \in \{0, ..., N-1\}

12:

a_x = 0.0

13:

a_{y} = 0.0

14:

15:

a_z = 0.0

for k \in \{0, ..., N-1\}

16:

dx = PX[k] - PX[j]

17:

dy = PY[k] - PY[j]

18:

dz = PZ[k] - PZ[j]

19:

d = \sqrt{dx * dx + dy * dy + dz * dz}

▷ distance between the objects

20:

w = \frac{M[k]}{d^3}

21:

a_x = a_x + w * dx

22:

▶ Acceleration caused by the interaction

a_y = a_y + w * dy

23:

a_z = a_z + w * dz

24:

VX[j] = VX[j] + a_x * dt

▶ Update speed

25:

VY[j] = VY[j] + a_y * dt

26:

VZ[j] = VZ[j] + a_z * dt

27:

for j \in \{0, ..., N-1\}

▶ Update positions

28:

PX[j] + = VX[j] * dt

29:

PY[j] + = VY[j] * dt

30:

PZ[j] + = VZ[j] * dt

31:

```

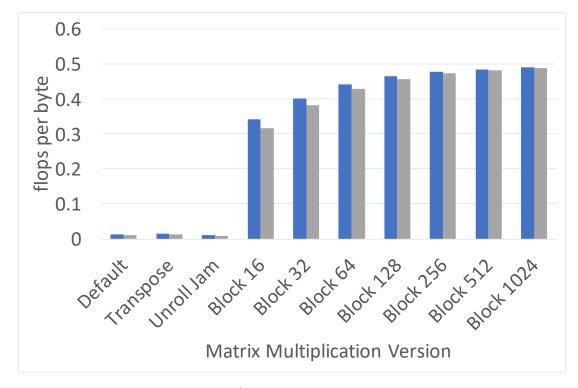

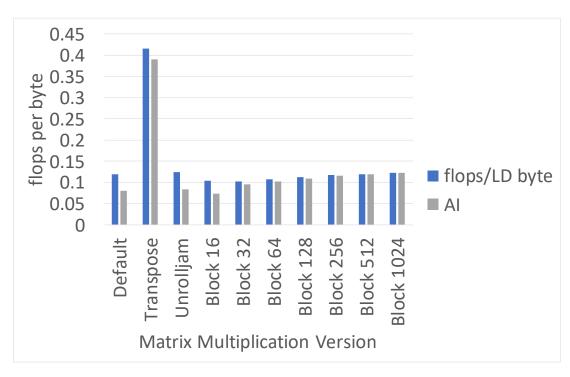

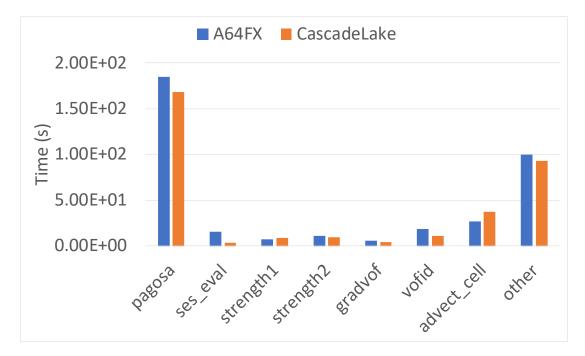

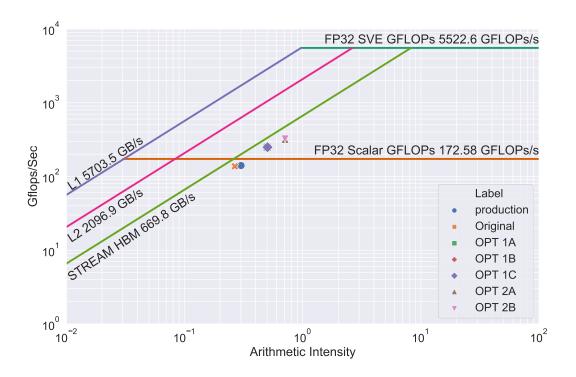

### 3.4 Summary